Fターム[5B060AC11]の内容

Fターム[5B060AC11]の下位に属するFターム

配列データ、変数データ (12)

画像データ (121)

文字パターン(フォント、キャラクタ)

ベクトルデータ (9)

文字列、ストリング (3)

タグ付データ(識別、属性) (2)

Fターム[5B060AC11]に分類される特許

1 - 20 / 74

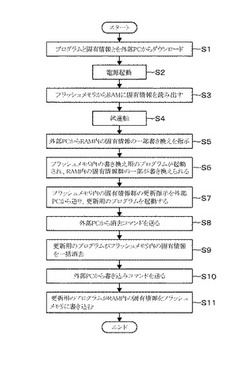

電子機器及び固有情報の管理方法。

【課題】マイクロコントローラのフラッシュメモリに記憶されたプログラムにより電子機器本体を制御する電子機器において、製造コストの低下を図りかつ固有情報の書き換えを速やかに行う。

【解決手段】フラッシュメモリ5内の固有情報領域7に外部コンピュータ4から固有情報群を事前に書き込んでおく。固有情報群は例えばシンセサイザ回路部2に使用される標準のパラメータ群及び周波数シンセサイザ1の仮番号である。マイクロコントローラ3のRAM8には、固有情報領域7と同容量の読み出し領域81が割り当てられ、電源投入時に固有情報領域7から読み出し領域81に固有情報群が読み出される。外部コンピュータ4からの指示により当該固有情報群の一部を書き換え、その後固有情報領域7内の固有情報群を一括消去した後、読み出し領域81内の固有情報群を一括して固有情報領域7に書き込む。

(もっと読む)

電子制御システム及び電子制御装置

【課題】自装置に十分な記録容量がない場合、又は記録装置が故障している場合であっても、自他装置の記録しておくべきデータを損失することなく記録することができる電子制御システム及び電子制御装置(ECU)を提供する。

【解決手段】データを記録する記録手段及び通信手段を有し、制御対象物の動作を制御する複数の電子制御装置を、通信線を介してデータ通信することが可能に接続してある。一の電子制御装置は、記録手段に所定のデータを記録することが可能であるか否かを判断し、可能であると判断した場合、記録手段にデータを記録する。可能ではないと判断した場合、他の電子制御装置へデータを送信する。他の電子制御装置は、受信したデータを記録手段に記録する。

(もっと読む)

制御装置及び方法

【課題】1つのプログラムから生成される複数のスレッド間の実行時間の不均衡を抑制する。

【解決手段】記憶装置300において電力制御が行われる単位のメモリブロック毎に省電力状態への遷移が禁止されているか否かを表すデータを格納する第1のデータ格納部220と、あるプログラムのスレッド毎に、省電力状態にあるメモリブロックへのアクセスが要求された回数を格納する第2のデータ格納部230と、演算処理装置100から受信したメモリ要求のアクセス先を含むメモリブロックが省電力状態となっている場合には第2のデータ格納部においてメモリ要求の要求元スレッドについての回数を増加させ、増加後の回数が所定の閾値を超えた場合には第1のデータ格納部においてメモリ要求のアクセス先を含むメモリブロックについて省電力状態への遷移が禁止されていることを表すデータを設定する制御部とを有する。

(もっと読む)

フラッシュメディアコントローラの内部のメタデータハンドリング

【課題】フラッシュメディアコントローラの内部のメタデータをハンドリングするための方法及び/又は装置を提供する。

【解決手段】メタデータをハンドリングする方法は、フラッシュメディアコントローラの内部のフラッシュメモリのページに格納される。方法は、一般に、(i)ページベースごとにコンテキストが定義されるコンテキストベースごとにメタデータを定義し、(ii)メタデータのサイズが定義済みの閾値以下であるとき、コンテキストの構造の内部に完了したメタデータを格納し(608)、及び(iii)メタデータのサイズが定義済みの閾値より大きいとき、コンテキストの内部にメタデータポインタを定義すること(610)を含む。

(もっと読む)

メモリの不揮発エリアの管理方法

【課題】メモリの不揮発エリアにデータを書き込む際における未使用領域の検索回数を削減し、検索時間を短縮することができるメモリの不揮発エリアの管理方法を得る。

【解決手段】メモリの不揮発エリアの管理方法であって、データ種別毎に、メモリの不揮発エリアが複数の格納領域に分割され、各データ種別の格納領域について、格納領域に格納されるデータ一件分の領域毎に、当該領域の状態を示す管理情報が設定され、起動時に、管理情報を読み取り、データ一件分の領域の状態を判定し、最新データの書き込み位置を決定するステップと、最新データの書き込み位置をRAMに保存するステップと、を備えたものである。

(もっと読む)

半導体装置及びメモリ保護方法

【課題】情報を効果的に保護できる半導体装置を提供すること。

【解決手段】実施形態の半導体装置1は、プロセッサ10と、不揮発性半導体記憶装置22を有し、プロセッサ10に対する主記憶として機能するメモリ装置20とを備える。プロセッサ10は、複数のプログラムCD1、CD2を実行する際に、プログラムを実行するために必要な情報をプログラム毎にワークセットWS1、WS2として管理すると共に、各々のワークセットWS1、WS2に必要な情報と、その情報のメモリ装置20内におけるアドレスとの関係を保持するテーブルPT1、PT2を、ワークセットWS1、WS2毎に作成する。メモリ装置20に対するアクセスは、ワークセットWS1、WS2毎に対応するテーブルPT1、PT2を参照して実行される。

(もっと読む)

計算機、消費電力低減方法およびプログラム

【課題】メモリを省電力状態にすることによる省電力効果を最大限に得る。

【解決手段】メモリを備えた計算機であって、メモリを、当該メモリに対するアクセスが可能な通常状態と、当該メモリにおける消費電力が通常状態よりも低減され、当該メモリに対するアクセスが不可能な省電力状態とのいずれかの状態にするメモリ電源制御部と、メモリに対するメモリアクセスエラーを検出する検出部とを有し、メモリ電源制御部は、メモリが省電力状態である場合に、当該メモリに対するメモリアクセスエラーが検出部にて検出されると、当該メモリを通常状態に変更する。

(もっと読む)

SIMDプロセッサのためのメモリコントローラ

【課題】外部メモリ上のデータの並列度が低い場合であってもSIMDプロセッサによるSIMD演算の効率を向上させ、高速なデータ処理を実現する。

【解決手段】メモリコントローラ20は、DDRメモリ30におけるアドレスを格納するアドレスメモリ22と、各アドレスからデータが連続して格納される長さをそれぞれ表すバースト長を格納するバースト長メモリ23とを備える。メモリコントローラ20は、第1のグループのプロセッサエレメントと、アドレスメモリ及びバースト長メモリに格納された第1のアドレス及び対応する第1のバースト長によって特定されるDDRメモリ30の領域との間で、第1のデータを転送し、第1のデータの転送後、第2のグループのプロセッサエレメントと、アドレスメモリ及びバースト長メモリに格納された第2のアドレス及び対応する第2のバースト長によって特定されるDDRメモリ30の領域との間で、第2のデータを転送する。

(もっと読む)

演算処理装置、および記憶システム

【課題】効率的にデータ転送を高速で行なうことのできるメモリシステムを実現する。

【解決手段】互いに属性の異なる情報を格納する第1および第2のメモリ(601,602)と、これらの第1および第2のメモリの記憶情報をそれぞれキャッシュする第3および第4のメモリ(611,612)と、これらの第1および第2のメモリと第3および第4のメモリの間のデータ転送を制御するコントローラを備える。第3および第4のメモリは、しきい値電圧以外の特性を利用して情報を不揮発的に格納する。

(もっと読む)

フラッシュメモリ、メモリ制御回路、マイクロコンピュータおよびメモリ制御方法

【課題】EEPROMエミュレーション時のエミュレーション書き込み単位(データ群)を構成するデータ数が各データ群で共通(固定値)にしなくてはならなかった。

【解決手段】本発明は、第1のデータをフラッシュメモリ4に書き込むときには、第1のデータを識別するための第1の付加ビットを書き込み、第2のデータをフラッシュメモリ4に書き込むときには、第2のデータを識別するための第1の付加ビットとは異なる第2の付加ビットを書き込む、ことを特徴とする。

(もっと読む)

データベース処理装置

【課題】表データおよびインデックスデータを含むデータベースを用いた検索、集計等の処理に利用可能なメモリ領域が予め決められ、そのメモリ領域にデータベースの表データおよびインデックスデータを読み込んで処理を行う場合において、処理時間を短縮する。

【解決手段】データベースのインデックスデータおよび表データの合計のデータ量が、HSQLDBエンジン12が使用可能な仮想メモリ14上のメモリ領域142に一度に読み込み可能なデータ量を超える場合、HSQLDBエンジン12は、データベースを分割して、それぞれがインデックスデータおよび表データを含む複数の分割データベース15−1〜15−nを生成し、それぞれの分割データベース15−1〜15−nのインデックスデータおよび表データの合計のデータ量が、メモリ領域142に一度に読み込み可能なデータ量以下となるようにする。

(もっと読む)

区画管理装置、区画管理方法及びプログラム

【課題】記憶装置の容量によらず柔軟に領域を区画し管理することが可能であり、また区画にファイルを割り付けるに当たって、効率的な手法により、領域を有効活用することのできる技術を提供する。

【解決手段】記憶装置の区画のサイズを互いに異なる2のべき乗の和で表して、和を構成する各2のべき乗のサイズの領域を主区域としたとき、各主区域を2分の1ずつ順次分割したサイズの各サイズの区域に区分けし、主区域を含む各サイズの区域のそれぞれのファイルの割付状態を示す割付情報を格納する割付表を生成する。各区域の割付情報を識別する区分番号は、区画を包含する2のべき乗サイズの仮想区域に基づいて割り振る。割付表に格納された割付情報に基づいて区画を管理する。

(もっと読む)

ストレージリソースの階層化管理方法及びシステム

メモリ管理装置及び方法

【課題】プロセッサで用いられるアドレス空間を拡張する。

【解決手段】メモリ管理装置35は、プロセッサ3bのプロセッサ論理アドレス空間PLA1に含まれるメモリウィンドウMW1に配置される各データの特性に基づいて生成され、当該各データの配置領域を決定するヒントとなる配置ヒント情報38を記憶する第1の記憶部17と、各データに対する配置ヒント情報38を生成する第1の管理部15と、配置ヒント情報に基づいて、メモリウィンドウMW1からプロセッサ物理アドレス空間34に書き込まれるデータに対して、プロセッサ物理アドレス空間34の中から、書き込み領域を決定する第2の管理部15と、各データのプロセッサ論理アドレスとプロセッサ物理アドレスとを関連付けたアドレス変換情報39を、第2の記憶部17に記憶する第3の管理部15とを具備する。

(もっと読む)

リスト構造制御回路

【課題】リスト構造の挿入及び削除を行うリスト構造制御回路において、エントリ数が多くても、高速な動作を行う。

【解決手段】複数の記憶素子(52−0〜52−N−1)を、選択回路(54−1〜54−N−2,56−1〜56−N−1)を介し直列接続し、挿入又は削除の位置を指定する位置選択信号と固定値との加算及び減算の一方の演算結果で、記憶素子に、データの保持又は前段の前記記憶素子のデータでの更新を制御する更新制御回路(3)を設け、高速なリスト操作を行うハードウェアを実現する。

(もっと読む)

データ消去方法及び情報機器

【課題】携帯電話等情報機器をリユース、リサイクルする際に、当該情報機器に記録されているユーザの機密情報を高速、かつ、完全に消去し、データの漏洩を防止することができる新規なデータ消去方法の提供、及び該方法を使用する情報機器、携帯電話端末の提供。

【解決手段】ホストからNAND型フラッシュメモリデバイスへ、消去対象となるパーティション番号を指定した消去コマンドを発行し、デバイスの制御部は、パーティションテーブルに関連付けて生成されたパーティションマップを参照して、該パーティション番号で特定された消去対象領域のアドレスを解釈し、該解釈に基づき消去対象パーティションに記憶されている全データを消去する。

(もっと読む)

データマップ読み取り装置、データマップ読み取り方法

【課題】高速メモリを用いたMAP引きによる演算を高速に実行するデータマップ読み取り装置及びデータマップ読み取り方法を提供すること

【解決手段】検索用データ24を記憶する第1の記憶手段15と、第1の記憶手段15のアドレスに従い、検索用データ24を一様方向に読み出す読み出し手段23と、読み出し手段が読み出した、検索用データ24の複製を記憶する第2の記憶手段13と、第2の記憶手段13に複製された検索用データ24を被検索値xinに基づき検索する検索手段25が、検索用データを24インクリメントサーチするかデクリメントサーチするかによって、検索用データ24の複製を読み出す方向を、第1の記憶手段15のアドレスの降順方向又は昇順方向のいずれかに切り替える切り替え手段21と、を有することを特徴とするデータマップ読み取り装置100を提供する。

(もっと読む)

ノンユニフォームアクセスメモリにおけるスケーラブルなインデックス付け

多数のレコードにスケールし、高トランザクションレートを提供するインデックスを構築するための方法及び装置である。ノンユニフォームアクセスメモリデバイスが、そのメモリデバイスにとって効率的であるIO(入力/出力)トラフィックに遭遇しながら、インデックス付けアルゴリズムがそのアルゴリズムにとって自然(効率的)である方法で行うことを保証するために、新しいデータ構造及び方法が提供される。インデックス付けアルゴリズムによって見なされた論理バケットを、メモリデバイス上の物理バケットにマップする、あるデータ構造である変換テーブルが作成される。このマッピングは、ノンユニフォームアクセスSSD及びフラッシュデバイスへの書込み性能が強化されるようにするものである。バケットを集め、大きい順次書き出しとして、メモリデバイスへ順次書き出すために、もう1つのデータ構造である連想キャッシュが使用される。インデックス付けアルゴリズムによって必要とされる(レコードの)バケットでキャッシュをポピュレートするために、方法が使用される。フリー消去ブロックの生成を容易にするために、追加のバケットが、デマンド読出し中に、或いはスキャベンジング処理によって、メモリデバイスからキャッシュへ読み出されてもよい。  (もっと読む)

(もっと読む)

電源制御付きコンピュータシステム及び電源制御方法

【課題】電源制御付きコンピュータシステム及び電源制御方法を提供する。

【解決手段】本コンピュータシステムは少なくとも第1記憶部と第2記憶部とを備え、第1記憶部は基本動作時に該コンピュータシステムが必要とするシステムプログラムを記憶している。電源モジュールと該第2記憶部との間の電源路上にスイッチが配置され、該電源モジュールは該第2記憶部が動作するための電力を該スイッチを介して供給する。該第2記憶部がアイドル状態の時、該スイッチを使用して該第2記憶部への電力供給を遮断することで、該コンピュータシステムの電力消費を効果的に低減する。

(もっと読む)

メモリ管理システム、メモリ管理方法及びプログラム

【課題】主記憶装置に格納されていない仮想ブロックがアクセスされた時点において、アクセスされた仮想ブロックについては割り当てる物理ブロックを決定する処理とその物理ブロックを初期化する処理とを行い、その仮想ブロックを含む複数の仮想ブロックについては割り当てる物理ブロックを決定する処理だけを行えるようにする。

【解決手段】主記憶部31に格納されていない仮想ブロックがアクセスされると、メモリ割り当て部14は、マッピングテーブル部12を参照して上記仮想ブロックに割り当てる物理ブロックが決定されているか否かを調べ、決定されていない場合は、アクセス対象の仮想ブロックを含む複数の仮想ブロックについて、その仮想ブロックに割り当てる物理ブロックを決定し、その情報をマッピングテーブル部12に登録する。そして、物理ブロックの初期化処理は、アクセス対象の仮想ブロックに割り当てた物理ブロックについてのみ行なう。

(もっと読む)

1 - 20 / 74

[ Back to top ]