Fターム[5B060CB01]の内容

Fターム[5B060CB01]に分類される特許

61 - 80 / 270

データ転送装置およびデータ転送方法

【課題】 入出力データの幅の異なる2つの機能ブロックの通信を可能にする。

【解決手段】 第1周期の第1クロック、第1周期の2倍の第2周期の第2クロックが生成される。第2クロックのハイ、ローの期間の各後半の間のみそれぞれハイを維持する第3、第4クロックが生成される。第1バッファ12は、第1ビット幅でデータを出力する。第1ラッチ71は、第1バッファから第1ビット幅でデータを受け取り、第2周期の第2クロックに合わせて第1ビット幅でデータを出力する。第2ラッチ72は、第1ビット幅で第1ラッチからデータを受け取り、保持している第1データの前半部を第3クロックの立ち上がり時に第1ビット幅の半分の第2ビット幅のデータを出力し、第1データの後半部を第4クロックの立ち上がり時に出力する。第2バッファ21は、第2ビット幅のデータを第2ラッチから受け取る。

(もっと読む)

データをセクタ単位にランダムに入出力することができるフラッシュメモリシステム

【課題】セクタ単位にランダムデータ入出力が可能なフラッシュメモリシステムを提供する。

【解決手段】本発明に従うフラッシュメモリ(セルアレイ)と、バッファメモリと、ランダムデータ入出力回路と、そして制御回路と、を備える。ランダムデータ入出力回路は、バッファメモリからセクタ単位にデータを入力されるか、或いはバッファメモリにセクタ単位にデータを出力する。制御回路は、バッファメモリとランダムデータ入出力回路との間に入出力されるデータの順序と回数とをセクタ単位に調整する。これにより、小ブロックフラッシュメモリの制御方式を用いて大ブロックフラッシュメモリを使用することができてデータ貯蔵効率を高めることができる。

(もっと読む)

不揮発性記憶装置および不揮発性メモリコントローラ

【課題】書き込み単位の大きな不揮発性メモリを制御するために容量の大きなバッファメモリを搭載した不揮発性記憶装置において、短時間での読み出しデータの出力を実現する。

【解決手段】データを一時的に格納するためにバッファメモリを、外部装置とのデータの転送単位にあわせた第1のバッファメモリと、不揮発性メモリの書き込み単位にあわせた第2のバッファメモリの2段階で構成する。外部からのデータは、第1のバッファメモリと第2のバッファメモリを経由して不揮発性メモリとの間を転送する。第1のバッファメモリは外部装置から印加されるクロックと不揮発性記憶装置内部のクロックとを切り替えて動作する。第2のバッファメモリは不揮発性記憶装置内部のクロックで動作する。

(もっと読む)

素材サーバおよび素材蓄積方法

【課題】 NAND型半導体メモリから素材をより高速に読み出すことができる素材サーバおよび素材蓄積方法を提供することを目的とする。

【解決手段】 映像データおよび音声データの少なくとも一方を含む素材を蓄積するNAND型半導体メモリを有する素材サーバ10で、入力される素材の識別情報を識別し、識別された素材の識別情報に応じて、入力された素材を蓄積するブロックを割り当てし、入力された素材毎に素材をバッファリングする複数のバッファ13にバッファリングされる容量を監視し、1ページ分の容量がバッファリングされたことが検出されると、割り当てされたブロックに対して、バッファリングされている素材をページ単位で書き込む。

(もっと読む)

ハイブリッドデータ、コード及びキャッシュ保存のためのNANDベースNOR及びNANDフラッシュ及びSRAM具備のワンチップ統合メモリシステム

【課題】ハイブリッドデータ、コード及びキャッシュ保存のためのNANDベースNOR 及びNANDフラッシュ及びSRAM具備のワンチップ統合メモリシステムの提供。

【解決手段】NANDフラッシュメモリ、NOR フラッシュメモリ及びSRAMを包含し、シングルチップ上に製造されるメモリである。NAND及びNOR メモリのいずれも同じNAND製造プロセスで製造される。これら三つのメモリは該シングルチップの同じアドレスバス、データバス、及びピンを共用する。該アドレスバスはコード、データ及びアドレスの双方向の受け取りと出力に供される。該データバスも双方向のデータの受け取り及び伝送に供される。一つの外部チップイネーブルピン及び一つの外部出力イネーブルピンがこれら三つのメモリに共用されることでシングルチップに必要なピン数を減らす。NAND及びNOR メモリはいずれもデュアル読み出しページバッファとデュアル書き込みページバッファを有し、ロード中読み出しとプログラム中書き込みの動作を行ない、これにより読み出しと書き込み動作を加速する。メモリマップ法が異なるメモリ、状態レジスタ、及びデュアル読み出しページバッファ又はデュアル書き込みページバッファの選択のために使用される。

(もっと読む)

データ転送回路

【構成】F/F回路22〜36および分配器38〜52は、入力端子20によって取り込まれたデータA〜Pのうち先行する8ワードのデータA〜Hの各々を16ビットの部分データA1〜H2に分割する。一方、SRAM54は、入力端子20によって取り込まれたデータA〜Pのうち後続する8ワードのデータI〜Pを一時的に保持する。分配器58は、SRAM54から読み出された8ワードのデータI〜Pの各々を16ビットの部分データI1〜P2に分割する。セレクタ78は、こうして生成された部分データA1〜P2を時分割態様でSDRAMに向けて出力する。

【効果】回路規模を抑えつつ、入力データのビット幅よりも小さいビット幅を有するSDRAMに対して入力データを転送することができる。

(もっと読む)

メモリシステムおよびメモリシステムの管理方法

【課題】上書き不可能な不揮発性メモリにおけるブロック移動を伴うデータ書き込み処理の効率化、高速化をなし得るメモリシステムを提供すること。

【解決手段】同一論理ブロックが第1および第2のメモリの各1つの物理ブロックと対応付けられるように論理ブロックと第1および第2のメモリの物理ブロックとの対応を管理し、同一論理ブロックで対応付けられた物理ブロック間ではデータが記憶されるページが重複しないように同一論理ブロックに含まれるページのデータを記憶し、第1のメモリに対して行う処理と、第2のメモリに対して行う処理とを並行に実行する。

(もっと読む)

情報処理システム及びデータ転送方法

【課題】初期アクセスレイテンシによるデータ処理速度の低下を低減するとともに無駄なメモリアクセスの発生しない情報処理システムを提供する。

【解決手段】情報処理システムは、連続する複数回のデータ読み出し命令を出力する際に転送状態信号を合わせて出力し、ある1つのデータ読み出し命令に対して少なくとも1つのデータ読み出し命令が後続することを転送状態信号により示すマスタモジュールと、上記ある1つのデータ読み出し命令と転送状態信号とをマスタモジュールから受信すると、転送状態信号に応答して、上記ある1つのデータ読み出し命令に後続する少なくとも1つのデータ読み出し命令に対応するデータをメモリから読み出して保持するとともに、上記ある1つのデータ読み出し命令に対応するデータをマスタモジュールに供給するメモリコントローラを含むことを特徴とする。

(もっと読む)

メモリコントローラ、システムおよび半導体メモリのアクセス制御方法

【課題】 半導体メモリのアクセス効率を向上し、システムの性能を向上する。

【解決手段】 並べ替え判定部は、半導体メモリのアクセス単位である少なくとも1つのメモリブロックをラップアクセスするためのアクセス要求アドレスが、メモリブロックの先頭アドレスと異なるときに並べ替え信号を活性化する。アドレス変換部は、並べ替え信号が活性化されたときに、メモリブロックの先頭アドレスをアクセス開始アドレスに設定する。リードデータ並び替え部は、並べ替え信号が活性化されたときに、アクセス開始アドレスに応じて半導体メモリから順次に読み出されるリードデータを、アクセス要求アドレスに対応するリードデータを先頭にして並び替える。バス出力部は、並び替えられたリードデータを外部リードバスに出力する。この結果、半導体メモリのアクセス効率を向上でき、システムの性能を向上できる。

(もっと読む)

オーディオデータ転送装置、転送方法およびオーディオデータ処理システム

【課題】演算装置よって処理されるマルチチャネルのオーディオデータが格納されている外部メモリと演算装置との間にキャッシュメモリシステムを配置する場合、キャッシュメモリと外部メモリとの間のデータ転送効率の悪化を抑制する。

【解決手段】オーディオデータ転送装置40は、バッファメモリ45及び先読み部44を有する。先読み部44は、外部メモリ1に格納されているn個のチャネル(ただし、nは2以上の整数)のオーディオデータのうち少なくとも一部をバッファメモリ45へ転送する処理を制御する。さらに、先読み部44は、n個のチャネルのオーディオデータのうち演算装置30によって処理されるm個のチャネル(ただし、mは1以上、n以下の整数)に応じて、m個のチャネルのオーディオデータを外部メモリ1とバッファメモリ45の間で転送する際のデータ転送サイズを調整する。

(もっと読む)

メモリデバイスおよびメモリデバイス制御装置

【課題】従来のインタフェースの機器との接続互換性を保ちつつ、データ転送速度を向上できるメモリデバイスおよびメモリデバイス制御装置を提供する。

【解決手段】メモリデバイス103とホスト装置101の間に介在するメモリデバイス制御装置102は、クロック信号に同期してメモリデバイスとの間でデータを転送するデータ転送手段123を備える。データ転送手段123は、クロック信号の立ち上がりエッジ及び立下りエッジの一方に同期してデータを転送するシングルエッジ同期モード、または、立ち上がりエッジと立下りエッジとの双方に同期してデータを転送するダブルエッジ同期モードに対応する。メモリデバイス103がバスマスタとして動作してデータ転送を行う際、データ転送手段123はメモリデバイスに対してダブルエッジ同期モードでデータ転送を行う。

(もっと読む)

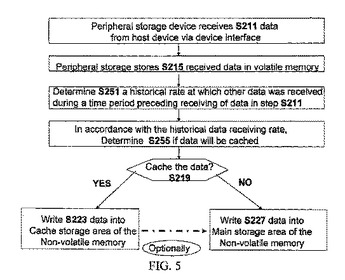

不揮発性メモリに対するキャッシングポリシーを実施する方法および装置

本開示は、ホストデバイスに動作可能に接続される周辺不揮発性記憶デバイスでキャッシングポリシーおよび/またはキャッシュフラッシングポリシーを実施する方法、デバイスおよびコンピュータ可読媒体に関する。一部の実施形態では、ホストデバイスから周辺記憶デバイスによって他のデータが受信された過去の速度、および/または受信された連続するホスト書き込み要求間の過去の平均時間間隔、および/またはデータが不揮発性メモリに書き込まれるべき評価された速度、および/またはホストが記憶レディ/ビジーフラグを読み出したことが周辺不揮発性メモリデバイスによって検出されることに従って周辺不揮発性記憶デバイス内の不揮発性メモリのキャッシュ領域にデータが記憶される。一部の実施形態では、過去の速度および/または過去の平均時間間隔に従って不揮発性メモリのキャッシュ記憶領域から主記憶領域にデータがコピーされる。  (もっと読む)

(もっと読む)

ストレージ装置および記録方法

【課題】ガベージコレクションを行わないで、データを書き込むときのIOPS性能を向上させること。

【解決手段】ホストからの第1データを、記録媒体を構成するブロックBlock1〜3のうちBlock3のページに書き込むステップと、不使用ページに基づいて選択されたBlock1のページに記録された第2データをバッファに書き込むステップと、Block1のページに記録されたデータを消去するステップと、その第2データをBlock1のページに再度書き込むステップとを備えている。このとき、その不使用ページは、データが書き込まれていないページ、または、他のページに書き込まれたデータが書き込まれているページを示している。このような記録方法によれば、ガベージコレクションを行わないで、ブロックに記録されたデータを消去する回数を低減することができる。

(もっと読む)

ページ−ディファレンシャルを使用して、DBMSに独立的な方法でフラッシュメモリーにデータを格納する方法

【課題】フラッシュ式格納システムにてページディファレンシャルロギングと呼ばれる効率的なデータ格納方法を提案する。

【解決手段】ページディファレンシャルロギングでは、フラッシュメモリー内のオリジナルページとメモリー内の最新ページとの差異であるディファレンシャルのみが記録される。ディファレンシャルは、ページがメモリー上で更新される度に計算されて記録されるのではなく、更新ページをフラッシュメモリーに反映する必要がある時にのみ計算されて記録される。このため、データの変更部分と非変更部分を含むページ全体を記録する既存のページ方式や、ページ内の変更事項の記録をすべて維持する既存のログ方式と異なる。フラッシュメモリードライバーを変更して既存のディスク式DBMSをフラッシュ式DBMSとして再使用できるのでDBMSに独立的な方法であり、書き込み演算の回数を減らしてフラッシュメモリーの寿命を伸ばす。

(もっと読む)

SSDコントローラおよびSSDコントローラの動作方法

【課題】ソリッドステートドライブ(SSD)に含まれるDRAMバッファの管理において、SSDに含まれた複数のメモリによる複数のポインタのうち代表ポインタを選定して代表ポインタに対するアクセスのみを管理することによって、ポインタ管理の複雑性を減らすこと。

【解決手段】SSDコントローラが開示される。当該SSDコントローラは、ホストからデータの読み出し命令が送信される場合に、少なくとも1つのメモリによってデータがバッファに記録完了する時点をチェックして少なくとも1つの第1ポインタのうち代表ポインタを選定し、前記代表ポインタに基づいて第2ポインタを参照して前記バッファから前記データを読み出してホストに送信する。

(もっと読む)

アクセス制御装置、情報処理装置、アクセス制御プログラム及びアクセス制御方法

【課題】記憶装置の良好ブロックをより有効に利用すること。

【解決手段】記憶領域を複数のメモリブロックに区切られたフラッシュメモリ14に対して、所定のメモリブロック群ごとにデータの書き込みを行うアクセス制御装置であって、メモリブロックごとに、当該メモリブロックが、データの記録が可能な良好ブロックであるか或いはデータの記録が不可能な不良ブロックであるかを示す記録可否情報を記憶し、この記録可否情報に基づき、当該メモリブロック群の良好ブロックに対してのみデータを書き込む。

(もっと読む)

メモリ装置

【課題】数十年以上の単位で記録データを長期的に安定に保存でき、しかも保存データを確実に読み出し可能なメモリ装置を提供する。

【解決手段】第1回路200は、データ記録回路210と、第2回路300からの読み出しまたは書き込み指示を受けて、アドレス信号に応じてデータ記録回路に対するデータの書き込みおよび読み出し制御を行う書き込み読み出し制御回路230と、を含み、第2回路300は、第1回路とのデータ転送制御を行うデータ転送制御回路310と、データ転送制御回路の作業用メモリ320と、を含み、データ転送制御回路310は、第1回路200のデータ記録回路210への書き込みデータを、いったん作業用メモリ320に蓄積し、蓄積したデータを順次に第1回路側の書き込み読み出し制御回路230に転送する。

(もっと読む)

マイクロプロセッサ

【課題】面積オーバヘッドや消費電力を低く抑えたマイクロプロセッサを提供する。

【解決手段】本発明は、データ配列単位での順次処理が可能なマイクロプロセッサであって、フェッチされた命令がデータのロード命令である場合に、指定されたデータを含んだデータ列をメモリ幅単位でデータメモリ16からロードし、また、命令の解析結果に基づいて、ロードしたデータ列のうち、次回のロード命令で指定される予定のデータを特定するロードストアユニット14と、ロードストアユニット14により特定されたデータを記憶するデータ一時記憶部17と、を備える。

(もっと読む)

データ処理装置

【課題】バッファSRAMの個数を減らしてチップ面積を削減することが可能なデータ処理装置を提供すること。

【解決手段】データ処理装置1は、SDRAM5の領域のいずれをIP(2−1〜2−m,3−1〜3−n)のそれぞれに割付けるかを示す情報を保持するSDRAMアドレス割付けレジスタ18と、バッファSRAM12および15の領域のいずれをIP(2−1〜2−m,3−1〜3−n)のそれぞれに割付けるかを示す情報を保持するバッファSRAMアドレス割付けレジスタ17とを含む。バスI/F16は、SDRAMアドレス割付けレジスタ18およびバッファSRAMアドレス割付けレジスタ17を参照してSDRAM5から読み出したデータをバッファSRAM15に格納する。したがって、IP毎にバッファSRAMを持たせる必要がなくなり、少数のバッファSRAMに統合することが可能となる。

(もっと読む)

バス装置

【課題】データの並べ替えによるバス転送の効率向上を実現することのできるバス装置を得る。

【解決手段】インオーダ対応バスマスタ2−1からの転送データにIDを付加し、IDをIDキュー部7で保持する。転送制御部8は、IDキュー部7のIDとバススレーブ3−1、3−2からの転送データのIDが一致した場合はあて先のバスマスタに転送する。一致しない場合は後で転送するとしてトランザクションキュー部9に蓄積する。トランザクションキュー部9の転送データのIDとIDキュー部7のIDが一致した場合、転送制御部8はその転送データをあて先のバスマスタに転送する。

(もっと読む)

61 - 80 / 270

[ Back to top ]