Fターム[5B060CB01]の内容

Fターム[5B060CB01]に分類される特許

161 - 180 / 270

外部記憶装置およびそのメモリアクセス制御方法

【課題】セクタデータを連続してアクセスする外部記憶装置において、単一のエラー訂正手段によりエラー検出・訂正を行いながらメモリアクセスを高速化する。

【解決手段】ホスト2がライトするセクタデータは一時ライトバッファ7に格納される。

マイクロプロセッサ8は、ライトバッファに格納されたセクタデータが奇数番目のセクタデータの場合には第1のメモリ4に、偶数番目のセクタデータの場合には第2のメモリ5に格納する。ホスト2がセクタデータをリードするときには、データ切換手段11において、第1のメモリから読み出したN番目のセクタデータをシステムバスに対し出力すると同時に、第2のメモリから読み出したN+1番目のセクタデータ(ホストコンピュータが次にリードするセクタデータ)をエラー訂正手段に対し出力する。これにより、N+1番目のセクタデータに対するエラー検出およびエラー訂正に要する時間を見かけ上短縮する。

(もっと読む)

共有メモリインターフェイス

【課題】複数個のプロセッサがそれぞれ管理するバスから共有メモリをアクセスする際における、各バスでの待ち状態の発生を抑制する。

【解決手段】メインバスB1はメインプロセッサ1が管理し、内部バスB2はコプロセッサ2が管理する。メインバスB1および内部バスB2とシングルポートの共有メモリ3との間に共有メモリインターフェイス4が介在する。共有メモリインターフェイス4は、メインバスB1と共有メモリ3との間に介在するバッファメモリ13を備える。調停制御部14は、共有メモリ3からの読出時には共有メモリからバッファメモリ13に転送したデータをバッファメモリ13からメインバスB1に読み出させる。また、調停制御部14は、共有メモリ13への書込時にはメインバスB1からバッファメモリ13にデータを転送しバッファメモリ13のデータを共有メモリに書き込ませる。

(もっと読む)

メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】フラッシュメモリの1ページの容量が増加しても、処理時間とバッファの容量を増加させることなく、バッファを介した記憶データの移動処理を行うこと。

【解決手段】同じ物理ゾーンに属する物理ブロック間で記憶データを移動させるときに

、物理ゾーンに構成する第1の物理ブロックを含む第1のフラッシュメモリ内のデータレジスタからデータを読み出し、読み出されたデータをデータ蓄積手段に蓄積し、蓄積したデータを、第1の物理ブロックと同一の物理ゾーンに属する第2物理ブロックを含む第2のフラッシュメモリ内のデータレジスタに転送する。この処理で、第1のフラッシュメモリ内のデータレジスタからのデータの読み出しと、第2のフラッシュメモリ内のデータレジスタへのデータの転送を、交互に又は並行して行うことにより、データ蓄積手段に1ページ分のデータを蓄積せずに、第1の物理ブロックから第1の物理ブロックと異なるフラッシュメモリ内の物理ブロックである第2の物理ブロックにデータを移動させる。

(もっと読む)

メモリシステム

【課題】フラッシュメモリチップを多く搭載することなく書き込み速度を高速化することができるメモリシステムを提供する。

【解決手段】メモリシステムは、夫々独立にメモリ動作可能な複数のメモリバンク(BNK1,BNK2)を有する複数の不揮発性メモリチップ(CHP1,CHP2)と、前記不揮発性メモリチップに対して個別にアクセス制御可能なメモリコントローラ(5)とを含む。前記メモリコントローラは前記不揮発性メモリチップの複数のメモリバンクに対する同時書き込み動作又はインタリーブ書き込み動作を選択的に指示することが可能である。前記同時書き込み指示は、メモリバンクを指定した書き込み動作の直列的な複数の指示の後に複数のメモリバンクに対して同じタイミングで書き込み動作を開始させる書き込み動作指示である。

(もっと読む)

NAND型フラッシュメモリデバイス及びこれを利用したコンピューティングシステムの起動方法

【課題】組み込み系コンピューティングシステムを構築するための、より改良されたNAND型フラッシュメモリデバイスの提供。及び該デバイスを用いたコンピューティングシステムの起動方法の提供。

【解決手段】NAND型フラッシュメモリからのブートローダの読み出しを、NAND型フラッシュメモリデバイスの内部機能により自律的に実行し、読み出したブートローダを、ホストCPUの内部メモリバスと直結するデバイス内のSRAMにロードする。ホストは、SRAMにロードされたブートローダの情報に基づきUSBインターフェースからOSをシステムメモリにロードし、システムを起動する。

(もっと読む)

メモリ制御回路及びメモリ制御方法

【課題】メモリチップ、メモリモジュールの書き込み、読み出し時のデータ切り替えに伴うノイズを削減できるようにすることを目的としている。

【解決手段】複数個のバーストから成るライトデータをメモリに書き込む際に、前記バーストの順番を並べ替えてn種類のライトデータを生成するとともに、前記n種類のライトデータの中から、メモリに書き込む際のデータ切り替え回数が前記バーストの順番を並べ替える前よりも少ないライトデータを選択し、更に選択されたライトデータのバースト並び順を冗長ビットにエンコードするようにして、前記選択されたライトデータと、前記エンコードされた冗長ビットとを前記メモリに書き込むようにすることにより、メモリリード、ライト時のデータ切り替え回数をできる限り低減できるようにする。

(もっと読む)

メモリシステム

【課題】安価なNAND型フラッシュメモリを使用しつつも、読み出し命令に対するレイテンシをNOR型フラッシュメモリと同程度に抑制することが可能なメモリシステムを得る。

【解決手段】メモリモジュール1のPOR時に、ページP1〜Pnの第1部分P1a〜PnaがNAND型フラッシュメモリ3から読み出され、エラー訂正部7によって所定のエラー訂正処理が行われた後、バッファメモリ6に書き込まれる。コントローラ2がホストシステム8からページの読み出し命令を受けると、制御部4は、NAND型フラッシュメモリ3の比較的大きいレイテンシに起因してNAND型フラッシュメモリ3が待機状態となっている間に、バッファメモリ6からページP1〜Pnの第1部分P1a〜Pnaを読み出して、ホストシステム8へデータ転送する。

(もっと読む)

フラッシュメモリシステム及びそのプログラム方法

【課題】 フラッシュメモリシステム及びそのプログラム方法を提供する。

【解決手段】 ホストから伝送される保存データを一時保存する複数のバッファを備えるバッファ部と、複数のメモリセルアレイを備える少なくとも一つのフラッシュメモリチップを備える複数のチャンネル部と、バッファ部に保存されたデータが複数のチャンネル部に順次に伝送されるように制御し、伝送された保存データがチャンネル部に備えられたフラッシュメモリチップのメモリセルアレイに記録されるように制御する制御部と、を備えることを特徴とするフラッシュメモリシステムである。これにより、複数のバッファを利用して各チャンネル部にデータを順次に伝送すると同時に、ホストから伝送されるデータを保存することによって全体帯域幅を増大させ、かつデータの記録速度を向上させうる。

(もっと読む)

データ記憶装置、メモリ管理方法、及びプログラム

【課題】高速にデータを検索することが可能な、データ記憶装置、メモリ管理方法、及びプログラムを提供すること。

【解決手段】メモリ領域が物理的に分割され、分割された各メモリ領域内に書き換え用のバッファ領域が設けられた不揮発性メモリ112と、分割された各メモリ領域内に設けられた書換え用のバッファ領域を利用して、分割された各メモリ領域に記録されたデータを更新するメモリ管理部106と、を備えることを特徴とする、データ記憶装置が提供される。かかる構成により、所定のメモリ領域に属するデータを検索する範囲を該当するメモリ領域内に限定することが可能になり、所望のデータに対するアクセスが高速化する。

(もっと読む)

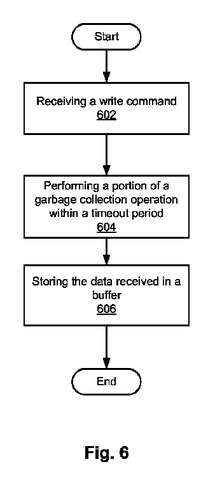

段階的ガーベッジコレクション

不揮発性メモリ記憶システムを動作させる方法が提供される。この方法では、データを書き込む書き込みコマンドが受け取られる。書き込みコマンドは、書き込みコマンドの実行を完了させるためのタイムアウト期間を割り当てられる。タイムアウト期間内に、ガーベッジコレクション動作の一部分が実行される。書き込みコマンドに関連付けられたデータは、不揮発性メモリ記憶システムに関連付けられたバッファに書き込まれる。  (もっと読む)

(もっと読む)

不揮発性記憶装置、データ記憶システム、およびデータ記憶方法

【課題】データを高速に書き込める不揮発性記憶装置を提供する。

【解決手段】不揮発性メモリ130には、データが単位領域毎に書き込まれるようになっている。CPU部121は、アクセス装置110から入力されるデータを保持する第1の記憶部122に保持された1つの単位領域分のデータ毎に上記不揮発性メモリに書き込む一方、上記第1の記憶部に保持されている上記単位領域分に満たないデータを第2の記憶部に保持させ、第2の記憶部に保持されたデータも、1つの単位領域分のデータ毎に上記不揮発性メモリに書き込む。

(もっと読む)

不揮発性メモリシステム、及びそのデータ読み出し/書き込み制御方法

不揮発性メモリシステムは、複数のデータ領域を有する不揮発性メモリと、前記不揮発性メモリの読み出し及び書き込みを制御するメモリコントローラとを備え、前記メモリコントローラは、ホストデバイスから供給されるコマンドとセクタカウント数及びセクタアドレスとに従って前記不揮発性メモリの選択されたデータ領域の複数セクタの読み出し/書き込みを連続的に実行する。 (もっと読む)

不揮発性記憶装置、不揮発性記憶装置の書込み方法およびコントローラ

【課題】メモリーカードにおいて、書込み単位の大きなフラッシュメモリを用いた場合に、書込み時間に占めるデータ転送の時間の割合が大きくなり、書込み性能が低下する。

【解決手段】ホスト102からの第一の書込みデータをバッファメモリAに保管し、次にホスト102からの第二の書込みデータをバッファメモリBに保管するとともにバッファメモリAに保管された第一の書込みデータをフラッシュメモリ103に転送する。次に、バッファメモリBに保管された第二の書込みデータをフラッシュメモリ103に転送する。そして、第一と第二の書込みデータを同時にフラッシュメモリ103に書き込む。これにより、バッファメモリ105への入出力転送を同時に行えるので書込みが高速化する。

(もっと読む)

演算処理システム

【課題】プロセッサの負荷を増加させることなく、アクセスに所定のルーチンを必要とするフラッシュメモリ等のメモリからの、読み出しにおける待ち時間を短縮する演算処理システムを提供することを目的とする。

【解決手段】演算処理システムであって、プロセッサと、前記プロセッサによるアクセスの対象であるデータを格納する第1のメモリと、転送されたデータを格納するための領域を有する第2のメモリと、前記プロセッサによるアクセスに従って、データを前記第1のメモリから前記第2のメモリの前記領域に転送させ、前記領域に格納されているデータを示す領域情報を記憶するデータ管理部とを備え、前記データ管理部は、前記プロセッサによるアクセスの対象が前記領域情報に示されているデータである場合は、前記プロセッサを前記第2のメモリにアクセスさせるものである。

(もっと読む)

メモリシステム

【課題】データの書き込み速度を向上出来るメモリシステムを提供すること。

【解決手段】ページ単位でデータを一括して書き込み、前記ページを複数含み且つ各々がデータの消去単位となる複数のメモリブロックBLKを備えた不揮発性半導体メモリ11と、前記不揮発性メモリ11に対して書き込みデータ及び第1ロウアドレスを転送し、且つ転送した前記第1ロウアドレスの変更命令と、該第1ロウアドレスとは異なる第2ロウアドレスとを発行するコントローラ12とを具備し、前記不揮発性半導体メモリ11は、前記変更命令が発行されない際には前記第1ロウアドレスに対応する前記ページに前記書き込みデータを書き込み、前記変更命令が発行された際には前記第2ロウアドレスに対応する前記ページに前記書き込みデータを書き込む。

(もっと読む)

半導体システムの製造方法

【課題】フラッシュメモリを内蔵した使い勝手の良好なマイクロコンピュータを搭載した半導体システムの製造方法を提供する。

【解決手段】CPUとI/Oポートとフラッシュメモリとランダムアクセスメモリとを1つの半導体基板上に有し、該フラッシュメモリには書き換え制御プログラムと転送制御プログラムとか格納され、CPUが書き換え制御プログラムを実行することによりI/Oポートから入力された情報を該フラッシュメモリの所定の領域に書込可能な樹脂封止型半導体装置を準備する工程と、当該半導体装置をプリント基板に実装する工程と、実装工程の後、CPUは前記転送制御プログラムを実行することにより書き換え制御プログラムをランダムアクセスメモリに転送し、転送された書き換え制御プログラムをCPUが実行することにより、I/Oポートから入力された情報を前記フラッシュメモリの所定の記憶領域に書き込む工程を含む。

(もっと読む)

不揮発性メモリ

【課題】コントローラの処理の負荷やフラッシュメモリとコントローラ間のやり取りを低減でき、コントローラの簡略化や性能の向上を実現でき、さらに、今まで得なし得なかった新しい機能を実現することが可能な不揮発性メモリを提供する。

【解決手段】データ部と特定フィールドを含むデータをアクセス単位としてアクセスされるメモリセルアレイ111と、メモリセルアレイ11から読み出したアクセス単位のデータまたはメモリセルアレイ111に書き込むべきアクセス単位のデータを保持するバッファ113と、指定されたアドレス、コマンド、並びに、バッファ113に保持されたデータのうちの特定フィールドのデータに応じてメモリセルアレイ111のアクセス制御を行う制御回路112とを有する。

(もっと読む)

画像処理装置及びプログラム

【課題】パイプライン形態等で連結された画像処理モジュールに対応する複数のスレッドを並列に実行させて画像処理を行う構成において、記憶リソースが一時的に不足しても画像処理全体を継続させることを可能とする。

【解決手段】各モジュールに対応するスレッドからメモリ取得が要求される毎に、要求されたメモリ領域が確保可能か判定し、確保可能であればメモリ領域を割り当て、確保可能でなければ要求元スレッドの動作を停止させ、待ち行列に取得要求情報を登録する(スレッドの実行優先度順)。任意のスレッドからメモリ解放が要求されると、要求されたメモリ領域を解放し(620)、待ち行列中の取得要求情報が要求するメモリ領域を確保可能か判定し (624,626)、確保可能であれば待ち行列から取得要求情報を取り出し、スレッドの動作停止状態を解除し、メモリ領域を割り当てる(628,630)ことを、待ち行列の先頭に登録された取得要求情報から順に行う。

(もっと読む)

記憶装置

【課題】情報端末からのフラッシュメモリとICカードへの並列アクセスを行うことができ、また、フラッシュメモリから情報端末とICカードへのデータ転送を並列に行うことができる記憶装置を提供する。

【解決手段】記憶装置において、フラッシュメモリデバイス130へのアクセスに用いられるフラッシュメモリバッファと、ICカードデバイス180へのアクセスに用いられるICカードバッファを持ち、かつそれらはデータの読み出しに用いられるREADバッファとデータの書き込みに用いられるWRITEバッファに分けて管理し、記憶装置に接続された情報端末、記憶装置内部のICカード、フラッシュメモリへのアクセスを制御するアドレス制御部(160、162、164)と、それらのデータ転送時の競合を調停するアドレス制御管理部190を備えた。

(もっと読む)

データ処理装置及びメモリコントローラチップ

【課題】 FIFOを用いたメモリコントローラにより外部バスアクセスの高速化を可能としたメモリシステムを提供する。

【解決手段】 データを格納するメモリ部と、メモリ部及び外部インタフェース部に接続される共有バスと、データを制御信号に応じて格納し出力するFIFO部と、データを受ける内部バスと、共有バスとFIFO部と内部バスとに接続され、与えられる制御信号に応じて、共有バスとFIFO部とを導通させ、又は、共通バスと内部バスとを導通させるバスコントローラ部と、外部インタフェース部から与えられる操作信号に応じた制御信号を、バスコントローラ部に供給する調停部とをもつデータ処理装置。

(もっと読む)

161 - 180 / 270

[ Back to top ]