Fターム[5B060CB01]の内容

Fターム[5B060CB01]に分類される特許

81 - 100 / 270

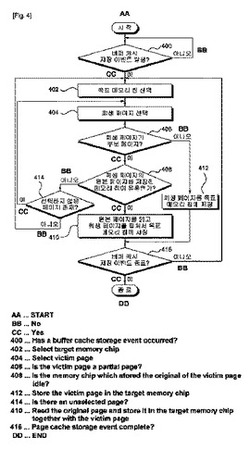

半導体ディスクシステムのバッファキャッシュプログラミング方法およびバッファキャッシュプログラミング装置

【課題】半導体ディスクシステムにおけるバッファキャッシュのプログラミング方法および装置を提案する。

【解決手段】本発明の実施形態に係る半導体ディスクシステムのバッファキャッシュプログラミング装置は、ページを格納するバッファキャッシュ部と、複数のメモリチップを備えるメモリ部と、前記複数のメモリチップのうち少なくとも1つの目標メモリチップに格納する時に発生し得る待機時間を考慮して前記ページのうち少なくとも1つのページを犠牲ページとして選択する制御部とを備える。

(もっと読む)

メモリシステム

【課題】ホストからの書き込み要求に対する応答性を全般的に向上させる。

【解決手段】WC追い出し制御部211は、WCリソース使用量を上限値Clmtより値が小さいAF(Auto Flush)閾値Cafと比較し、WCリソース使用量がAF閾値Cafを越えているときは、NANDメモリ10での整理の状態を確認し、NANDメモリ10での整理が充分に進んでいる場合には、早めにWC(ライトキャッシュ)21からNANDメモリ10にデータを追い出す。

(もっと読む)

セクタ書き込み操作時間を効果的に減少させるための不揮発性メモリユニット内のブロックの構成

【課題】セクタ書き込み操作時間を効果的に減少させるための不揮発性メモリユニット内の好適なブロックの構成を提供すること。

【解決手段】本発明の一実施形態は、ブロックに分けられた不揮発性メモリ(16)内の格納位置(232)内にセクタ情報を格納する不揮発性メモリシステムを備える。複数のブロックは、スーパーブロックを規定し、各ブロックは所定の複数のセクタを有する。不揮発性メモリシステムは、セクタ情報を、特定のスーパーブロック(204)の第1のブロック(210)と第2のブロック(216)にシフトさせ、セクタ情報を特定のスーパーブロックの第1のブロック(210)に書き込むコントローラ(14)を備える。第1のブロックへの書込み中に、第2のブロック(216)へのシフト全体が起こり、それにより、ブロックへの書込み動作を行うために必要な時間が減少し、全体的なシステム性能が上がる。

(もっと読む)

半導体記憶装置

【課題】

多値フラッシュメモリにおいては書き込み速度の向上と長寿命化が課題となっている。

【解決手段】

本発明の不揮発性メモリは、複数のブロックで構成され、ブロックはそれぞれ複数のページで構成され、ページはそれぞれ複数のセルで構成され、ページは、1つのセルに複数ビットを記録する第1のモードでライト可能であり、ページはまた、1つのセルに前記複数ビットよりも少数のビットを、第1のモードでのライトに要する時間よりも短い時間で記録する第2のモードでライト可能である。コントローラは、半導体記憶装置の外部からのデータのライト要求に応答して、第2のモードを用いてデータを第1のページに書いたのち、第1のモードを用いて第1のページ内のデータの一部を第2のページに書くことを特徴とする。

(もっと読む)

速度変換回路

【課題】シングルポートメモリを用いて、データが欠けることなく連続した書き込み及び読み取りを行う。

【解決手段】書き込み用のクロック周波数からなる第1のクロック信号に同期した書き込みデータが保持されるライトバッファ回路と、前記第1のクロック信号と、前記第1のクロック信号と独立した読み取り用のクロック周波数からなる第2のクロック信号との非同期吸収を行う非同期吸収回路と、シングルポートメモリに対する書き込み及び読み取りを制御するRAMコントローラ回路とを有し、前記非同期吸収回路は、前記ライトバッファ回路で保持された書き込みデータを、前記第2のクロック信号に対応させてデータ長を調整し、調整された書き込みデータを前記RAMコントローラ回路へ出力することにより上記課題を解決する。

(もっと読む)

トリプル・バッファリングを使用するデータを処理する方法

【課題】トリプル・バッファリングを使用する双方向データ交換を提供する。

【解決手段】本発明は、データを処理する方法に関する。処理されるデータブロックは、第1の時間間隔(t1、t2、t3、...)においてメモリエリア(A、B、C)に書き込まれる。前記データブロックは、第2の時間間隔(t2、t3、t4...)において同一のメモリエリア(A、B、C)で処理される。処理されたデータブロックは、第3の時間間隔(t3、t4、t5...)において前記同一のメモリエリア(A、B、C)から返される。

(もっと読む)

記憶装置

【課題】ホストからの恒常的な高速書き込みとフラシュメモリへの書き換え頻度の低減を可能にした記憶装置を提供する。

【解決手段】記憶装置は、記憶領域が複数からなるn個のブロックに分けられたRAMと、複数のm組に分けられたフラシュメモリと、外部からRAMに対してデータの書き込みが可能にされた第1バスと、RAMから前記m組に分けられたフラシュメモリに対してそれぞれ独立してデータの書き込みが可能にされたm個の第2バスからなる内部バスと、第1バスを用いてRAMの書き込みを行う第1動作と、第1動作のための記憶領域を確保すべく、RAMの記憶データのうち書き込み時の古い順であって、かかる記憶データのデータ量に対応して第2バスを用いて1ないしm個のブロック分のデータをフラシュメモリに対して書き込む第2動作とを時分割的に同時に行う内部コントローラ部とを有する。

(もっと読む)

フラッシュメモリのキャッシングポリシーを実施する方法および装置

1つ以上のキャッシュ管理ポリシーを実施するための方法、装置およびコンピュータ媒体を本願明細書で開示する。或る実施形態では、記憶デバイスのフラッシュメモリは複数のフラッシュメモリダイを含み、各フラッシュメモリダイはそれぞれのキャッシュ記憶領域とそれぞれの主記憶領域とを含む。外部ホストデバイスから受け取ったデータについて、受け取ったデータがどの主記憶領域に宛てられているかを判定し、これによりその受け取ったデータのためのターゲットダイとして複数のフラッシュメモリダイのうちの1つを指定する。受け取ったデータが主記憶領域に書き込まれる前にキャッシュ記憶領域に書き込まれるたびに、受け取ったデータは指定されたターゲットダイのキャッシュ記憶領域に書き込まれる。  (もっと読む)

(もっと読む)

メモリコントローラ、メモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】複数セクタの領域が含まれる論理ページ単位のデータが格納されるデータ格納領域を複数個備えたフラッシュメモリシステムにおいて、フラッシュメモリに対するデータ書込みの効率やフラッシュメモリの寿命を向上させる。

【解決手段】メモリコントローラは、論理ページ単位のデータが格納されるデータ格納領域を複数個備えたデータ格納手段を有しており、複数個のデータ格納領域のうち、ホストシステムから与えられたデータが格納されている領域のセクタ数が多いデータ格納領域を優先して、データ格納領域に格納されているデータをフラッシュメモリに書き込む。

(もっと読む)

インターフェース回路

【課題】シリアルフラッシュメモリに対するデータアクセスを可及的に高速に行うことが可能なインターフェース回路を提供する。

【解決手段】プログラムを実行するCPUコアの要求に基づいて、前記プログラムを格納するシリアルフラッシュメモリにアクセスするインターフェース回路であって、

前記CPUコアから出力されたリード信号及びアドレス信号に基づいて、前記シリアルフラッシュメモリに発行するためのリードコマンド及びアドレスセットを生成する、自動コマンド生成回路と、

前記リードコマンド及びアドレスセットを前記シリアルフラッシュメモリに発行する、制御部と、

前記リードコマンド及びアドレスセットに応じて前記シリアルフラッシュメモリから読み出されたデータを格納する、ワードレジスタと、

を備え、

前記制御部は、さらに、前記シリアルフラッシュメモリから読み出され前記ワードレジスタに格納されたデータを、前記CPUコアに出力するものとして構成されている。

(もっと読む)

メモリコントローラ、メモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】複数セクタの領域に対応する論理ページ単位のデータが格納されるデータ格納領域を複数個備えたフラッシュメモリシステムにおいて、アクセス速度を向上させることを目的とする。

【解決手段】いずれかの論理ページに対応するデータである第1のデータを、いずれかのデータ格納領域である第1のデータ格納領域に格納するのに並行して、第1のデータと同じ論理ページに対応する第2のデータがフラッシュメモリから読み出され、読み出された第2のデータが、第1のデータ格納領域とは異なるデータ格納領域である第2のデータ格納領域に格納される。そして、第1のデータ格納領域と第2のデータ格納領域との間でデータ転送を行うことにより、第2のデータの一部が第1のデータで置き換えられたデータが作成される。

(もっと読む)

メモリシステム、メモリ装置、メモリアクセス方法

【課題】メモリセルアレイがビジー状態のときでもアクセスが可能なメモリシステムを提供する。

【解決手段】メモリセルアレイ100を有する第1メモリ装置10に、第1メモリ装置10を活性化するための第1制御信号CS1、メモリセルアレイ100にアクセスするためのコマンド信号CMD、アドレス信号ADD、及びデータ信号DATを入力する。第1メモリ装置10は、メモリセルアレイ100がビジー状態であるか否かを検知する状態検知部17、ビジー状態のときにコマンド信号CMDを一時記憶する第1バッファ14、ビジー状態のときにアドレス信号ADDを一時記憶する第2バッファ15、及びビジー状態のときにデータ信号DATを一時記憶する第1バッファ16を備える。第1〜第3バッファ14〜16により、ビジー状態であっても第1メモリ装置10に必要なデータを入力可能になる。

(もっと読む)

半導体装置

【課題】データの書き込み速度を向上出来る半導体装置を提供すること。

【解決手段】2ビット以上のデータを保持可能な第1メモリブロックBLK1と、1ビットのデータを保持可能な第2メモリブロックBLK2とを有し、ページ単位でデータをプログラム可能な不揮発性半導体メモリ11と、前記不揮発性半導体メモリ11にデータのプログラムを命令するコントローラ12とを具備し、前記第1メモリブロックBLK1において前記ページは前記データのビット毎に割り当てられ、且つビット毎に書き込みに要する時間が異なり、書き込みデータの最終ページが前記書き込みに要する時間の最も長いビットに相当する場合、前記コントローラ12は前記不揮発性半導体メモリ11に対して、前記第2メモリブロックのいずれかのページにプログラムを実行するよう命令する。

(もっと読む)

フラッシュメモリ制御方法および制御装置

フラッシュメモリ制御方法および制御装置が提供される。フラッシュメモリ制御方法は、フラッシュメモリの複数のブロックに格納されたデータを同時に消去する多重ブロック消去機能が支援される環境において、前記多重ブロック消去機能を考慮して使用可能なブロックリサイクル方式それぞれの費用を算出するステップと、前記算出された費用に基づいて前記使用可能なブロックリサイクル方式のうち少なくとも1つを選択するステップと、前記使用可能なブロックリサイクル方式のうち選択された少なくとも1つを用いて少なくとも1つのブロックを管理するステップとを含む。  (もっと読む)

(もっと読む)

メモリコントローラおよび不揮発性記憶装置

【課題】小さな容量のデータ、特に読み出し・書き込み単位よりも小さな容量のデータを良好に読み出すことができるメモリコトローラを提供する。

【解決手段】ホストとのデータの入出力を制御するホストインタフェースと、前記メモリとのデータの入出力を制御するメモリインタフェースと、2以上のセクターからなるページ単位のデータを記憶可能な揮発性メモリの複数からなるバッファと、前記バッファのそれぞれの揮発性メモリを前記ホストインタフェースに接続するか、前記メモリインタフェースに接続するかを制御するバッファ制御部と、を備えたメモリコントローラであって、前記バッファ制御部は、前記メモリから揮発性メモリへの前記セクター単位のデータの転送が終了した時に、前記ホストへの読み出しデータがなければ、前記揮発性メモリの接続を前記ホストインタフェースに切り替える。

(もっと読む)

メモリ制御装置

【課題】行アドレスの変更が必要な連続した複数のデータを繰り返して読み出す場合であっても、短時間でそのデータを読出すことができるようにする。

【解決手段】繰返リード制御部5の繰返リード回数レジスタに格納された回数およびリードアドレス領域レジスタに格納されたSDRAM2のアドレスに基づいてSDRAM2に格納された連続する複数のデータを繰り返して読み出すとき、1回目にSDRAM2から読み出した連続する複数のデータをプリチャージが不要なデータバッファ4に記憶させ、2回目以降に読み出すときはそのデータバッファ4から連続する複数のデータを読み出すようにした。

(もっと読む)

パーティションフリーマルチソケットメモリシステムアーキテクチャ

【課題】アプリケーションのメモリ帯域幅を増大させる技術を提供する。

【解決手段】少なくとも2つのメモリに接続される少なくとも2つのプロセッサを有する装置であって、前記少なくとも2つのプロセッサの第1プロセッサは、前記少なくとも2つのメモリの第1メモリに格納されているデータの第1部分と、前記少なくとも2つのメモリの第2メモリに格納されているデータの第2部分とをクロック信号期間の第1部分内で読み、前記少なくとも2つのプロセッサの第2プロセッサは、前記少なくとも2つのメモリの第1メモリに格納されているデータの第3部分と、前記少なくとも2つのメモリの第2メモリに格納されているデータの第4部分とを前記クロック信号期間の第1部分内で読む。

(もっと読む)

フラッシュメモリシステムにおけるハウスキーピング操作のスケジューリング

【課題】ハウスキーピング操作は繰り返される消去および再プログラミングを通して累積する個々のブロックの損耗を均す。

【解決手段】メモリセルが同時に消去可能なセルのブロックをなすようにグループ分けされているフラッシュEEPROM(登録商標)システムのような再プログラム可能な不揮発性メモリシステムはホストコマンドの実行中にメモリシステムのハウスキーピング操作をフォアグラウンドで行うように操作され、そのハウスキーピング操作はホストコマンドの実行とは関連しない。1つ以上のそのようなハウスキーピング操作とホストコマンドの実行との両方が、その特定のコマンドを実行するために確立された時間割り当て内で行われる。1つのそのようなコマンドは、受信されたデータのメモリへの書き込みである。

(もっと読む)

制御装置

【課題】分割ブロック単位で一括消去を行ってから書込が行われる不揮発フラッシュメモリの一括書込時間を短縮する。

【解決手段】外部ツール105Aと通信を行うマイクロプロセッサ110と、マイクロプロセッサ110の入出力制御プログラムが格納される不揮発フラッシュメモリ113Aを備え、前記入出力制御プログラムは外部ツール106Aからマイクロププロセッサ110と協働するバッファメモリ112を介して所定の書込単位量毎に順次不揮発フラッシュメモリ113Aの各分割ブロックBiに対して書込まれる。各分割ブロックBiは更に、分割書込みされる第一・第二のセクタに分割され、前記バッファメモリ112は少なくとも3段(前段部112a・中段部112b・後段部112c)の先入先出デーブルを構成して、外部ツール105Aからのシリアル通信に起因する転送遅れによる書込み待ちが発生しないように構成されている。

(もっと読む)

制御回路

【課題】メモリに接続されている関連性のない複数のアクセス要因が交互にあった場合でも連続性を失うことがなくデータを読み出すことができる回路を提供する。

【解決手段】複数の要因ごとにメモリのデータを記憶するデータバッファを設け、要求されたデータがデータバッファにある場合は、データバッファに記憶されているデータを出力する。

(もっと読む)

81 - 100 / 270

[ Back to top ]