Fターム[5B060CB01]の内容

Fターム[5B060CB01]に分類される特許

21 - 40 / 270

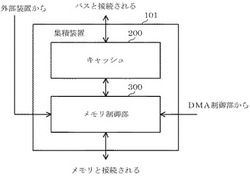

集積装置、および、制御方法

【課題】DRAMのリフレッシュ実行中に、DMAコントローラからアクセスがあった場合の性能低下を防ぐ。

【解決手段】集積装置は、セルフリフレッシュ中はDMAデータを格納するキャッシュと、DMA転送開始情報によりメモリのセルフリフレッシュ解除を行うメモリ制御部とを含む。

(もっと読む)

メモリシステム

【課題】転送効率を可及的に向上させること。

【解決手段】メモリシステムは、不揮発性のメモリセルアレイおよび読み出しバッファを備えるメモリチップと、読み出し要求されたデータを第1単位サイズ毎に前記メモリチップに出力させて、前記出力されたデータをホスト装置に逐次転送するコントローラと、を備える。前記メモリチップは、指定された第1単位サイズのデータを前記読み出しバッファを介して外部に出力する第1の読み出しコマンドと、指定されたデータを外部に出力するとともに当該指定されたデータに物理アドレスが隣接する次の第1単位サイズのデータを前記読み出しバッファに格納する第2の読み出しコマンドとをサポートし、前記コントローラは、読み出し要求に含まれるホストアドレスおよび/またはデータサイズに基づいて使用する読み出しコマンドを決定する。

(もっと読む)

メモリコントローラ、及びデータ記録装置

【課題】管理テーブルを不揮発性メモリに保存する時の応答遅延時間を縮減し、データ記録装置の電源遮断後に、不揮発性メモリに保存した情報から管理テーブルを復元する機能を備えるメモリコントローラを提供する。

【解決手段】不揮発性メモリ1011は、管理テーブル格納ブロックと、データ書き込みのために割り当てたスクラッチブロックと、データを保持するデータブロックと、データを消去した消去済みブロックを持つ。メモリ1012は、データの格納場所を管理する論理・物理アドレス変換テーブル10120と、ブロック履歴管理テーブル10125を持つ。管理テーブル格納ブロックは、論理・物理アドレス変換テーブル10120とブロック履歴管理テーブル10125を保存する管理テーブルページを持つ。メモリコントローラ1010は、論理・物理アドレス変換テーブル10120の一部を不揮発性メモリ1011の管理テーブル格納ブロックに保存する。

(もっと読む)

メモリ装置

【課題】ハードウェア構造を変化させることなく種々の送信元および送信先に対応することができる。

【解決手段】メモリ装置1は、データの送受信に用いられる装置であり、データ送信元2から出力されるデータを格納し、データの出力先であるデータ送信先3に対してデータを出力するデータバッファ4と、データ送信元2が受動的にデータを出力するものであるとき、出力されるデータに対して配列処理を行う送信元アドレス変換部5と、データ送信先3が受動的にデータを入力するものであるとき、データ送信先3に入力するデータに対して配列処理を行う送信先アドレス変換部6と、を備える。

(もっと読む)

機能拡張型メモリコントローラを備えるグラフィックス処理システム

【課題】迫力のあるグラフィックスを生成するためには競合リソース間におけるメインメモリへのアクセスを効率的に制御するすることが重要である。このために、CPUやグラフィックス関連リソースに対して高い優先順位を付与し、メインメモリへの高速アクセスを保証する。

【解決手段】メモリコントローラ152は、メインメモリ112へのアクセスをシークする様々な競合メモリ間の調停、メモリアクセス要求リソースのメモリ待ち時間および帯域幅必要条件の対処、バスターンアラウンドを減少させるためのバッファ書き込み、メインメモリのリフレッシュ、およびプログラム可能なレジスタを用いてのメインメモリの保護など、メモリ制御関連の様々な機能を果たす。メモリコントローラ152は、それぞれ異なる競合リソースからの書き込み要求をキューにいれる、「グローバル」書き込みキューを使用してメモリの読み出し/書き込みの切り替えを最小にする。

(もっと読む)

情報処理装置

【課題】コンプリーションデータの順番を並び替えるためのバッファを各マスタに設ける必要をなくす。

【解決手段】中継部は、メモリから返信されてきたコンプリーションデータC−A1,C−A2,C−B1を返信中継する際に、送信中継情報とタグを用いて、以下の処理をする。同じマスタに返信するコンプリーションデータであって対応するリードリクエストの順番が先であるコンプリーションデータを中継していれば、返信されてきたコンプリーションデータを中継し、順番が先であるコンプリーションデータを中継していなければ、順番が先であるコンプリーションデータを中継するまで返信されてきたコンプリーションデータをバッファ53で保持する。

(もっと読む)

制御装置およびデータ記憶装置

【課題】データの書き込み速度の高速化を図ると共にRRAMの劣化を抑制する。

【解決手段】ホスト装置10から書き込み要求信号が入力されたときには、ホスト装置10から入力されたデータを順次エンコーダ30に入力し、エンコーダ30から出力されたデータがRRAM24に記憶されるようRRAM24を制御し、RRAM24に記憶されているデータのサイズが所定サイズSrefに至ったときにはRRAM24に記憶されて所定サイズSrefのデータが読み出されるようRRAM24を制御し、RRAM24から読み出されたデータをエンコーダ32に入力し、エンコーダ32から出力されたデータがフラッシュメモリ22に記憶されるようフラッシュメモリ22を制御する。これにより、データの書き込み速度の向上とデータの信頼性の向上を図ることができる。

(もっと読む)

データ処理装置及びデータ処理システム

【課題】効率的にデータを読み出す。

【解決手段】割り当てられた記憶装置50の記憶領域に記憶されたデータを使用する工程の前かつ当該データの読み出し位置を示すアドレスを生成して出力する工程の後にデータ読み出しのための待ち時間に応じたNOP工程が配置されたパイプライン処理を各々が行う複数の画像処理部10を備え、画像処理部10の各々に対応させて、中間バッファ32、アドレスバッファ34、アドレスバッファ34に書き込まれたアドレスを順に読み出して記憶装置50からデータを読み出し中間バッファ32に書き込むDMA制御部33、及び画像処理部10から出力されたアドレスをアドレスバッファ34に書き込むと共に中間バッファ32に書き込まれたデータを画像処理部10に転送する画像処理部I/F31を設ける。更に、各DMA制御部33に対して記憶装置50に対するアクセス権を排他的に付与する排他制御部40を設ける。

(もっと読む)

画像処理装置およびその動作方法

【課題】画像処理装置がDRAMから画像領域をアクセスする際に、DRAMの複数のページの境界を横断するアクセスが発生しても、ページミスによるアクセスのオーバーヘッドの増大を軽減する。

【解決手段】画像処理装置1は、画像処理部18、メモリアクセス制御部12、内蔵メモリ16を具備する。画像処理部は、水平方向と垂直方向とにそれぞれ所定の画素数を少なくとも有する画像領域MBに含まれる画素情報を処理する。メモリアクセス制御部12はDRAM7と内蔵メモリ16をアクセス可能とされ、両方のメモリに画素情報を格納可能とされる。DRAM7への格納の際にDRAMの複数のページ間のページ境界を横断するアクセスが発生する場合に、一方のページの境界領域BAのデータは内蔵メモリ16に格納され、他方のページのデータはDRAMの他方のページに格納される。

(もっと読む)

ストアマージ装置、情報処理装置、ストアマージ方法およびプログラム

【課題】主記憶上の異なるアドレスに対するストア命令が中央処理装置から出力された場合にも記憶装置へのアクセスを抑える。

【解決手段】ストアバッファ回路12が、複数のストア命令を記憶しておく。そして、ストアバッファ回路12は、中央処理装置60からストア命令が出力されると、当該ストア命令と主記憶装置70上で同一のアドレスに対するストア命令を記憶しているか否かを判定し、記憶していると判定した場合は、この記憶しているストア命令をマージ回路11に出力する。これにより、主記憶装置70(記憶装置)へのアクセスを抑えることができる。

(もっと読む)

SIMDプロセッサのためのメモリコントローラ

【課題】外部メモリ上のデータの並列度が低い場合であってもSIMDプロセッサによるSIMD演算の効率を向上させ、高速なデータ処理を実現する。

【解決手段】メモリコントローラ20は、DDRメモリ30におけるアドレスを格納するアドレスメモリ22と、各アドレスからデータが連続して格納される長さをそれぞれ表すバースト長を格納するバースト長メモリ23とを備える。メモリコントローラ20は、第1のグループのプロセッサエレメントと、アドレスメモリ及びバースト長メモリに格納された第1のアドレス及び対応する第1のバースト長によって特定されるDDRメモリ30の領域との間で、第1のデータを転送し、第1のデータの転送後、第2のグループのプロセッサエレメントと、アドレスメモリ及びバースト長メモリに格納された第2のアドレス及び対応する第2のバースト長によって特定されるDDRメモリ30の領域との間で、第2のデータを転送する。

(もっと読む)

メモリ管理装置およびメモリ管理方法

【課題】フラグメンテーションの発生を抑制でき、メモリの有効利用に有利なメモリ管理装置およびメモリ管理方法を提供する。

【解決手段】実施形態によれば、不揮発性半導体メモリ61〜6nと揮発性半導体メモリ5とを備えるメインメモリ65を管理するメモリ管理装置3であって、前記不揮発性半導体メモリへのデータ書き込み動作の際に、書き込み対象のデータについて、該データのデータ属性により決定される書き込み頻度についての情報22に基づき、前記不揮発性半導体メモリ上の書き込み領域の振り分けを行う振り分け部78と、前記振り分けられたデータを、追記方式により前記不揮発性半導体メモリに書き込む制御部77とを具備することを特徴とするメモリ管理装置。

(もっと読む)

データ処理装置

【課題】マスタ動作モジュールが、容量を低減した内部メモリを使用して、多様なアクセス方法で必要なデータのみを読み取れるデータ処理装置の実現。

【解決手段】CPU12と、マスタ動作モジュール14と、マスタ動作モジュールから直接アクセス可能な内部メモリ20Aと、外部メモリ18から内部メモリにデータを転送するデータ転送部13と、を有し、内部メモリは、ページ単位で論理的に分割した2以上のページ記憶領域と、転送されたデータを内部メモリのアドレスに変換して書き込む書き込みアドレス変換部22と、読み出しアドレスを内部メモリのアドレスに変換してデータを読み出す読み出しアドレス変換部23と、状態遷移制御部24と、を備え、書き込みが行われたページ記憶領域に対して読み出し動作を行い、読み出し動作が終了したページ記憶領域に対して書き込み動作を行うように制御する。

(もっと読む)

メモリ装置及び信号処理装置

【課題】入力されたデータを効率的に記憶して出力することのできる装置を提供すること。

【解決手段】書込みバッファ122及び書込み制御部123を有する書込みバッファ部121と、129メモリ部と、読出しバッファ125及び読出し制御部126を有する読出しバッファ部124と、メモリ部129にデータが格納されているか否かを示すメモリ使用状態を記憶するメモリ使用状態記憶部130と、書込みバッファ122、読出しバッファ125及びメモリ部129に記憶されているデータのデータ量に応じて、書込みバッファ部121、メモリ部129及び読出しバッファ部124の間でデータ転送を行う転送制御切替部131と、を備えるメモリ装置120を提供する。

(もっと読む)

メモリシステム及びそのデータ転送方法

【課題】メモリシステムの回路面積を縮小する。

【解決手段】メモリシステム10は、データ部に対して誤り訂正のためのパリティビットを生成するECCエンコーダ17と、ページ単位でデータを格納する不揮発性メモリ11と、パリティビットを用いてデータ部の誤りを訂正するECCデコーダ18と、不揮発性メモリ11から読み出されたページ、或いはECCエンコーダ17から転送されたフレームを一時的に格納する第1のメモリバッファ15と、パリティビットが付加される直前のデータ部、或いはECCデコーダ18により誤りが訂正されたデータ部を一時的に格納する第2のメモリバッファ19と、不揮発性メモリ11及び第2のメモリバッファ19間のデータ転送を制御し、かつデータコピー動作時に第1のメモリバッファ15をシリアルにアクセスするデータ転送制御部22とを含む。

(もっと読む)

フレーム処理装置及びフレーム処理方法

【課題】バッファの空きアドレスを格納するアドレス記憶部から読み出す値に異常が生じたときに発生するバッファのリソースの低減を防止する。

【解決手段】フレーム処理装置1は、バッファ2の空きアドレスを記憶するアドレス記憶部3と、巡回アドレスによって読出アドレスを指定することによりアドレス記憶部3から読み出した空きアドレスへフレームを書き込むフレーム書込部4と、バッファ2の各アドレスの使用状態を記憶する第1記憶部10と、バッファ2にフレームを書き込むときフレームが書き込まれるアドレスについて第1記憶部10に記憶される使用状態を変更する状態変更部11と、巡回アドレスが一巡する期間に亘って書込処理が行われず、かつ未使用であると第1記憶部10に記憶されるアドレスを検出するアドレス検出部20を備える。

(もっと読む)

メモリシステム

【課題】ホストからの指示に応じて消費電力の上限を抑制可能なメモリシステムを提供する。

【解決手段】並列動作可能な複数のバンクを有する不揮発性半導体メモリと、ホストからの電源管理コマンドを受信すると、受信した電源管理コマンドを解析するコマンド解析部と、このコマンド解析部の解析結果に応じて書き込みの際に並列動作させるバンクの上限数を動的に可変制御する記録制御部とを備える。

(もっと読む)

アクセス管理装置、情報処理装置、アクセス管理方法

【課題】複数のプロセッサが共有リソースにアクセスする際の調停頻度を、キャッシュやバッファを抑制するアクセス管理装置、情報処理装置及びアクセス管理方法を提供すること。

【解決手段】複数のプロセッサ11から要求された共通のリソース16へのアクセス要求を制御するアクセス管理装置100であって、複数のプロセッサ11から受け付けたリードアクセスの複数のアドレスを比較するアドレス比較手段13と、複数のアドレスのうち一致したアドレスのデータをリソース16からリードするデータリード手段14と、データリード手段14がリードしたデータを、一致した複数のアドレスを出力した複数のプロセッサ11に同じタイミングで出力するデータ出力手段15と、を有することを特徴とする。

(もっと読む)

携帯可能電子装置及び携帯可能電子装置の制御方法

【課題】 ICカード処理装置からのコマンドに応じてICカードが不揮発性メモリ上のデータ格納領域へのデータの書き込みを行う処理に要する時間を短縮することができる。

【解決手段】 外部装置から受信したコマンドに基づいてデータを不揮発性メモリ上のデータ格納領域に書き込む必要がある場合、不揮発性メモリ上のバッファ領域に当該データを書き込み、上記バッファ領域へのデータの書き込みが終了した際にバッファ領域への書き込み完了を示す応答データを外部装置へ出力し、当該データをデータ格納領域に書き込むようにしたものである。

(もっと読む)

ストレージリソースの階層化管理方法及びシステム

21 - 40 / 270

[ Back to top ]