Fターム[5B060CD01]の内容

Fターム[5B060CD01]の下位に属するFターム

バッファへの要求受付処理 (7)

要求のバッファ内順序管理 (64)

バッファから要求送出制御 (18)

Fターム[5B060CD01]に分類される特許

1 - 20 / 34

メモリデバイス

【課題】高品質なメモリデバイスを提供する。

【解決手段】メモリデバイスは、不揮発性のメモリ73と、コマンドが格納されるコマンド格納部74と、コマンドをホストデバイス2から受信し、コマンドをコマンド格納部74に格納すると共にコマンドを実行し、コマンドの実行が終了した後、コマンドの実行の終了を知らせる第1の信号をホストデバイス2に送信する制御部71とを備え、制御部71は、第1のコマンドに応答してメモリ73についての書き込み、読み出し、または消去を実行し、第2のコマンドに応答して、コマンド格納部74内の第1のコマンドまたは実行中の第1のコマンドを中断し、第2のコマンドを実行した際、中断対象となる第1のコマンドのうち、中断可能な第1コマンドを中断すると共に、中断対象となる第1のコマンドのうちで中断されなかった全ての第1のコマンドに関する第1の通知を送信した後、第2のコマンドに関する第1の通知を送信する。

(もっと読む)

電子制御装置およびその制御方法

【課題】処理要求の発生の有無を調べるための時間を短縮し、およびその処理負荷を低減することが可能な電子制御装置および制御方法を提供する。

【解決手段】実行結果に応じて予め定められた機能の動作を要求するための機能動作要求が発生したとき、機能動作要求とともに、機能動作の内容を出力する処理毎に設けられた機能動作要求出力部と、いずれかの機能動作要求出力部から機能動作要求が出力されたとき、機能動作要求があることを表す情報を記憶する機能動作要求記憶部と、処理毎に機能動作の内容を記憶する機能動作内容記憶部と、機能動作内容記憶部の記憶内容を読み出して、いずれの機能の動作を実行するかの調停を行う調停部とを備え、調停部は予め定められたタイミングで機能動作要求記憶部の記憶内容を参照し、機能動作要求記憶部に機能動作要求があることを表す情報が記憶されているとき、機能動作内容記憶部の記憶内容を読み出して調停を行う。

(もっと読む)

フラッシュインタフェースの有効利用

【課題】フラッシュインタフェースの有効利用のための方法を提供する。

【解決手段】第1の回路206、第2の回路204、及び第3の回路208を含む装置。第1の回路は、フラッシュレーンコントローラ(FLC)の動作のために用いられるダイに基づく情報を保持するように構成される。第2の回路は、フラッシュレーンコントローラ(FLC)によってアクティブに処理されているコンテキストを管理するように構成される。第3の回路は、第2の回路によって管理される複数のコンテキストのパイプライン実行を実行するように構成される。

(もっと読む)

メモリシステム

【課題】 DRAMを用いずに、データの高速な読み出しが可能なメモリシステムを提供する。

【解決手段】 複数の不揮発性メモリ11は、複数のチャネルのそれぞれに接続され、複数のバンクを有している。バッファ17は、複数の不揮発性メモリから読み出されたデータを保持し、同時に読み出し可能なデータサイズのほぼ2倍の容量を有するスタティックメモリにより構成されている。複数のチャネル制御部16-0〜16-7は、複数の不揮発性メモリからデータを読み出すための読み出し要求を複数のチャネル毎に保持するキューを有している。バッファ制御部15は、読み出し要求を複数のチャネル制御部のいずれかのキューに供給するとともに、バッファ内に不揮発性メモリから読み出されたデータを保持するための領域を確保する。

(もっと読む)

マルチチャネルを有するメモリ装置及び同装置におけるメモリアクセス方法

【課題】ブロック単位のメモリアクセス処理を、小容量のメモリ領域を用いた管理で高速に実行できるようにする。

【解決手段】実施形態によれば、コマンド生成手段は所定のアクセス処理において、チャネル別のアクセスコマンドの群をメモリインタフェースに逐次投機的に投入する。パージ手段は、複数のチャネルを介してのメモリアクセスのいずれかでエラーが発生した場合、既に投入されている未実行のアクセスコマンドの系列を返却する。コマンド進捗管理手段は、各チャネルにおけるコマンド進捗が、返却された未実行のアクセスコマンドの系列のうちの最も古い未実行のアクセスコマンドの指定する位置を指すようにコマンド進捗情報を更新する。コマンド生成手段は更新された情報に基づき、チャネル別のアクセスコマンドの群をメモリインタフェースに投入する。

(もっと読む)

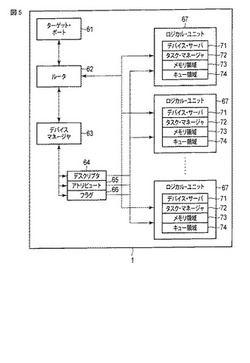

トラフィッククラスと関連するポートをもつマルチポートのメモリコントローラ

【課題】メモリコントローラは、QoSパラメータに対する強調を少なくさせるとともに、メモリコントローラパイプラインを通じてオペレーションが流れるのでメモリバンド幅の最適化に対する強調を増加させる。

【解決手段】一実施例においてメモリコントローラはマルチポートを含む。各ポートは異なるタイプのトラフィック専用である。一実施例においてサービスの質(QoS)パラメータがトラフィックタイプのために定義され、各トラフィックタイプは異なるQoSパラメータ定義を有する。メモリコントローラは、QoSパラメータに基づき異なるポートで受信したオペレーションをスケジューリングするよう構成される。一実施例において、サイドバンド要求を介して及び/又はオペレーションのエイジングを介してより高いQoSパラメータを有するその後のオペレーションが受信されるとき、メモリコントローラはQoSパラメータのアップグレードをサポートする。

(もっと読む)

半導体集積回路、及びリクエスト制御方法

【課題】論理規模を増大させることなく、複数のバスマスタからのリクエスト発行数を増加させる。

【解決手段】本発明による半導体集積回路100は、複数のキュー330と、複数のバスマスタ1、2から発行されたリクエストのアクセス先のアドレスに基づいて、リクエストを複数のキュー330のいずれかに振り分けるリクエスト振り分け部301と、複数のキュー330から選択したキュー内のリクエストを、外部デバイス5に発行するリクエストセレクタ302とを具備する。

(もっと読む)

半導体記憶装置及び半導体記憶装置の制御方法

【課題】CPUからの1コマンドでコンパクション動作が実行される半導体記憶装置。

【課題を解決するための手段】半導体記憶装置は、不揮発性メモリのコマンドをキューイングするキューイングバッファ(26)と、不揮発性メモリのリードコマンドを発行するリード手段(#102)と、リード手段により前記不揮発性メモリから読み出されたデータをユーザデータと管理データとに分離する分離手段(#104)と、不揮発性メモリのライトアドレスを管理するライトポインタ情報により示されるアドレスを分離手段により得られた管理データに対して加えてライトコマンドを発行し、キューイングバッファへ自動的にキューイングするライトコマンド発行手段(#110)と、ライトコマンド発行手段により発行されたライトコマンドを不揮発性メモリに与え、データを不揮発性メモリに書き込むライト手段(#114)とを具備する。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】複数CPU間での排他制御を考慮する必要がなく、簡単な制御で、他の動作の割り込み無く複数チャネルの不揮発性メモリの消去動作を実施すること。

【解決手段】複数のCPUと複数チャネルの不揮発性メモリとを有する半導体記憶装置であって、複数チャネルの不揮発性メモリ毎の消去動作用のアドレスからなるアドレスリストをアドレスキュー(14)に設定する手段()と、いずれかのCPUから発生された単一の消去動作要求に応じて前記アドレスリストに記載の各アドレスについての一連の消去動作コマンドを連続して発生するコマンド制御部(18)と、前記一連の消去動作コマンドを各アドレスに対応したチャネルの不揮発性メモリに与える分配器(24)とを具備する。

(もっと読む)

データ転送システム

【課題】1つのメモリコントローラに対して複数のコントロールマスタを設けたデータ転送システムにおいて、リードコマンドに対する処理効率を向上させる。

【解決手段】メモリコントローラを介して接続された複数のコントロールマスタとメモリとの間でデータリード処理を行なうデータ転送システムであって、メモリコントローラは、リードコマンドを受け付けると、そのリードコマンドに係るコントロールマスタの識別子をFIFO形式で格納するルートセレクタと、メモリから読み出したリードデータをFIFO形式で格納するリードデータバッファとを備え、コントロールマスタは、ルートセレクタに格納されている識別子のうち、最先に格納された識別子が自身の識別子であって、リードデータバッファにリードデータが格納されている場合に、リードデータバッファからリードデータを読み出す。

(もっと読む)

メモリ制御回路

【課題】複数のメモリデバイスを使用するシステム構成において、低電力モードを積極的に利用し、かつ、メモリデバイスへのアクセス効率の低下を起こさないメモリ制御回路を提供する。

【解決手段】メモリ制御回路は、複数のメモリデバイスを制御する複数のチップセレクトと、メモリデバイスをチップセレクトごとに、キューバッファに保存されているコマンドに応じて異なる省電力レベルの省電力モードに移行させる省電力制御手段と、を有する。

(もっと読む)

メモリ制御回路

【課題】省電力化とアクセス効率の維持とが同時に実現することを目的とする。

【解決手段】省電力モードを有する複数メモリデバイスを省電力モードへ投入/省電力モードを解除するメモリ制御回路において、メモリアクセスを最大M個まで一時的に保持するコマンドキューと、前記コマンドキューのN(Nは1以上、M以下)段目までに保持されているメモリアクセスのアクセス対象デバイスの省電力モードを解除する手段とを有することを特徴とするメモリ制御回路等を提供する。

(もっと読む)

異種ソースに対する階層的メモリアービトレーション技術

【解決手段】

階層的メモリ要求ストリームアービトレーション技術は、多重メモリ要求ソース(204,206,208,216)からのコヒーレントメモリ要求ストリームをまとめ、そしてまとめられたコヒーレントメモリ要求ストリームを非コヒーレントメモリ要求ストリームからの要求と共にアービトレートする。本発明の少なくとも1つの実施形態においては、複数のメモリ要求ストリームからまとめられたメモリ要求ストリーム(316)を生成する方法は、コヒーレントメモリ要求を第1のシリアルメモリ要求ストリームへまとめることを含む。方法は、まとめられたメモリ要求ストリーム内での配置のためにメモリ要求を少なくとも第1のシリアルメモリ要求ストリーム及びまとめられた非コヒーレントメモリ要求ストリームからメモリ制御器回路(213,302)によって選択することを含む。まとめられた非コヒーレントメモリ要求ストリームは、まとめられたメモリ要求ストリーム内での配置のために選択された前回のメモリ要求の標識(334)に少なくとも部分的に基いている。

(もっと読む)

データキャッシュとメインメモリ間の一貫性の保証

プロセッサコア、複数のスレッドの各々によってアクセス可能なデータを記憶するキャッシュメモリ、複数のスレッドによってアクセス可能なデータを記憶するメインメモリ、非一貫性検出モジュール、及びメモリアービターを含み、複数のスレッドをサポートするマルチスレッドプロセッサにおいてメモリアクセスを制御するための装置を提供し、非一貫性検出モジュールは、プロセッサコアとメモリアービターの間に接続され、メモリアービターは、非一貫性検出モジュールとメインメモリの間に接続され、キャッシュメモリからメモリアービターに送信された読取及び書込要求に対する各スレッドのための個別の要求待ち行列が存在し、使用においては、非一貫性検出モジュールは、キャッシュメモリからメインメモリに送信された各書込要求に対するメモリアドレスの指示を書込アドレスメモリに記憶し、更に、キャッシュメモリから送信された各次の読取要求のアドレスを書込アドレスメモリ内の指示と比較し、次の読取要求のアドレスが指示に適合した場合に、読取要求に対応する障壁を適合指示が属するスレッドの要求待ち行列内に挿入し、メモリアービターは、対応する障壁がメモリアービターによって受信されるまで読取要求がメモリバスにアクセスしないように阻止する。 (もっと読む)

メモリプリフェッチシステムおよび方法

選択されたメモリヴォールトと関連付けられるパイプラインが空の時に、積層ダイのメモリシステム中の選択されたメモリヴォールトから、プログラム可能ないくつかのデータワードをプリフェッチするように動作するものを含む、システムおよび方法が、本明細書にて開示される。 (もっと読む)

メモリコントローラおよびデータ処理装置

【課題】複数のメモリアクセスリクエスタからのリクエストでも、バスの使用効率を高めるためのグループ化が可能なメモリコントローラおよびデータ処理装置を提供する。

【解決手段】リクエストキュー22は、複数のメモリアクセスリクエスタから受信したリクエストを格納する。併合部31は、リクエストキュー22内のリクエストのうち、DDR2−SDRAMにおける1回の読出しサイクルまたは書込みサイクルでアクセス可能なリクエストを併合する。メモリインタフェース部27は、リクエストに従って、DDR2−SDRAMに対してアクセスを行ない、併合された複数のリクエストに対するDDR2−SDRAMのアクセスを一括して行なう。

(もっと読む)

メモリコントローラ

【課題】 メモリコントローラとメモリ間でのレイテンシを小さくし、メモリコントローラの回路規模も小さくする。

【解決手段】 メモリコントローラ000に、複数のバスインターフェース310、320、330と、この複数のバスインターフェースから発行されるコマンド及びデータを制御し、メモリへの書き込み及び読み出しを行うメモリコントローラコア部100とを備え、メモリコントローラコア部100に、前記複数のバスインターフェースから発行される複数のコマンドを受け付け、該複数のコマンドをリオーダして保持するコマンド制御部110と、前記複数のバスインターフェースから発行される複数のライトデータを、前記コマンド制御部がライトコマンドを受け付けた順に受け付け、当該ライトデータを、前記コマンド制御部によるリオーダの結果に基づいて出力するライトデータ制御部120とを備える。

(もっと読む)

メモリ制御装置,メモリ制御方法および情報処理装置

【課題】プロセッサからのフェッチ要求に対応するフェッチ応答データを主記憶装置から取り出してプロセッサに送出する場合において、フェッチ応答データが到着してからプロセッサに向けて送出されるまでのレイテンシを短縮することを目的とする。

【解決手段】主記憶装置14aから取り出したフェッチ応答データを格納部19をバイパスして受信し、当該受信したフェッチ応答データをセット可能な第1のポート18と、フェッチ応答データを第1のポート18にセットできない場合に、主記憶装置14aから取り出したフェッチ応答データを格納部19を経由してセットする第2のポート20と、第1のポート18または第2のポート20にセットされたフェッチ応答データに対して、予め規定された優先度に従ってプロセッサ13に送出するプライオリティ制御を行なう送出制御部22とをそなえている。

(もっと読む)

記憶システム及び方法

【課題】能率的で好適な記憶システム及び方法を提供すること。

【解決手段】一実施形態では、記憶システム100は、複数の記憶ノード120、130、140、及びマスタコントローラ110を含む。記憶ノードは情報を記憶する。記憶ノード120、130、140は、アップストリーム通信の際の衝突の解決を容易にするように局所的に記憶ノード120、130、140で制御されるアップストリーム通信バッファ160を含む。マスタコントローラ110は、アップストリーム通信バッファの制約条件に基づいて、ノード120、130、140へのトラフィックの流れを制御する。一実施形態では、マスタコントローラ110とノード120、130、140の間の通信が、決められた最大待ち時間を有する。記憶ノード120、130、140は、チェーンメモリ構成によりマスタコントローラ110に結合することができる。

(もっと読む)

データ応答を順序変更するためのシステム

【課題】

データ応答を順序変更するためのメモリ・コントローラを提供する。

【解決手段】

本発明のシステムは決定性システムとリンクを介して決定性システムに電気的に接続されたコントローラとを含む。コントローラは、そのコントローラから発生された要求に対応するその決定性システムからのデータ応答が順序不同で返送されることを可能にするトランザクション・スケジューリング機構を含む。

(もっと読む)

1 - 20 / 34

[ Back to top ]