Fターム[5B061BA01]の内容

Fターム[5B061BA01]に分類される特許

161 - 180 / 240

データ転送装置

【課題】 画像データを転送するためのデータ転送用の専用バス、及びCPU(プロセッサ)がメモリアクセスを行なう専用バスの両方の信号線が必要となる。

【解決手段】 CPU2はCPUバス12を介して、DMAC3はDMAバス13を介してローカルバスコントローラ5と接続し、ローカルバスコントローラ5は、外部のローカルバス11と接続され、ローカルバス11に外部I/Fコントローラ8、コードROM9、フォントROM10が接続されて、外部I/Fからのデータ転送を行うバスとCPUが使用するコードROM9が接続されるバスとしてローカルバス11を共用する。

(もっと読む)

情報処理装置及びバス使用権獲得方法

【課題】バスマスタの数の増加に伴ってバス獲得用の信号線の数が増加するのを防止する。

【解決手段】情報処理装置は、データ転送を行うためのバス12と、入力された信号を伝送するための1本の判断用信号線14と、バス12及び判断用信号線14に接続され、かつ、バスの使用権獲得に関する優先順位が設定された複数のバスマスタを備え、バス12の使用権を獲得する必要があるバスマスタ16は、バス12の使用権を獲得していない他のバスマスタ16によってバス12の使用権の獲得が要求されたとき、他のバスマスタ16と同時に自己の優先順位を示す優先順位信号を信号線14に出力すると共に、信号線14に同時に出力された複数の優先順位信号を合成した合成信号に基づいて、バス12の使用権を獲得したか否かを判断し、バス12を介してデータ転送を行うバスマスタ群とを含んで構成されている。

(もっと読む)

バス調停に関する方法及びシステム

複数のデータ取り扱いユニット110a,….,110d、及び複数のデータラインを有する共有バス140を含むシステムにおいて使用されるべきバス調停に関する方法及びシステムが提供される。本発明は、データ取り扱いユニットからデータ転送要求を受信するステップと、一群のデータ転送要求であって、当該データ転送要求の許可が、最大数のデータ取り扱いユニットを作用させ且つ最大数のデータラインを利用させるような、一群のデータ転送要求を選択するステップと、前記選択された一群のデータ転送要求を発行したデータ取り扱いユニットが単一のバス周期において前記バスにアクセスすることを許可するステップと、を含む方法、及びこの方法を実行させるシステムを提供する。  (もっと読む)

(もっと読む)

バス調停方法及びバス調停プログラム

【課題】優先度が高いタスクを実行する装置に、より効率的にバスが割り当てられるようにバスの使用率を定義したテーブルを作成し、テーブルに従ってバスの調停を行うことにより、優先度の高いタスクの実行時間を短縮できるバス調停方法及びバス調停プログラムを提供する。

【解決手段】バスに接続された複数の装置によって複数のタスクを実行可能なコンピュータにおける前記バスの調停を行うバス調停方法であって、所定のタイミングで、前記複数のタスクの各々の優先度を含むタスク情報を取得する工程と、前記タスク情報に基づいて、前記優先度の高いタスクを実行する装置に優先的に前記バスが割り当てられるように前記複数の装置の各々のバス使用条件を定義したバス使用条件情報を生成する工程と、前記バス使用条件情報に基づいて前記バスの調停を行う工程とを含む。

(もっと読む)

パワーダウン移行システム

【課題】 単一又は複数のマスタモジュールとこれらが共有する共有バスとを有する省電力機能を備えた動作システムにおいては、省電力を実行するパワーダウンモードへ移行するためのソフトウェア又はハードウェアが複雑になって、速やかにダウンモードへ移行するのが難しかった。

【解決手段】 複数のマスタモジュール11,12とパワーダウン用マスタモジュール13を備え、バス調停回路16によって、共有バス15を介してメモリ14にアクセスするためのバス占有権を与える際に、パワーダウン用マスタモジュール13にバス占有権を与える優先度を最も低くし、パワーダウン用マスタモジュール13は、この優先度の最も低いバス占有権を与えられることによってシステムのパワーダウンモードへの移行処理を実行する。

(もっと読む)

転送方向および消費された帯域幅に基づく重み付けバス・アービトレーション

【課題】

【解決手段】バス・アービトレーション・アルゴリズムは、バストランザクションによるバスチャネルの方向、および/またはバスチャネル帯域幅消費を考慮することによって、各マスターデバイスに割り当てられる相対的バスチャネル帯域幅を正確に制御する。少なくとも1つの重み付けレジスタが各マスターデバイスに関連付けられ、一実施形態では、バスチャネルごとに1つの重み付けレジスタとなる。このレジスタは、利用可能なバス帯域幅に比例するシェアで周期的にロードされる。バスチャネル上のバストランザクションが許可されると、対応する重み付けレジスタは、そのトランザクションを完了するために必要なバスデータ転送サイクルの数または転送されるデータ量によって測定される、そのトランザクションによるバスチャネル帯域幅消費を反映する量が減算される。相対的な帯域幅シェアの初期割り当てが同等である場合、バスチャネル帯域幅を消費するマスターデバイスが相対的に低い優先度を有し、バスチャネル帯域幅を消費しないマスターデバイスは相対的に高い優先度を保持する。

(もっと読む)

データストリーマ

【課題】プロセッサ、データキャッシュ、3次元グラフィックスユニット、メモリおよび入力/出力デバイス等の種々のシステム構成要素を収容する統合メディアプロセッサチップセット用データ転送に適合するデータ移動構成を提供する。

【解決手段】プロセッサ、主メモリ、複数のI/Oデバイスを含む複数のモジュールから構成され、プロセッサと主メモリとI/Oデバイスとの間のデータ転送演算を行うデータ転送スイッチで、複数のモジュールからの読取り・書込みリクエストを受けるリクエストバスと、アドレスおよびデータ情報を受けるプロセッサメモリバスとを有し、プロセッサメモリバスは、データ読取り・書込みリクエストを受けるデータバスアービタを備え、また内部メモリバスがデータバスアービタを備え、プロセッサメモリバスと内部メモリバスとの間でデータを転送するため、双方のバスに接続されたトランシーバシステムを更に有している。

(もっと読む)

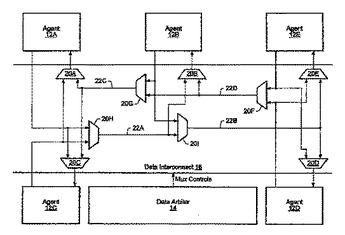

部分的にポピュレートされる階層型クロスバ

様々な実施形態で、装置は、複数のエージェントと相互接続を備える。一実施形態では、複数のエージェントは第1から第4までのエージェントを含む。相互接続は、エージェント間で通信パスを形成するように切換え可能な(例えば複数の選択回路を使用して)複数のセグメントを備え、第1セグメントは、第1エージェントから第2エージェントへの第1通信パスに含まれ、また第3エージェントから第4エージェントへの第2通信パスにも含まれる。別の実施形態では、各セグメントは選択回路によって駆動される。少なくとも1つの選択回路は、少なくとも1つのセグメントと、少なくとも1つのエージェントからの出力とを、入力として有する。さらに別の実施形態では、アービタが、セグメントを介した宛先エージェントへの通信パスを、各要求に対して相互接続上で決定するように構成される。アービタは、対応する通信パス中の各セグメントが利用可能であるような要求のサブセット間で、調停するように構成される。  (もっと読む)

(もっと読む)

切り替え制御装置

【課題】 要求が競合した場合には優先度に応じた調停を行い、複数の機能ブロックからの要求に応じて接続を切り替える際、優先度の高い機能の必要な切り替え応答性を落とすことなく、また、切り替え頻度の最小化によるパフォーマンス劣化を改善する切り替え制御装置を提供する。

【解決手段】データ受信要求によるデータの受信が完了しても、切り替え制御手段210は接続を切り替えることなく共用データバースを通してデータをデータ蓄積メモリ230に蓄積した後、優先度の低い機能ブロックとの接続を再開する。優先度の高い機能ブロックから再度データ受信要求を受けるとデータ蓄積メモリ230のデータを機能ブロックに送信する。

(もっと読む)

バスシステム

【課題】より高い性能を有するスプリット方式のバスシステムを提供する。

【解決手段】レスポンスタイムテーブル14には、ターゲットモジュール4の読み出しコマンドに対する応答時間23が格納されている。レスポンスカウンタ15は、マスタモジュール2から発行された読み出しコマンドの実行が開始された後の経過時間24を計測する。差分算出部16は、応答時間23と経過時間24との時間差25を算出する。コマンド選択部12は受信されたコマンドの中から実行すべきコマンドを選択し、コマンド発行部13は選択されたコマンドをバス8に対して発行する。読み出しコマンドに対する応答待ちの間に別のコマンドが受信された場合には、コマンド選択部12は、当該コマンドの実行が時間差25以内に完了する場合に限り、当該コマンドを実行すべきコマンドとして選択する。

(もっと読む)

マルチバス制御装置及びマルチバス制御方法

【課題】 マルチレイヤバス構成の各バスレイヤに対して、バスの割当をダイナミックに変更可能にすることにより、バスアクセス時間及びバス占有時間を最小にし、低消費電力化を図ること。

【解決手段】 バス100は、レイヤ毎のレイヤバス101〜104から構成されており、DMAコントローラ113、メモリインターフェイス部115及びブリッジ125が接続されている。バスアービタ105は、バス100の制御を行う。CPU111、112は、バスアービタ105により、入出力バスを介してバス100に接続制御されるように構成されており、バスアービタ105の指示により入出力バスのバス幅を変換する。DMAコントローラ113は、DMAコントローラ113のバスも、バスアービタ105を介して、バス100に接続制御されるように構成されている。

(もっと読む)

システムLSI用マルチタスクOS

【課題】 システムLSIの個別構成に特化して高性能にできるOSを提供する。

【解決手段】 ハード側=プロセッサ、メモリ、機能回路モジュール、バス、CPUから制御可能なバスアービタ、を持つシステムLSI。バスアービタはバス上マスタデバイスに優先順位を付けられる。ソフト側=マルチタスクOSであり、タスクの属性としてマスタデバイス管理属性を有し、カーネルがタスク遷移の際に上記属性値を参照してバスアービタを制御。優先度の高いタスクと連動して機能回路モジュールも高速化。

(もっと読む)

バス制御システム及びバス制御方法

【課題】

適切な調停アルゴリズムでバスの調停を行い、効率よくバスを使用できるバス制御システム及びバス制御方法を提供すること。

【解決手段】

本発明にかかるバス制御システムは、バス140に共通に接続されたバスマスタ101a,101b,101cと、バスマスタ101a,101b,101cによるバス140の使用を調停するアービタ120と、バスマスタ101a,101b,101cからのバス使用要求をアービタ120が許可する順番を規定する調停アルゴリズムを切り替えるCPU1と、を備えるものである。

(もっと読む)

バス調停装置及びバス調停方法

【課題】

簡易な構成で、優先順位を確保しつつ全てのバスマスタが必ずリソースにアクセスできるとともに、バス占有率を容易に計算することができるバス調停装置及びバス調停方法を提供すること。

【解決手段】

本発明にかかるバス調停回路100は、バスマスタ1〜6のそれぞれを第1階層RR1,第2階層RR2に階層化する階層情報設定部111と、

第1階層RR1のバスマスタのいずれかもしくは第2階層RR2を選択する第1階層選択部111と、第1階層選択部111が第2階層RR2を選択した場合に、第2階層RR2のバスマスタのいずれかを選択する第2階層選択部112と、第1階層選択部111もしくは第2階層選択部112が選択したバスマスタのバスアクセスを許可する選択信号出力部130と、を有するものである。

(もっと読む)

データ処理装置

【課題】 簡素な構成で、複数のコントローラ間での排他処理によるバス効率の低下を抑制することができるデータ処理装置を提供する。

【解決手段】 複合装置10において、コントローラ100は、割込要求元および割込要求先毎に割当てられた複数の割込要求領域を含むレジスタ110と、信号線156a〜156dを介して各割込要求先と接続される出力端子122a〜122dと、割込要求領域への割込信号発生要求のバス150を介した書き込みに伴って、対応する割込要求先に出力端子を介して割込信号を出力する割込信号出力部120と、を有し、各コントローラ300〜500は、割込情報を記憶するメモリ310〜510と、割込処理を行う場合、割込要求先のメモリ310〜510に割込情報を、およびレジスタ110における割込要求先に対応する割込要求領域に割込信号発生要求を、バス150を介して書き込むPCIC306〜506と、を備える。

(もっと読む)

バスシステム

【課題】 回路規模を増大させることなく、省電力化を実現することができるバスシステムを提供する。

【解決手段】 アクセス量計測部111は、各マスタデバイスの所定期間内におけるバス10へのアクセス量を計測し、消費電力値算出部112は、アクセス量計測部111によって計測されたアクセス量を用いて所定期間内における各マスタデバイスの消費電力値を算出し、アクセス制限部113は、消費電力値算出部112によって算出された各マスタデバイスの消費電力値の合計値が予め設定されている値以上になった場合、マスタデバイスからバス10へのアクセスを制限する。

(もっと読む)

バスシステム

【課題】 信号遅延の削減を図る。

【解決手段】 CPU11と周辺回路31〜34とを接続するバスシステムにおいて、周辺回路31〜34とCPU11との間で信号の送信又は受信を行うフリップフロップ41〜44と、該フリップフロップ41〜44をシフトレジスタが構成されるように接続する接続手段51、52とを備え、CPU11を周辺回路31〜34の内の最も高速応答が要求される周辺回路31に対応するフリップフロップ41に接続する。

(もっと読む)

バス・ブリッジのアビトレーション方法

【課題】 この発明は、バス・ブリッジにIEEE 1394に準拠したバスとの異なる動作バスとが接続されている場合に、IEEE 1394以外のバスにアクセス権が亘らない状況を回避することを目的とする。

【解決手段】 システム内のローカルバスである1次側バスと2次側のバスに相当するバスとのインターフェースを行うブリッジデバイスであり、かつ1デバイスで2種類以上の異なる動作をサポートし、そのうちの1種類がIEEE 1394に準拠したシリアルバスであるバス・ブリッジのアビトレーション方法であって、2次側のアービトレーションの状態にかかわらず、1次側から2次側へのアクセスの場合はそのアクセスを最優先することを特徴とする。

(もっと読む)

半導体ディスク及び情報処理システム

【課題】揮発性メモリから不揮発性メモリへのバックアップ処理の時間を短縮し、かつ、回路規模を縮小することができるようにする。

【解決手段】メモリバス26はシリアル伝送方式となっている。複数の揮発性メモリ22A〜22Cは、シリアル信号及びパラレル信号の何れか一方から他方への変換を行うメモリインタフェース部20A〜20Dを介してメモリバス26に接続される。外部インタフェース部18は、外部と複数の揮発性メモリ22A〜22Cの少なくとも一つとの間で外部データ転送を実行しているときに、揮発性メモリと不揮発性メモリ22Dとの間でメモリ間データ転送を実行する。その際に、メモリバス26の空き伝送帯域を用いてメモリ間データ転送を実行することにより、外部データ転送とメモリ間データ転送とを並列に実行し、バックアップ処理時間を短縮する。

(もっと読む)

データ転送制御装置,データ転送制御方法,データ転送装置,画像形成装置,データ転送制御プログラム、および該制御プログラムを記録したコンピュータ読み取り可能な記録媒体

【課題】 システム設計の難解化を抑制しつつ、所定のバスマスタに対する帯域保証を行う。

【解決手段】 調停回路42は、バス回路を介したデータ転送を制御するバスマスタの各々がデータ転送要求を出力すると、該出力を行っているバスマスタ毎に設定される各優先度に基づいて、いずれか一つのバスマスタによるデータ転送を実行させる構成である。さらに、調停回路42には、帯域保証要求を出力しているバスマスタによるデータ転送について、実効帯域を計測する帯域測定回路52と、上記計測された実効帯域に応じて上記帯域保証要求を出力しているバスマスタに設定される優先度を変更する優先度判定回路51と、を含む。

(もっと読む)

161 - 180 / 240

[ Back to top ]