Fターム[5B061BA01]の内容

Fターム[5B061BA01]に分類される特許

101 - 120 / 240

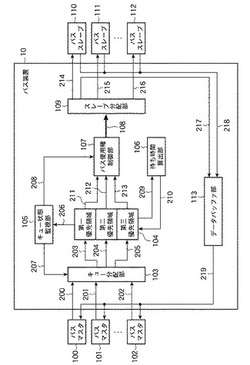

バス装置

【課題】排他制御付き書き込み装置を不要とし、レイアウトの際に配線混雑を回避できるバス装置を得る。

【解決手段】キュー分配部103は複数のバスマスタ100〜102からバススレーブ110〜112に転送するデータを含むバス使用要求を受信して分配し、キュー部104はキュー分配部103から分配されたバス使用要求を複数の領域に分けて保持し、待ち時間算出部106はキュー部104に保持されたバス使用要求の待ち時間を算出し、バス使用権制御部107はキュー部104に保持されたバス使用要求の中から、待ち時間算出部106により算出された待ち時間により、転送するバス使用要求を選択する。

(もっと読む)

接続制御用半導体集積回路及び印刷装置

【課題】製造コストとパフォーマンスのバランスが良いマルチCPUタイプの印刷装置を、提供する。

【解決手段】印刷装置10の制御部13を、共通データバス,N組のコントロールバス及びアドレスバスにより、2個のCPUと接続される、バス使用要求を出したCPUに、バス使用許可を与える接続制御ASIC20であって、2個のCPUによって同時にバス使用要求が出された場合には、各バス使用要求を出したCPUが出力するアドレスから1個のCPUを特定し、特定したCPUに、バス使用許可を与える接続制御ASIC20が用いられているものとしておく。

(もっと読む)

DMA転送装置およびデータ転送装置

【課題】効率良くDMA転送を行い、特定のモジュールによりデータバスが占有され続けることによって生じる不整合を回避する。

【解決手段】各DMAモジュール12−0〜12−nのいずれかによるDMA転送完了後に次のDMA要求が行われるまでの間隔を示すDMAインターバルの期間値が、各DMAモジュール内のレジスタ12−0a〜12−naに設定されている。各DMAモジュール12−0〜12−nのうちの複数からのDMA要求が競合した場合に、DMAバス調停回路14によって、優先順位が高い例えばDMAモジュール12−1からのDMA要求に対してDMA転送許可が与えられ、そのDMA転送の完了後、DMAモジュール12−1からの次のDMA要求の発生が、DMA転送が完了したDMAモジュール12−1以外の他のDMAモジュール12−0、12−2および12−3からのDMA要求が全てなくなるまで抑制される。

(もっと読む)

デジタルカメラ

【課題】従来のデジタルカメラでは、画像メモリのアクセス速度が不十分であったり、メモリ制御が複雑であるため、CCDデータ取り込み、Y/C分離処理、モニター表示処理、JPEG圧縮処理、外部メディア記録処理などの複数の信号処理を並列に処理することが困難であり、トータルとしての信号処理時間が長くかかってしまうという問題があった。

【解決手段】本発明は、撮像素子の出力をデジタル化する撮像回路と、デジタル化された映像信号を処理する複数の信号処理回路と、前記複数の信号処理回路からのメモリアクセス要求を調停するアービタと、メモリアクセスを中継するメモリ制御回路と、メインメモリを備え、アービタは予め定められた優先順位に従って最も優先度の高い要求信号に応じてアクセス許可信号を出力し、アクセス許可を受けた信号処理回路がメモリ制御回路を介してメインメモリにアクセスする。

(もっと読む)

バスインターフェース回路および情報処理装置

【課題】バスの使用効率を向上させる。

【解決手段】内部処理モジュール311は一定の周期で繰り返される第1の期間の先頭を検出する。内部処理モジュール311は、バス使用許可信号を受信してから最初に第1の期間の先頭が訪れた場合に、第1の期間よりも短い第2の期間内に、読み出しの対象であるデータのアドレスをバス100に出力する。内部処理モジュール311は、第2の期間に続いて、予め定められた正の整数を周期に乗じた第3の期間が経過した場合に、第3の期間に続いて、周期から前記第2の期間を差し引いた第4の期間内に、当該アドレスに対応するデータであって、スレーブ装置がバス100に出力したデータを入力する。

(もっと読む)

多重バスインタフェースモジュールおよび多重バスシステム

【課題】バスアービタを必要とせず、かつ、効率的な多重バスシステムを容易に設計できる多重バスインタフェースモジュール、および、当該多重バスインタフェースモジュールを備えた多重バスシステムを提供する。

【解決手段】本発明の多重バスインタフェースモジュールRB_HB2は、互いに直列に接続される、複数の中間内部インタフェースモジュールFMn3を備え、個々のFMn3が、上流のRB_HB2からの入力リンクまたは機能ブロックFB1からの入力リンクを、FB1の反対側への出力リンクまたは下流のRB_HB2への出力リンクに接続し、かつ、FB1の反対側からの入力リンクまたは上流のRB_HB2からの入力リンクを、FB1側の出力リンクに接続することができる。よって、個々のFMn3がデータ伝送経路を決定することになり、バスアービタを必要としない多重バスシステムを実現できる。

(もっと読む)

通信制御装置

【課題】バス使用要求信号が集中している場合でも、所定の制御装置は優先的に目的の装

置へアクセスすることができる通信制御装置を提供すること。

【解決手段】ビジータイミング調整回路40からSDRAMビジー信号が出力されると、SDRAMアクセス要求マスク回路37は、即時性の低い制御回路から出力されるSDRAM使用要求信号をマスクする。一方、即時性の高い制御回路からのSDRAM使用要求信号は、ビジータイミング調整回路40からSDRAMビジー信号が出力されていてもマスクせず、SDRAMアクセス調停回路38へ入力される。よって、ビジータイミング調整回路40からSDRAMビジー信号が出力されている場合には、即ち、SDRAM13へのアクセスの頻度が高い場合には、SDRAMアクセス調停回路38は、即時性の高い制御回路へ優先してバス使用許可を付与することができる。

(もっと読む)

デジタル音声信号処理装置における制御信号調停方法

【課題】デジタル音声処理回路を有する基板間の制御信号の双方向通信ができ、配線数が少なく、音声信号との干渉による問題がないデジタル音声信号処理装置における制御信号調停方法を提供する。

【解決手段】少なくとも2枚以上のモジュール20を有し、音声信号のサンプリング周波数と同一の周波数であるワードクロックが各モジュール20に分配され、前記ワードクロックに同期させてモジュール20間で音声信号をシリアル転送するデジタル音声信号処理装置における制御信号調停方法において、前記ワードクロックを計数し、前記計数結果と所定演算を行い、前記所定演算による演算結果が前記モジュールの固有値と一致したとき共有バスラインLaへの送信権を得て、前記音声信号のシリアル転送クロックと同一の転送クロックで制御信号を共有バスラインLaへ送信し、かつ受信権を得たときのみ制御信号を受信する。

(もっと読む)

安全モジュール及び自動化システム

【課題】自動化システムの融通のきく構成を可能にする安全モジュールを提供する。

【解決手段】フィールド機器用入出力モジュール(4a,4b)の接続のために設けられたバスシステム制御モジュール(2)とデータバス(3)を介して接続するための接続部を持つ安全モジュール(5)は、バスシステム制御モジュール(2)に一致してデータバス(3)を介して伝送されるデータの同一処理のために設けられているデータ処理装置(μC2)を持っている。データ処理装置(μC2)は、規則正しいデータ通信の確保のため安全機能を持つように設けられて、データバス(3)を介してバスシステム制御モジュール(2)とのデータ交換により、安全機能の相互検査が行われるようにする。

(もっと読む)

バスアクセス方法およびバスアクセス装置

【課題】複数のバスマスタでバスを共有するバスアクセス装置に関するものであり、バス待ち時間、バス未使用時間およびバス調停時間の短縮、共有バッファサイズの削減を可能とする。

【解決手段】複数のバスマスタの動作モード、周波数、データ転送語数、データヒット率、負荷率、データ処理量、アクセスするバススレーブに応じてバスアクセス1回当たりのバス占有量および共有バッファの占有量を可変制御する。

(もっと読む)

情報処理装置

【課題】 ユーザアクセスバスを介してのハッキングを防止しつつ、暗号化された複数のコンテンツデータを簡易な構成で同時に再生することができる情報処理装置を提供する。

【解決手段】 情報処理装置1は、暗号化されたコンテンツデータを取得して処理するデータ取得部3と、ユーザアクセスバス2を介してデータ取得部3からコンテンツデータを取得して再生するデータ処理部4と、を備えている。データ取得部3は、コンテンツデータを復号化するための復号化データを処理するICカード7と、復号化データを用いてコンテンツデータを復号化する複数の制御プロセッサ部91,92と、各制御プロセッサ部91,92に対し、ICカード7との通信の確立を排他的に許可するアービタ調停部111と、を有している。

(もっと読む)

スプリットバス及びタイムスロットインターフェースバス調停を用いる共有デバイス並びにメモリ

【課題】拡張されたデジタルシステムにおける調停方法及び装置を提供する。

【解決手段】調停装置は、共通のデータバスを分離するアイソレーションデバイス199と、プロセッサまたは他のバスマスターを含む共通のデータバスの内部部分へのアクセスを制御するプライオリティ−ベースのアービタ142、134と、複数のバスマスター295、297、外部メモリインターフェース124等を含む共通のデータバスの外部部分へのアクセスを制御するタイムスロットアービタとを含み、共通のデータバスへの効率的なアクセス制御を可能にする。共通の外部メモリ107は、アイソレートされた共通のデータバスの両部分を使用して、多数のデバイスによる排他的なまたは非排他的な使用のために割り当てられる。外部メモリにアクセスする外部デバイス112は、共通のデータバスの内部部分上で、1つまたはそれ以上のバスマスターと直接通信することができる。

(もっと読む)

半導体回路

【課題】CPUの割り込み処理を早期に実行させることが可能な技術を提供する。

【解決手段】バスマスタ1〜4にはCPUが含まれている。バスマスタ1〜4のそれぞれは共通のバスBUSSを利用してバススレーブ5,6にアクセスする。バスアクセス調停回路7は、バスマスタ1〜4におけるバスBUSSに対するアクセス要求を調停する。割り込みコントローラ8は、割り込み要求が通知されると、CPUに対して割り込み処理の実行を通知するとともに、当該CPUのアクセス要求を優先して受け付けることを要求する優先処理要求信号PPRをバスアクセス調停回路7に出力する。バスアクセス調停回路7は、優先処理要求信号PPRが入力されると、CPUのアクセス要求を他のバスマスタ2〜4よりも優先して受け付ける。

(もっと読む)

信号バス占有調停方法及びデータ転送装置

【目的】簡単な回路構成により信号バスの占有権を複数のデバイス間で調停することのできる信号バス占有調停方法及びデータ転送装置を提供する。

【構成】少なくとも1つの信号バスと、各々が占有許可信号に応じて該信号バスを占有し、これを介してデータ転送をなす複数のデバイスとを含むデータ転送装置における信号バス占有調停方法及びデータ転送装置であり、所定カウント区間内にある各カウント値を時間経過に従って巡回する現在カウント値を保持すると共に、該デバイス毎に、該カウント値の何れかと一致する少なくとも1つの許可タイミングカウント値を保持し、該デバイスのうちの1のデバイスが生成した占有要求信号に応じて、該現在カウント値と該1のデバイスの許可タイミングカウント値とを比較し、双方の値が一致した場合にのみ該1のデバイスに該占有許可信号を供給する。

(もっと読む)

情報処理システム

【課題】情報処理システムにおいて、システムバスでデータ転送に用いられるアクセス経路を分散させて、データ転送の最適化を図る。

【解決手段】CPU2等の各種デバイスが接続されるシステムバスを3つに分割し、各システムバス20A、20B、20Cに各デバイスを分散して接続する。また、システムバス20A〜20C同士は相互にアクセス可能なデバイスとして互いに接続する。そして、各システムバス20A〜20Cには、各デバイスからのアクセス状況を監視するバスモニタ回路を設け、調整回路30が、CPU2が実行するアプリケーション毎に各バスモニタ回路を一定時間動作させて、各システムバス20A〜20C間のアクセス経路で占有率が判定レベルを越える過負荷経路が存在するか否かを判定し、過負荷経路を検出すると、そのアクセス経路の占有率が低くなるように、迂回経路を設定する。

(もっと読む)

バス調停装置及びバス調停方法

【課題】デバイスの優先順位を任意に設定することができ、デバイス間のバス使用権の競合が生じた場合に、システムの動作状況に応じた最適な調停を行うことができるバス調停装置及びバス調停方法を提供する。

【解決手段】デバイス1〜4の各々に対応する順番レジスタ52、初期値レジスタ54及びカウンタレジスタ56には、カウント値を監視する順番、初期値、及びカウント値が各々保持されている。順番レジスタ52及び初期値レジスタ54はプログラマブルであり、カウント値を監視する順番やカウント初期値を、システムの動作状況に応じて適宜書き換えることができる。バス調停回路42は、デバイス1〜4のカウンタレジスタ56のカウント値を定期的に監視し、カウント値が所定値(例えば「0」)になったデバイスだけが調停の対象とされる。調停の対象とされたデバイスの優先順位は、順番レジスタ52で設定された順番に従って決定される。

(もっと読む)

バスシステム

【課題】周波数を上げること無く、必要最低限の転送レートを確保し、消費電力を削減する。

【解決手段】バスシステムは、バス40aと、バスマスタであるCPU31−1及びDMAC31−2と、バススレーブであるメモリ32−1と、転送レートに対応した優先順位設定信号を出力する優先順位設定レジスタ41と、競合状態を調停するアービトレーション回路42と、セレクタ44等により構成されている。CPU31−1は、転送レートに対応した優先順位設定信号S41を出力するように、優先順位設定レジスタ41の設定を変更する。アービトレーション回路42は、優先順位設定信号S41に基づき、バス制御応答信号ACK3,S31−2bのどちらかを選択するようにセレクタ44へバスマスタ選択信号S42を出力する。

(もっと読む)

共通バスアクセス調停システム

【課題】

制御モジュールを二重化したシステムにおける、信頼性の高い共通バスのアクセス制御を実現する共通バスアクセス調停システムを提供することにある。

【解決手段】

現用系制御モジュール(例えば100)と予備系制御モジュール(例えば200)との間で、共通バス400の使用権を調停する調停機能部を、前記現用系制御モジュールと前記予備系制御モジュールがそれぞれ有し(102、202)、現用系制御モジュール100内の調停機能部102が共通バスの使用権の調停を行う構成を採用する。

(もっと読む)

データ転送装置

【課題】既存の通信規格において、簡単な構成で新たにリクエストコマンドを定義でき、新たな優先度の最も高いデータ転送を行うことができるデータ転送装置を提供する。

【解決手段】IEEE1394bの通信規格を基にしたデータ転送装置11は新たに優先度の最も高い「Express」のリクエストコマンドを定義し、そのリクエストコマンドに対する該優先度を決定する外部送信権要求信号RQ1a,RQ1bを新たに定義した。各ポートデコーダ14a,14bは、そのリクエストコマンドに対する外部送信権要求信号RQ1a,RQ1bについて、他のリクエストコマンドとは異なる変換要求信号X1a,X1bをエンコードするように構成した。判定回路16には、そのリクエストコマンドに対する変換要求信号X1a,X1bを最も優先度の高いコマンドと判定する優先度判定テーブル40を設けた。

(もっと読む)

バスシステムおよびバスシステム制御方法

【課題】複数のマスタ1,2とスレーブ3,4がバス5に接続されているバスシステムにおいて、信頼性を保証されるべきデータを転送中に、転送に関わらないマスタやスレーブに異常が生じても、転送データの信頼性を保証できるバスシステムを提供する。

【解決手段】バススイッチ31〜34とスイッチ制御部11を設け、優先(安全)データ転送時は、優先(安全)データ信号71を「1」として、転送に関係無いマスタ2及びスレーブ4のバススイッチ32,34をOFFし、他方、通常データ転送時は、優先(安全)データ信号71を「0」として、全てのバススイッチ31〜34をON状態にする。

(もっと読む)

101 - 120 / 240

[ Back to top ]