Fターム[5B061BA01]の内容

Fターム[5B061BA01]に分類される特許

221 - 240 / 240

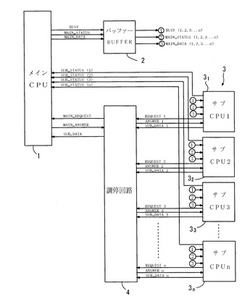

撮像装置におけるデータ通信調停方式及びそのデータ通信調停回路

【課題】超多画素のCCDセンサーを複数の撮像領域に分割し、各撮像領域に対応してサブCPUを設け、メインCPUが各サブCPUを制御するようにし、所定の動作レートで画像処理が可能な撮像装置におけるデータ通信調停方式及びそのデータ通信調停回路を提供する。

【解決手段】メインCPU1に対しサブCPU3が少なくとも二つ備えられ、メインCPU1からサブCPU3の何れかにデータを送信する際、メインCPU1が選択したサブCPU3の受信状態を示すサブステータス信号によりデータの送信が確実な行われたか否かを検出し、かつサブCPU3からメインCPU1に処理済み画像のデータを送信する際は、サブCPU3の送信要求信号を調停回路4で受けて調停回路4から主送信要求信号をメインCPU1に送信し、サブCPU3から優先順位に従ってメインCPU1に処理済み画像のデータを送信するようにしたデータ通信調停方式である。

(もっと読む)

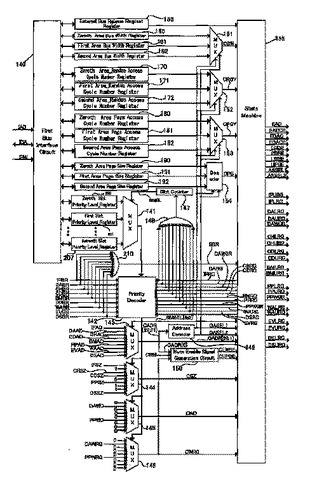

バス・アクセス取り消しを伴うデータ処理システム

バス・マスタ(12)は現在待ち状態にあるアクセスの1つまたは複数の特性に基づいて現在待ち状態にあるアクセスを選択的に取り消す。このようにして、バス・マスタはバス・マスタのアクセス要求をより良好に制御する。1つまたは複数の特性は、例えば、アクセス・タイプ(例えば、読み取り/書き込み、命令/データ、バースト/非バーストなど)、アクセスのシーケンスまたは順序、アクセスされるアドレス(例えば、いずれのアドレス範囲がアクセスされるか、またはいずれのデバイスがアクセスされるか)、取り消しを要求しているバス・マスタ(例えば、マルチマスタ・システムにおける)、およびこれらの任意の組合せを含む。また、バス調停(216)も、現在待ち状態にあるアクセス要求または後続のアクセス要求の1つまたは複数の特性に基づいて後続のアクセス要求を優遇して現在待ち状態にあるアクセス要求を選択的に取り消す。それらの特性は、上にリストアップした特性のいずれか、要求側マスタの優先順位(例えば、要求側マスタ間の優先順位デルタ)、要求側マスタの他の属性、またはこれらの任意の組合せを含む。  (もっと読む)

(もっと読む)

データ処理装置

【課題】 複数の回路モジュールがバスで接続されたLSIにおいて、バス回路やある特定の処理回路の混雑が生じても、システムオンチップの潜在性能を十分に引き出せるデータ処理装置を提供する。

【解決手段】 アクセスが集中するバス回路回路SBS、PBS1,2及びスレーブ回路に状態監視機構ESBS,EPBS1,2を設ける。状態監視機構はクロック制御回路CPGなどのシステム制御回路や、CPUコアなどマスタ回路に、得られた状態を通知する機構を有し、更に、マスタ回路にはバス回路やスレーブ回路に処理の優先順位を通知するための優先順位を動的に切替できる機構PRIOが設けられる。

(もっと読む)

デバイスコントローラ

アドインボード上のPCIデバイスやカードデバイスを制御するために用いられるデバイスコントローラである。マスタデバイスを含む複数のデバイスをアドインボード上に搭載し、かつ、それらのデバイスの動作を円滑に制御することでマルチファンクションのPCIデバイスまたはカードデバイスを構築するために、デバイスコントローラ(1)に、デバイス(D1〜D8)からのバスマスタ要求に対応するバスアービタ回路(17)を設け、バスアービタ回路(17)およびターゲット検出回路(16)によりイニシエータおよびターゲットを検出させ、バスシーケンサ2に前記検出結果に基づいた適正な手順でバスマスタサイクル等における信号の発行を制御させるとともに、アドインボード(30)をホスト装置に単一のマルチファンクションデバイスとして認識させる。  (もっと読む)

(もっと読む)

アクセス制御装置

【課題】複数のバスマスタにおけるバススレーブに対するアクセス要求を調停する際に使用される時間情報を適切に制御することが可能な技術を提供する。

【解決手段】アクセス調停回路ACは、バスマスタBM0,BM1のそれぞれに対応する記憶回路MEM内の許容待ち時間情報に基づいて、バスマスタBM0,BM1のバススレーブBS0,BS1に対するアクセス要求の許容待ち時間を更新する。そして、これらの許容待ち時間を比較し、その比較結果に基づいてバスマスタBM0,BM1のどちらかのアクセス要求を受付ける。また、バスマスタBM0は記憶回路MEM内の許容待ち時間情報を制御することができる。

(もっと読む)

共有バス調停システム

【課題】 小規模な回路構成で共有バスの調停を実現すると共に、チップサイズの縮小化に寄与し、更に共有バスを共有するCPU等の数の変更に対して簡単に対応できる共有バス調停システムを提供することを目的とする。

【解決手段】 システムクロックを発生するシステムクロック発生回路6と、複数のCPU(1、2及び3)と、各CPUの駆動条件を記憶するレジスタ21、22及び23と、CPU1、2及び3に共有される共有バス8と、システムクロックに同期してカウント値を更新するカウンタ7とが備えられている。各CPUは、カウント値が自身の駆動条件を満たす時に共有バス8の使用権を獲得し、駆動条件の夫々は、同一のカウント値に対して2以上のCPUの駆動条件が同時に満足することがないように定められている。

(もっと読む)

データ転送装置及びデータ転送方法

【課題】 システムのスループットを低減させることなくデータ転送を効率よく行わせ、かつCPU及びDMA制御部による外部メモリへのアクセス競合を確実に調停する。

【解決手段】 外部メモリ109との間のデータ転送をCPU102の動作と独立して行うDMA制御部106及び外部バスインタフェースユニット107を内蔵するコンピュータシステムシにおいて、DMA制御部106の制御による外部メモリ109とのデータ転送をDMA制御部106と外部バスインタフェースユニット107との間に設けたローカルバス110を通して行い、CPUの制御下での外部メモリとのデータ転送及びDMA制御部の制御下での外部メモリとのデータ転送に対する優先順位を外部バスインタフェースユニットに設けた転送順位設定手段111により設定する構成にした。

(もっと読む)

データを交換する集積回路および方法

複数の処理モジュールM,Sと、第1のモジュールMと少なくとも一つの第2のモジュールSとの間に少なくとも一つの接続を設けるネットワークN,RNとを備えた集積回路が設けられる。前記接続は、前記第1のモジュールから前記第2のモジュールへの送信メッセージと、前記第2のモジュールから前記第1のモジュールへの応答メッセージとを有する。前記集積回路は、前記第1および第2のモジュールM,Sにより交換されたデータをドロップする少なくとも一つのドロップ手段DMを備えている。したがって、トランザクション完了のための代替の方式が設けられ、完全かつ中間のトランザクションの完了は、特定の場合のみに適用される。本発明は、特定の場合にデータのドロップを許容させるアイデアに基づいている。  (もっと読む)

(もっと読む)

メモリ制御装置およびメモリ制御方法

【課題】CPUがアクセスするアドレスや時間で優先順位を変化させることで、画像形成装置のパフォーマンスをソフトウェアも含めて改善すること。

【解決手段】本発明のメモリ制御装置は、CPU10と、CPU10のアクセス先のアドレスを監視し、所定のアドレスの場合に優先順位変更指示を出力するアドレスR/W監視部14と、CPU10および少なくとも1つのDMA22・24によるメモリ31へのアクセスを所定の優先順位に従って制御するアービタ20と、前記優先順位変更指示を受け取った場合に、所定の時間の間前記優先順位を変更する優先順位設定部21と、を備える。

(もっと読む)

スケーラブル・マルチチャネル・メモリアクセスのための方法、及びメモリコントローラ

本発明は効率的で柔軟性のあるメモリアクセス制御を行う電子機器とその対応する方法に関する。本発明に従う電子機器(及びその対応する方法)は、少なくとも1つのメモリアクセスユニットと少なくとも1つの物理的なメモリモジュールを有するメモリとに接続され、その機器は、少なくとも1つのシステムバスを介して少なくとも1つのメモリアクセスユニットと前記少なくとも1つの物理的なメモリモジュールとに接続される少なくとも1つのアクセスチャネル回路を有し、前記アクセスチャネル回路は、前記メモリの少なくとも一部への前記少なくとも1つのメモリアクセスユニットによるメモリアクセスを提供する。このようにして、同時/並列的メモリアクセスが達成される、効率的で柔軟性の高いメモリアクセスが提供される。本発明によって提供されたスケーラビリティにより、メモリコントローラ/メモリアクセスの方法の特定の実施例が適切なニーズ(速度や柔軟性など)に調整されることが可能になる。さらに、メモリアクセス機器間での競合の危険性の削減やその危険性をなくすことが可能になる。また自動データ転送/プリフェッチが提供され、データ転送を高速化する。本発明はまた、プログラムを有するコンピュータ可読媒体に関する。そのプログラムにより、コンピュータは本発明の方法及び移動体通信端末における機器/方法の利用を行うことが可能になる。  (もっと読む)

(もっと読む)

グラフィックオブジェクト処理装置及びグラフィックオブジェクト処理方法

【課題】 パイプライン構成のモジュールのストールを回避または軽減するか、またはストールの影響を軽減させ、高速なグラフィックオブジェクト処理装置を提供する。

【解決手段】 本発明は、ラスター画素イメージを形成するべくグラフィックオブジェクトの任意の属性に関して所定の処理を行うグラフィックオブジェクト処理装置であって、前記グラフィックオブジェクトの任意の属性に関する複数の処理を行う複数の処理手段と、前記複数の処理手段のそれぞれからのバスアクセスを調停するバスアクセス調停手段と、を備える。そして、バスアクセス調停手段は、さらに、前記複数の処理手段からのバスアクセス要求を調停結果に基づいてシステムバスに転送するバスインタフェース手段と、前記複数の処理手段それぞれの負荷状態を検出する状態検出手段と、前記状態検出手段による検出結果に基づいてバス調停アルゴリズムを実行し、前記バスインタフェース手段を制御する制御手段とを有している。

(もっと読む)

シングル・チップ・データ処理装置とデータ処理システム

【課題】 使い勝手のよいシングル・チップ・データ処理装置とデータ処理システムを提供する。

【解決手段】 外部インターフェイス回路により、データ処理装置がモード端子を介して受けたバス使用権制御信号にしたがってスレーブ・モードで動作するとき、第1端子をバス使用権要求信号を出力する為の端子とし、第2端子をバス使用許可信号を受けるための端子として利用できるように設定する。上記外部インターフェイス回路は、上記データ処理装置が上記モード端子を介して受けたバス使用権制御信号にしたがってマスター・モードで動作するとき、上記第1端子をバス使用許可信号を出力する為の端子とし、上第2端子をバス解放要求を受ける為の端子として利用できるように設定する。

(もっと読む)

データ転送制御装置

【課題】転送元からのデータ転送要求に対して異なったバスを介したデータ転送を行うことができるデータ転送制御装置を提供することを目的とする。

【解決手段】外部20からデータを受信した場合にデータ転送要求信号DREQを出力する外部接続手段16と、データ転送要求信号DREQを受信した場合に、外部接続手段16から第1のバス11を介して当該第1のバス11に接続された第1の格納手段13にデータを転送する第1の転送手段17と、データ転送要求信号DREQを受信した場合に、外部接続手段16から第2のバス12を介して当該第2のバス12に接続された第2の格納手段14にデータを転送する第2の転送手段18と、外部接続手段16が出力したデータ転送要求信号DREQを第1又は第2の転送手段17,18の何れか一方に受信させる制御手段15と、を備えるデータ転送制御装置。

(もっと読む)

データ転送方法及びシステム、入出力要求装置、並びに、データ転送プログラム及び同プログラムを記録したコンピュータ読取可能な記録媒体

【課題】 外部記憶装置にそなえられた複数の論理デバイスに対して入出力要求を行なうことにより複数のパスを使用してデータ転送を行なう際に、論理デバイスに要求されるアクセスレスポンスの速度に応じて、論理デバイスのアクセスレスポンス性能の低下を抑止できるようにする。

【解決手段】 外部記憶装置にそなえられた複数の論理デバイスと、これら複数の論理デバイスに対して入出力要求を行なう入出力要求装置との間で複数のパスを使用してデータ転送を行なうデータ転送方法において、複数の論理デバイスの優先度を設定する第1ステップS10と、この第1ステップS10で設定された優先度に基づいて論理デバイス毎に各パスの使用比率を設定する第2ステップS20と、この第2ステップS20で設定された使用比率になるように各パスを使用してデータ転送を行なう第3ステップS40,S50とを含むようにする。

(もっと読む)

調停装置、調停方法、調停方法のプログラム、調停方法のプログラムを記録した記録媒体及び電子スチルカメラ

【課題】調停装置、調停方法、調停方法のプログラム、調停方法のプログラムを記録した記録媒体及び電子スチルカメラに関し、例えば複数の処理回路でメモリを共用する構成に適用して、メモリ等へのアクセス権を複数の処理回路に適切かつ効率良く設定することができるようにする。

【解決手段】 本発明は、優先順位に従ってアクセス権を設定することを前提にして、基準回路からのアクセス要求と、基準回路より優先順位の低い処理回路からのアクセス要求とが競合した場合に、基準回路へのアクセス権の設定回数に対する優先順位の低い処理回路へのアクセス権の設定回数が、事前の帯域制限値に応じた値となるようにアクセス権を設定する。

(もっと読む)

データ処理装置及びバス調停装置

データ転送のスループットの向上を図りながらも、各バスマスタがバス使用許可を取得するまでの待ち時間を極力短縮でき、かつ、バス使用効率の向上を図ることができるバス調停装置を提供する。バスマスタは、リード/ライトを行うデータのサイズを示すサイズ信号(例えばCDSZ)を与える。ステートマシン155は、サイズ信号に応じた数のバスサイクルを与えるので、バスマスタは、データを連続してリード/ライトできる。バスマスタが要求したサイズに応じた数のバスサイクルを単位として、必ず調停動作が行われる。サイズ信号はバスマスタが発行するので、データ転送に必要充分なサイズ情報の発行が可能であり、そうすると、ステートマシン155は、バスサイクルの最適な数を設定できる。

(もっと読む)

(もっと読む)

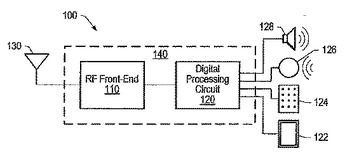

制限されたバス・アクセスを伴う時間領域分離を実装する通信装置

無線周波数信号で動作する無線周波数回路と、無線周波数回路に結合されたデジタル処理回路とを含む通信装置。デジタル処理回路は、共有バスに結合された複数のバス・マスタを含む。バス・アービタが、第1のバス・マスタと1つまたは複数の他のバス・マスタによるバスへのアクセス要求の間を調停するために提供される。1つまたは複数の他のバス・マスタによるバスへのアクセスが、RF回路の動作モードの変更を示す信号に応答して制限される。特定の一実装では、通信装置は、無線周波数回路がアクティブなときにデジタル処理回路がシャットダウン・モードに置かれ得る、時間領域分離を使用する。  (もっと読む)

(もっと読む)

データ通信方法

データバスの参加部の周期的で且つ競合のないデータ通信を実施するための方法であって、それらの参加部が、参加部サイクルインターバル範囲内の重なり合わない時間間隔内でデータを送信し、課題を処理し、またそれらの参加部には、プランニング段階において参加部サイクルインターバル範囲内の固定の送信時間スロットが割り当てられる、前記方法において、参加部の課題処理が参加部サイクルインターバル範囲内のアプリケーション時間インターバル範囲内だけで実施され、プランニング段階において各参加部の送信時間スロットが、アプリケーション時間インターバルに対してディスジョイントされた、参加部サイクルインターバル範囲内の送信時間インターバル範囲内で選択され、そして、選択された送信時間スロットが、参加部に対し、後続する初期化段階において通知される。  (もっと読む)

(もっと読む)

低電力共用リンクアービトレーション

相互接続が複数のイニシエータネットワークの資源と複数の目標ネットワークの資源に結合する種々の方法及び装置が記載される。相互接続は、回路の第1ステージ、回路の第2ステージ、アービトレーションコントローラを含む。回路の第1ステージは、複数のイニシエータネットワークの資源からトランザクションを受け取る。回路の第2ステージは、トランザクションを相互接続に接続している複数の目標ネットワークの資源に渡す。アービトレーションコントローラは、目標ネットワークの資源の1つ又はそれ以上に向けられた複数のイニシエータネットワーク資源からトランザクションをアービトレートする。目標ネットワーク資源は、アービトレーションコントローラにトランザクションをサービスするためにその可用性を示す。アービトレーションコントローラは、イニシエータネットワーク資源からの、現在利用できない目標ネットワークの資源向けのトランザクションをアービトレーションプロセスからフィルタアウトする。 (もっと読む)

データ処理装置

【課題】DMAコントローラ等のCPU以外のバスマスタからのバス使用権要求によりCPUにおける処理が滞ってシステムのスループットが低下するのを防止できるシングルチップマイコンを実現する。

【解決手段】CPU優先レベル制御回路(119)を設け、そこに設定された優先レベルを示す信号をCPU以外のバスマスタ(DMAコントローラ113,115)に供給して、当該CPU以外のバスマスタに設定されている優先レベル(比較基準値)とCPUのその時点の優先レベルとを比較して動作(DMA転送)を開始するか否か判定するように構成した。

(もっと読む)

221 - 240 / 240

[ Back to top ]