Fターム[5B079BC01]の内容

Fターム[5B079BC01]に分類される特許

201 - 220 / 506

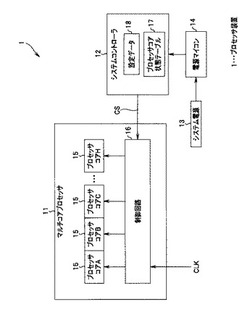

プロセッサ装置

【課題】電源供給の状態に基づいて、プロセッサコア毎にクロック信号を供給又は停止する制御を行うことにより消費電力を低減する。

【解決手段】プロセッサ装置1は、複数のプロセッサコア15を搭載するマルチコアプロセッサ11と、電源供給の状態を検知し、クロック信号を供給するあるいは供給しないプロセッサコア15を指定するための制御信号を出力するシステムコントローラ12と、制御信号に基づいて、クロック信号を供給するあるいは供給しないプロセッサコア15の指定を制御する制御回路16とを有する。

(もっと読む)

サーバの消費電力制御装置、サーバの消費電力制御方法及びコンピュータプログラム

【課題】本発明の消費電力制御装置は、仮想サーバを有する物理サーバの消費電力を適切な値に制御する。

【解決手段】管理サーバ1は、各仮想サーバ5及び仮想化機構4のそれぞれの負荷(CPU使用率)の合計量と物理サーバ2のCPU総量との差から、未使用のCPU量(CPUを使用できる時間)を求める。管理サーバ1は、未使用のCPU量に基づいて、物理サーバ2内のCPUの駆動周波数を決定する。管理サーバ1は、決定された駆動周波数に応じて、各仮想サーバ5及び仮想化機構4のそれぞれに関するCPU割当量を変更する。仮想化機構4は、管理サーバ1からの指示に従い、CPU割当量及び駆動周波数を制御する。これにより、物理サーバ2の消費電力が制御される。

(もっと読む)

マイクロコンピュータ

【課題】スリープモードの場合でもシリアル通信を行うことが可能なマイクロコンピュータを提供する。

【解決手段】CPUの通常動作モードで生成するメインクロックとは別に、該通常動作モードよりも消費電力量が少ないスリープモードでサブクロックを生成し、スリープモードにおいてサブクロックにより動作し、周辺回路とのシリアル通信を行うシリアル通信手段と、受信データに基づいて、動作モードをスリープモードから通常動作モードに切り替えるウェイクアップが要求されるウェイクアップ要因が発生したか否かを判定するウェイクアップ要因判定手段と、ウェイクアップ要因が発生したと判定されたときに、動作モード切換手段に対し、動作モードをスリープモードから通常動作モードに切り替えるためのウェイクアップ信号を出力するウェイクアップ信号出力手段を備えることを特徴とする。

(もっと読む)

半導体集積回路装置および半導体集積回路装置のクロック制御方法

【課題】消費電力削減の効果を発揮すること。

【解決手段】パイプライン接続された複数の演算装置4と、データ通知信号が入力されると処理制御信号を生成し出力する処理制御装置2と、処理制御信号が入力されるとクロック制御信号を生成し出力するクロック制御信号生成装置3と、を備え、演算装置4は、クロック制御信号が入力されると、クロック制御信号に基づいて、演算装置を動作させるゲーテッドクロック信号を生成し出力するクロックゲーティング回路5と、ゲーテッドクロック信号に同期して動作し、データおよび処理制御信号が入力されると、データに対して処理制御信号が指示する処理を行い、処理後のデータおよび処理制御信号を後段に接続された演算装置4へ出力する演算ブロック6と、クロック制御信号が入力されると、クロック制御信号を処理後のデータおよび処理制御信号と同期するように、演算ブロック6での処理時間分遅延して、後段に接続された演算装置4へ出力する遅延回路7と、を備える。

(もっと読む)

データ処理システムの強制アイドル

【課題】データ処理システムの電力を管理する方法及び装置を提供する。

【解決手段】第1周波数及び第1電圧で動作するシステムの制約パラメータが監視される。システムは、制約パラメータの監視に基づき、第2周波数及び第2電圧で動作する間にアイドル状態へと強制される。アイドル状態は、インストラクションが実行されるのを防止する。

(もっと読む)

クロック信号生成装置

【課題】消費電流を低減すると共にクロック信号を早期に安定出力することができるクロック信号生成装置を提供する。

【解決手段】クロック信号生成装置は、水晶発振子からの発振信号を定電流値に応じて増幅して得られた増幅発振信号の振幅が閾値振幅を超過したと判別した場合に当該増幅発振信号に基づいてクロック信号を生成し、該クロック信号のクロックパルス総数が所定のパルス数を超過したと判別した場合に該定電流値を低減する。

(もっと読む)

マルチデバイスシステム

【課題】ソフトウエアの介在なしにクロックの供給を停止する対象を抽出し、その供給の停止を行う。

【解決手段】複数のスレイブデバイスの各々に対してクロックの供給/停止を制御するクロック供給部13と、マスタデバイスによって行われるデータの送受信処理の開始と終了をシステムバス1の信号をモニタリングすることで検知するバスモニタ10と、バスモニタ10の検知によってデータの送受信対象として選択されていないと判定されたスレイブデバイスのうちクロックの供給を停止できるスレイブデバイスを特定するコントロールテーブル12とを備え、クロック供給部13は、コントロールテーブル12によって特定されたスレイブデバイスのクロックを停止する。

(もっと読む)

基板バイアス制御を活用する電力性能最適化コンパイラ及びプロセッサシステム

【課題】マルチプロセッサシステムにおいて、複数の並列化可能なタスクをプロセッサユニット(PU)に効率的に割り当て、また、性能・電力面でのシステム全体の実行効率を上げるために、全体の実行時間に影響を与えるタスクを高速に実行し、電力効率の観点から、全体の実行時間に影響を与えないタスクは低速に実行する。

【解決手段】入力プログラムを複数のタスク(MT0〜MT3)に分割し、複数のPU(PU0,PU1)に割り当てるコンパイラにおいて、全体実行時間を小さくするようタスク割当を行うプロセスと、全体性能に対し影響を与えるタスクを実行するプロセッサの周波数を一時的に向上させる電力制御プロセスと、全体性能に対し影響を与えないタスクを実行するプロセッサの周波数を一時的に低減させる電力制御プロセスを含む。

【効果】マルチプロセッサシステムの性能を最大限活用しつつ、低電力にて効率よく処理することが可能となる。

(もっと読む)

携帯電子装置及び動作クロック制御方法

【課題】 電池駆動の携帯電子装置で、動作クロック周波数の適切な制御を行い、低消費電力化を図る。

【解決手段】 第1部品回路と、第1部品回路との間でデータを授受する第2部品回路と、前記データを授受する経路内に設けられたFIFOとを備える携帯電子装置の動作クロック制御方法において、FIFOが単位時間内で一杯または空になる回数を計数し、該計数値に応じて第1部品回路の動作クロックの周波数変更を行う。

(もっと読む)

情報処理装置、情報処理装置のクロック信号制御方法およびクロック信号制御プログラム

【課題】データの取得・検索を行う処理において、消費電力を増大させること無く、適切にクロック制御を行って処理の高速化を実現する。

【解決手段】RAM110には、過去に行われたデータの取得・検索処理の結果得られた結果情報(検索条件、検索結果件数、取得時間(データを取得するまでにかかった時間))がテーブル情報として記憶される。今回用いる検索条件と、当該検索条件にしたがって参照されるRAM110のテーブル情報に基づいて、今回用いる検索条件にしたがって行うデータの取得・検索処理がボトルネックになる処理か否かを判断し、CPU130により、クロック信号発生部140を制御し、CPU130で用いられるクロック信号とRAM110などのメモリへのアクセスのためのクロック信号との一方あるいは両方を制御する。

(もっと読む)

情報処理装置、情報処理方法、プログラム及び記録媒体

【課題】情報処理装置のデータ処理手段により、処理するデータに応じた電力モードでデータを処理して消費電力を低減する。

【解決手段】CPU21を有するASIC20のネットワークコントローラ40と、ネットワークとの接続部であるPHY15とを接続してパケットを送受信する。省電力モード時にパケットを受信したときには、ネットワークコントローラ40により、受信パケットの処理の要否を判定して、処理不要のときには受信パケットを破棄する。また、処理要のときには、クロックジェネレータ22によりクロック周波数を変更する等して、CPU21の電力モードを受信パケットに応じた電力モードに切り替え、受信パケットの処理等を実行させる。

(もっと読む)

マルチダイマイクロプロセッサにおける周波数及び性能を最適化する方法、装置、及びシステム

【課題】 マルチコアプロセッサ化が進んではいるが、各コアは、アイドル又はアクティブステータスに関して、他のダイのステータスを容易に確認することができない。

【解決手段】 マルチダイマイクロプロセッサにおける複数のコア間でコアステータスを伝送するインターフェイスを使用する提案を記載する。これは、各コアのステータスを使用して性能及び周波数の最適設定を可能にして熱管理を容易にする。

(もっと読む)

半導体集積回路装置

【課題】回路ブロックの動作状態が、半導体集積回路装置の予め定められた消費電力の許容値を超えないようにする。

【解決手段】複数の回路ブロックと電力制御回路とを設ける。上記複数の回路ブロックのそれぞれは少なくとも第1の状態と第2の状態とを含む複数の動作状態をもつ。上記第1の状態における上記回路ブロックはその機能に従って動作し、上記第2状態においては動作が停止される。上記電力制御回路は、上記複数の回路ブロックの動作状態を決定する際に参照する消費電力の許容値を記憶する記憶手段を有する。そして上記電力制御回路は、上記消費電力の許容値を超えないように上記複数の回路ブロックの上記動作を決定し、上記許容値を第1の値から第2の値に変更する際に、上記許容値を前記第1の値と前記第2の値との間の値に段階的に変更する。これにより、一度に動作可能になるサブ回路ブロック数を抑え、電流変動による電圧変動を小さくする。

(もっと読む)

信号処理プロセッサ

【課題】簡易な構成で消費電力の低減を図ることができる信号処理プロセッサを提供する。

【解決手段】プログラム1の内容に応じてプログラム1の命令中にALU及びメモリのNOPコードを挿入する制御部2と、プログラム1の命令中のNOPコードをデコードするデコーダ3と、ALUへの動作クロックの供給を制御し、NOPコードのデコード結果に基づいてALUへの動作クロックの供給を停止するクロック制御部4と、メモリへの動作クロックの供給を制御し、NOPコードのデコード結果に基づいてメモリへの動作クロックの供給を停止するクロック制御部6とを備えた。

(もっと読む)

マイクロコンピュータシステム

【課題】メインCPU部に対する電源の供給制御をより適切に行い、低消費電力化を図ることができるマイクロコンピュータシステムを提供する。

【解決手段】メインCPU4を含むメインマイコン2とは別に、サブCPU8と、メインマイコン2への電源供給を制御する電源制御部24とを備えるサブマイコン3を設け、サブマイコン3に低周波数のサブクロック信号を供給するサブクロック部9を、連続モードと間欠モードとに切り替え可能とする。メインCPU4が、自身の動作停止条件が成立したと判断してサブCPU8に動作停止通知を行うと、サブCPU8はその通知を認識し、メインマイコン2への電源供給を停止させてサブクロック部9を間欠モードに設定する。サブCPU8は、間欠モードでサブクロック信号が供給されている期間に動作開始条件が成立したかを判断し、条件が成立するとサブクロック部9を連続モードに切り替えてメインマイコン2に対する電源供給を再開させる。

(もっと読む)

ナビゲーション装置及び消費電流制御方法

【課題】外部から供給可能な制限電流が変わる場合でも、確実に動作し得るナビゲーション装置及び消費電流制御方法を実現する。

【解決手段】PND1の本体部3では、本体部3の消費電流が外部から供給可能な制限電流以下となるよう、CPU23が、少なくとも、液晶ディスプレイ2及びGPS受信部27の消費電流を低減させるこれらを制御するようにしたことにより、例えば、外部の電力供給元がシガーソケットからUSB接続されたパーソナルコンピュータ11に変わるなどして、外部から供給可能な制限電流がより小さな値に変わった場合でも、ナビゲーション装置の消費電流が外部から供給可能な制限電流を超えて動作を途中で終了してしまうような状況を未然に回避することができ、かくして、外部から供給可能な制限電流が変わる場合でも、確実に動作することができる。

(もっと読む)

プロセッサハードウェアフィードバックメカニズムを用いた最適プロセッサ性能レベルを選択するためのシステムおよび方法

【課題】最適プロセッサ周波数を選び、電力を減少させるための、ハードウェアフィードバックを使用した適応型パワーマネジメントに関するシステム及び方法を提供する。

【解決手段】最適プロセッサ周波数を選択し消費電力を低下させるためのハードウェアフィードバックを使用した適応パワーマネジメントであって、ハードウェアフィードバックおよびプロセッサストール状態挙動に基づいてプロセッサ周波数および消費電力の使用を最適化する。

(もっと読む)

データ処理システム

【課題】ハードウェアでデータ処理の処理性能を制御することにより、合理的な精度で処理性能を制御するデータ処理システムを提供する。

【解決手段】データ処理部110を有するデータ処理システムにおいて、データ処理の処理性能を測定し、その結果としての測定性能値を格納する第1のレジスタ121と、目標とする所定の処理性能である目標性能値を格納する第2のレジスタ122と、第1のレジスタ121に格納された測定性能値と第2のレジスタ122に格納された目標性能値とを比較する性能比較部123と、性能比較部123の比較結果に応じて、データ処理の処理性能を調整する性能調整部124とを有する。

(もっと読む)

プロセッサ

【課題】擬似並行的に複数のプログラムを効率的に実行可能なプロセッサを提供する。

【解決手段】複数のレジスタ群と、複数のレジスタ群のうちいずれか1つを、プログラム実行の基礎とする実行対象レジスタ群として選択し、選択先を所定時間毎に切り替えるレジスタ切替部412と、切り替え毎に、実行対象レジスタ群にあるレジスタ値群によりプログラムを特定し、特定したプログラムを実行する処理実行部410と、プログラムの実行を中断する中断事由が発生していることを検出し、中断事由が解消したことを検出し、プログラムの実行をするハードウエアの消費電力を低減する処理制御部411とを備え、処理実行部410は、プログラムについての中断事由の発生が検出された場合、中断事由が解消するまでプログラムの実行のために割り当てられるべき実行期間を放棄し、処理制御部411が放棄している間、電力低減を実施するプロセッサ。

(もっと読む)

デジタル信号処理装置

【課題】演算内容に応じて消費電力をきめ細かく削減できるようにすること。

【解決手段】レジスタ80は、4ビットのデータをクロックに同期して保持するフリップフロップを8つ備え、32ビットの乗算結果を最上位ビットから順に4ビットずつ分けて保持する。制御回路70は、乗算器50で乗算される入力データAと係数データBについて、最下位ビットから連続する0の総数を検出し、検出した0の総数に基づいてイネーブル信号EN[7:0]の値を設定する。イネーブル信号EN[7:0]は、レジスタ80に備わる8つのフリップフロップについて、クロックの供給の有無を個別に規定する信号である。制御回路70は、例えば、0の総数が“13”であった場合、レジスタ80において下位12ビットの値を保持する3つのフリップフロップについて、クロックの供給を停止させるため、イネーブル信号EN[7:0]の値を“11111000”に設定する。

(もっと読む)

201 - 220 / 506

[ Back to top ]