Fターム[5B079BC06]の内容

Fターム[5B079BC06]に分類される特許

1 - 20 / 42

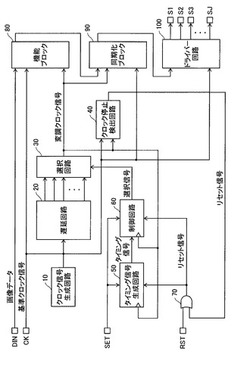

半導体集積回路装置及びそれを用いた電子機器

【課題】クロック信号のスペクトラムを拡散することによって電磁放射ノイズを低減する半導体集積回路装置において、規模が小さくシンプルで確実に動作する回路構成を用いて、デッドロックや誤動作から確実に復帰する。

【解決手段】この装置は、基準クロック信号に基づいて多相クロック信号を出力する遅延回路と、多相クロック信号の内の1つを選択信号に従って選択することにより変調クロック信号を生成する選択回路と、変調クロック信号の生成が停止したときにリセット信号を出力するクロック停止検出回路と、リセット信号によってリセットされ、変調クロック信号に含まれているパルスの数をカウントすることにより、周期的にタイミング信号を生成するタイミング信号生成回路と、タイミング信号に応答して、変調クロック信号の周波数を所定の変調周期において増減させるように選択信号を生成する制御回路とを具備する。

(もっと読む)

クロック生成回路、クロック生成方法および半導体集積回路

【課題】占有面積や定常位相誤差の増大、並びに、クロックが安定するまでに長時間を要することなく、スペクトラム拡散クロックを生成してEMI対策を図る。

【解決手段】基準信号CK1を受け取って、立ち上がりエッジの傾き、または、立ち下がりエッジの傾き、または、立ち上がりエッジおよび立ち下がりエッジの傾きを、周期的に変化させた第1信号CK2を生成する第1回路4と、前記第1信号を受け取って、周期的に周波数が変化するクロックを生成する第2回路5と、を有する。

(もっと読む)

電子機器

【課題】複数の回路間で伝送路を介して第1クロックを伝送し、それぞれの回路で第1クロックを分周あるいは逓倍した第2クロックを用いる電子機器において、第1クロックと第2クロックとの伝送路でのクロストークを防止する。

【解決手段】リセット信号に基づいて動作を開始し、第1クロックを分周/逓倍して第2クロックを生成する第1分周/逓倍回路を備えた第1回路と、伝送路を介して入力したリセット信号に基づいて動作を開始し、伝送路を介して入力した第1クロックを分周/逓倍して第2クロックを生成する第2分周/逓倍回路を備えた第2回路と、を含むことを特徴とする電子機器。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 残ピークノイズを低減させることができるとともに、ジッターの増大を防止することのできるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 実施形態のスペクトラム拡散クロックジェネレータは、チャージポンプ回路1が、出力電流量が設定に応じて変化する可変電流源を有し、位相比較器14により検出された位相差に応じた期間、VCO11へ印加する電圧を制御するためのチャージ電流を出力する。

(もっと読む)

半導体集積装置およびそれを備える表示装置

【課題】電磁波の不要輻射および伝送欠陥を低コストで低減することができる、半導体集積装置およびそれを備える表示装置を提供することを目的とする。

【解決手段】タイミングコントローラIC400が含む出力インターフェース回路420_1は、出力バッファ422と、出力バッファ422の後段に設けられた減衰部424とを有している。出力バッファ422は、正側画像信号DV1(+)および負側画像信号DV1(−)からなる差動信号を出力する。減衰部424は、1対のローパスフィルタ425Aおよび425Bを有している。ローパスフィルタ425Aおよび425Bにより高周波成分がそれぞれ減衰された正側画像信号DV1(+)および負側画像信号DV1(−)は、それぞれ伝送線路610Aおよび610Bに与えられる。

(もっと読む)

電子機器

【課題】複数の接続部に動作クロックを出力すると、それぞれのクロックの立ち上がり及び立ち下がりにより生じる電磁波の周りへの影響が大きい。

【解決手段】電子機器は、信号の授受する動作クロックの周波数が同じ複数の外部機器が接続される複数の接続部と、複数の接続部に対して互いに位相をずらした動作クロックを出力するクロック出力部とを備える。クロック出力部は、複数の接続部のうちの2つに対して互いに逆位相の動作クロックを出力する。

(もっと読む)

クロック発生回路

【課題】ロックアップタイムを短くすることのできるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、基準クロックRCLKに基づいて、周波数を変調させた変調クロックSCLKを発生するスペクトラム拡散クロック発生回路10と、基準クロックRCLKと変調クロックSCLKとの位相の一致を検出したときにHレベルのロック信号LOCKを出力する位相比較器20とを含む。また、クロック発生回路1は、Hレベルのロック信号LOCKが出力されるまでは基準クロックRCLKを出力クロックCLKとして選択し、Hレベルのロック信号の出力に応答して変調クロックSCLKを選択するセレクタ50を含む。

(もっと読む)

クロック生成回路

【課題】小規模な回路で、クロックノイズが小さなクロック信号を生成可能なクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1の電流生成回路と、第1の電圧生成回路と、第1の比較回路と、第2の電流生成回路と、第2の電圧生成回路と、第2の比較回路と、クロック出力回路と、制御回路と、を備える。クロック出力回路は、第1および第2の比較結果が変化するタイミングに同期して位相が変化するクロック信号を生成する。制御回路は、前記クロック信号に同期して乱数を生成し、この乱数に応じて、第1の電流、第2の電流、第1の閾値および第2の閾値電圧のうち、少なくとも1つを可変制御する。

(もっと読む)

アダプタ、情報機器、情報システム及び通信方法

【課題】 高価格化及び実効転送速度の低下を招くことなく、機器間の情報通信において、要輻射(EMI)を低減することができるアダプタを提供する。

【解決手段】 カードアダプタは、ボード、該ボードの一端近傍に設けられたカードエッジコネクタ315、該ボード上に実装された2つのトランシーバソケット(312A、312B)、変換素子317、及び4つのコネクタなどを有している。そして、変換素子317は、カードエッジコネクタ315と2つのトランシーバソケット(312A、312B)との間を電気的に接続する複数の配線パターンの途中に設けられ、該複数の配線パターンのクロックドメインを、クロックがスペクトラム拡散クロックであるクロックドメインと、クロックが非スペクトラム拡散クロックであるクロックドメインとに分割している。

(もっと読む)

マルチコアプロセッサ及びこれを用いる車載電子制御装置

【課題】各コアの動作周波数を時系列で適切に変動させることで、放射ノイズ等の問題点を少なくとも部分的に解決すること。

【解決手段】 本発明は、複数のコアを搭載したマルチコアプロセッサ1,2であって、複数のコアA,B,Cは、同一の周期Tで周期的に周波数が変動する動作クロックで動作するように構成され、コアの動作クロックの周波数の変動位相が、前記複数のコア間でずらされることを特徴とする。好ましくは、各コアの動作クロックの周波数の変動位相は、時間T/N(Nはコア数)に相当する位相ずつずらされる。好ましくは、コアの動作クロックの周波数の変動態様は、複数のコア間で、変動位相が異なる以外は同一である。

(もっと読む)

クロック送受信回路

【課題】

クロック配線からのクロストークを抑制できるクロック送受信回路を提供する。

【解決手段】

クロックを送信し送信した前記クロックを受信するクロック送受信回路において,入力クロックを入力し擬似乱数ビット列に基づく第1のクロックを生成する擬似乱数ビット列生成ユニットと,第1のクロックと入力クロックとを入力し排他的論理演算を行い第2のクロックを生成する送信側排他的論理演算器とを有する送信ユニットと,送信ユニットが生成する前記第1,第2のクロックを伝播する第1,第2のクロック配線と,第1,第2のクロック配線を伝播してきた第1,第2のクロックを入力し排他的論理演算を行い出力クロックを生成する受信側排他的論理演算器を有する受信ユニットとを有する。

(もっと読む)

画面表示制御装置およびこの画面表示制御装置の制御用プログラム

【課題】必要なときにのみクロックアップすることにより、画像メモリからの画像データの読出しを阻害することなく、画像メモリへの画像データの書込みを確実に行うとともに、コストダウンを図ることのできる技術を提供する。

【解決手段】画像データ書込要求信号と画像データ読出要求信号との受付けが重複したときにのみ、RAM制御部765は、高速モードの高クロックを生成するように、クロック切換部764に対してクロック切換信号を出力するため、必要なときにのみクロックを切換えてクロックアップすることにより、VRAM766からの画像データの読出しを阻害することなく、VRAM766への画像データの書込みを確実に行うことができる。また、必要なときのみクロックアップすることで、放射電磁波などを低減できるとともに省電力を図ることができるためコストダウンを図ることができる。

(もっと読む)

通信制御装置、通信制御方法、プログラム、及び記憶媒体

【課題】放射ノイズの発生を抑制することができる通信制御装置を提供する。

【解決手段】通信制御装置100のマスター制御部8は、クロック信号を発生させる発振器5と、複数のスレーブ用通信制御部3a,3b・・・3xの各通信データ量に応じて、発振器5により発生したクロック信号の周波数を変調し、変調した変調クロック信号を対応するスレーブ用通信制御部3a,3b・・・3xのそれぞれに送信するクロック信号変調部とを有する。

(もっと読む)

計測ユニット及びユニット着脱型計測器

【課題】絶縁素子及びその他の信号伝送系から発生する高周波放射ノイズを抑制することができる計測ユニットとこの計測ユニットを備えたユニット着脱型計測器とを得る。

【解決手段】本発明の計測ユニットは、計測回路が、アナログ信号を第1のクロック信号・サンプリングクロックの同期信号に基づきデジタル信号にする信号変換手段と、前記サンプリングクロックの同期信号と同じ周期を有し且つ各周期が少なくとも1つのクロックパルスを有している第2のクロック信号を、前記第1のクロック信号から生成するクロック信号生成手段と、絶縁素子を介して前記デジタル信号及び前記第2のクロック信号が入力され、前記第2のクロック信号を前記第1のクロック信号と同じ周波数に復調し、この第2のクロック信号に基づいて、前記デジタル信号にデジタル処理をさらに施すデジタル信号処理手段とを備えているものである。

(もっと読む)

半導体集積回路

【課題】動作モードによって周波数変調を行うか行わないかを選択することによって受信側の負荷を低減することができる半導体集積回路を提供すること。

【解決手段】半導体集積回路1は、2以上の内部回路(ビデオデコーダ11、CPU12など)と、所定の周波数のクロックを発生するPLL31と、周波数を変調させたクロックを発生するSSCG PLL32と、内部回路にPLL31からのクロックか、SSCG PLL32からのクロックのいずれかを選択して内部回路に入力するセレクタ21とを有する。

(もっと読む)

クロック制御回路及びクロック制御方法

【課題】クロックの停止時及び再開時にクロックを比較的短時間に制御するクロック制御回路を提供する。

【解決手段】クロック停止信号を信号入力端子から入力し、クロック入力を反転クロック端子から入力する第1のDタイプフリップフロップ回路と、前記クロック停止信号を信号入力端子から入力し、前記クロック入力を非反転クロック端子から入力する第2のDタイプフリップフロップ回路と、前記クロック入力と前記第1のDタイプフリップフロップの非反転出力との論理積をとる第1の論理積ゲートと、前記クロック停止信号と前記第2のDタイプフリップフロップの非反転出力との論理積をとる第2の論理積ゲートと、前記第1の論理積ゲートの出力を入力端子から入力し、前記第2の論理積ゲートの出力を駆動能力の制御信号として入力する駆動能力可変クロックバッファと、を備える。

(もっと読む)

クロック信号発生装置

【課題】クロック信号伝送において信号波形歪みや信号遅延による位相ひずみの生じにくいクロック信号を発生するクロック信号発生装置を提供する。

【解決手段】本発明のクロック信号発生装置は、単一の周波数成分からなる第1クロック信号を出力する信号発生部と、上記第1クロック信号の振幅値内に設定された複数の閾値と上記第1クロック信号の瞬時値とをウインドコンパレータによって比較して第1クロック信号の位相を判別し、この位相角度に対応して信号の立ち上がり又は立ち下がりを決定して第2クロック信号を形成する位相角度検出部と、を備える。

(もっと読む)

デジタル復調IC

【課題】システムクロックを発生することなく、チューナの設定データを制御する。

【解決手段】I2C制御部30は、CPUからのアドレスデータに応じてゲート回路36およびクロック発生器24の動作についての設定データをレジスタ34に記憶する。アナログTVの場合には、ゲート回路36を開き、クロック発生器24の動作を停止する。これによって、CPUからの設定データをチューナに供給する。

(もっと読む)

半導体装置、半導体集積回路装置、及び許容位相差測定回路

【課題】低コストで電流ピークを効果的に抑制することができる半導体装置を得る。

【解決手段】ステップST1において、モジュールA21とモジュールB22とのクロック位相を一致させた後、ステップST2において、モジュールA21からモジュールB22にデータ転送を行う。その後、ステップST3において、モジュールA21のクロックCLKAとモジュールB22のクロックCLKBとのクロック位相差を所定の大きさに設定した後、ステップST4において、モジュールA21とモジュールB22とがそれぞれ独立に所定の演算処理を行う。そして、ステップST5において、モジュールA21のクロックCLKAとCPU25のクロックCLKPとの位相を一致させた後、ステップST6においてモジュールA21の演算結果をCPU25で読み取る。

(もっと読む)

集積回路電源ノイズ低減方法および集積回路電源ノイズ低減システム

【課題】 集積回路の電源から放出されるノイズを効率良く低減することができる集積回路電源ノイズ低減方法および集積回路電源ノイズ低減システムを提供すること。

【解決手段】 トランジスタが作動するときの貫通電流によって発生するIC1の電源ノイズを低減する集積回路電源ノイズ低減方法において、前記IC1のベースクロックに対して一定周期単位で位相を遅らせたディレイクロックを複数生成するクロック分散手順と、前記複数のディレイクロックにより動作する回路ブロックを複数の回路ブロック11,12,13,14に分割する回路ブロック分割手順と、各回路ブロック11,12,13,14により生成された位相のずれたノイズ波形と電源ノイズ波形を干渉させて電源ノイズを低減する電源ノイズ低減手順と、を有する。

(もっと読む)

1 - 20 / 42

[ Back to top ]