Fターム[5B079DD08]の内容

Fターム[5B079DD08]に分類される特許

1 - 20 / 244

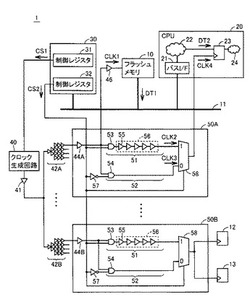

半導体装置

【課題】不揮発性メモリを備えた半導体装置において、高速動作の場合と低速動作の場合とに切替え可能にするとともに、低速動作時の消費電力を従来よりも削減する。

【解決手段】半導体装置1において、クロック生成回路40は、高周波モード時には低周波モード時よりも周波数の高いクロックを生成する。中央処理装置20は、データバス11を介して不揮発性メモリ10から読み出された読出データを取得する。クロック遅延部50Aは、縦続接続された複数段のバッファ55を介した第1の経路51と複数段のバッファ55を迂回した第2の経路52とを含む。クロック遅延部50Aは、高周波モード時には、クロック生成回路40からのクロックを第1の経路51を介して中央処理装置20に供給し、低周波モード時には、クロック生成回路40からのクロックを第2の経路52を介して中央処理装置20に供給する。

(もっと読む)

半導体集積回路及びその省電力制御方法、並びに半導体装置

【課題】デバイス間のインタフェースとしてPCI Expressを用いた画像処理装置において、画像読取部からの画像データで、画像データの転送に影響を与えずに、ASPMを利用可能にする。

【解決手段】LTSSMで定義された状態のうち、低消費電力(省電力)状態にいることを示す信号をLTSSMレジスタ602bからアンド回路603a,603bに出力し、SSCG607からのクロックをマスクすることにより、PCIeのリンクの状態に応じて、ASIC601内の所定の機能モジュールへのクロック供給を止めることができる。これにより、ASIC601の消費電力を削減できる。ASPMによる動的なクロックゲーティングが可能となり、ASIC601内のこまめな省電力制御が実現できる。

(もっと読む)

粗クロックゲーティングを用いた動的周波数制御

【課題】クロックゲーティング回路を用いてクロック信号の周波数を制御するための方法及び装置を提供する。

【解決手段】1つの実施形態では、クロックゲーティング回路にルートクロック信号及びイネーブル信号が供給される。このクロックゲーティング回路は、イネーブル信号がアサートされると、(ルートクロック信号に基づく)動作クロック信号を供給するように構成される。イネーブル信号がデアサートされると、動作クロック信号が阻止される。Nクロックサイクルのうちの1サイクルにわたってイネーブル信号をアサートすることにより、動作クロック信号の周波数を低下した周波数で出力することができる。さらに、ルートクロック信号に対してイネーブル信号をアサートする割合を変更することにより、動作クロック信号を受け取る機能ユニットの動作を中断させることなく、動作クロック信号の周波数を動的に変更することができる。

(もっと読む)

クロック動作システム

【課題】クロック信号に正確に同期した動作が行えるクロック動作システムを、小さな回路規模で実現すること。

【解決手段】逆相関係のクロック信号対CKq,CKqxを含むクロック信号群を生成する送信クロック生成回路21と、クロック信号群の送信経路22と、クロック信号群に対して逓倍関係を有する複数のクロック信号に基づいて動作するクロック動作回路23-0,23-1,23-nと、を有し、クロック動作回路は、送信経路を介して送信されたクロック信号群から、複数のクロック信号を生成する逓倍クロック生成回路24を有するクロック動作システム。

(もっと読む)

クロック供給回路及び半導体集積回路

【課題】高速なクロックを内部回路に供給するためには、消費電力の高いクロックバッファを必要とする。そのため、高速なクロックを低消費電力で供給するクロック供給回路及び半導体集積回路が、望まれる。

【解決手段】クロック供給回路は、電圧制御発振器を含むPLL回路と、電圧制御発振器の発振周波数を制御する発振制御電圧に基づいて、電圧制御発振器の発振周波数と略同一の周波数を持つクロックを、PLL回路のリファレンスクロックに同期させて出力する自己発振型バッファ回路と、を備えている。

(もっと読む)

グリッチフリークロック信号マルチプレクサ回路および動作の方法

【課題】クロックマルチプレクサを駆動する第1のクロック入力から第2のクロック入力への切換えにおいて起こるグリッチを低減する。

【解決手段】クロックマルチプレクサ116は、第1のクロック入力を受信し、クロック出力118を提供し、第1のクロック出力における低フェーズ入力レベルに応答してクロック出力における低フェーズ出力レベルを判定する。限定された期間、低フェーズ出力レベルは、第1のクロック入力信号のフェーズレベルに関わらず維持される。クロックマルチプレクサ116は、第2のクロック入力を受信し、第2のクロック入力信号における低フェーズ入力レベルを判定する。第2のクロック入力に応答してクロック出力118を提供することへの切換えは、第2のクロック入力信号における低フェーズ入力レベルの間に起こる。その後、クロックマルチプレクサ116の出力は第2のクロック信号のフェーズレベルに従う。

(もっと読む)

半導体装置

【課題】クロック生成回路からクロック信号を受けるドライブ回路の経年劣化を抑制する。

【解決手段】半導体装置1は、クロック信号INT1−SIGを生成して出力するクロック生成回路2と、クロック生成回路2からクロック信号INT1−SIGを受けるドライブ回路3とを備え、クロック生成回路2は、クロック信号INT1−SIGを生成して出力ノード2aから出力するクロック出力モードと、出力ノード2aの電位をハイレベルに固定する第1のクロック停止モードと、出力ノード2aの電位をロウレベルに固定する第2のクロック停止モードとを有する。

(もっと読む)

集積回路、クロックゲート回路、および方法

【課題】本発明は、集積回路に渡ってクロック信号を分配する時に消費される、電力の量を減少するための技術に関する。

【解決手段】集積回路2は、動作クロック周波数を有する動作クロック信号に応じて作動するように配設される、機能回路4、6を備える。電力を節約するために、クロック信号は、動作クロック周波数よりも低い分配クロック周波数で、集積回路2に渡って分配される。クロック変換器10は、機能回路4、6の動作を制御するために、分配クロック信号を動作クロック信号に変換するように提供される。

(もっと読む)

クロック供給装置

【課題】複数の回路ブロック全体のピーク消費電流を軽減しつつ、複数の回路ブロック全体のリセットを適切に行える仕組を提供すること。

【解決手段】複数の回路ブロックA2〜D5に対してクロックを供給するクロック供給装置1は、複数の回路ブロックA2〜D5の通常動作時には、複数の回路ブロックA2〜D5に、所定のアクティブエッジ位相を持つクロック信号を供給し、複数の回路ブロックA2〜D5のリセット動作時には、複数の回路ブロックA2〜D5のそれぞれに、異なるアクティブエッジ位相を持つクロック信号を供給する。

(もっと読む)

集積回路及び位相制御方法

【課題】分周クロック信号とクロック信号との位相関係を適応的に制御可能な集積回路を提供する。

【解決手段】集積回路は、第1のクロック信号を分周して第2のクロック信号を生成する分周回路と、第1のクロック信号が伝搬する第1の信号伝搬経路と、第2のクロック信号が伝搬する第2の信号伝搬経路と、第1の信号伝搬経路を伝搬後の第1のクロック信号に第2の信号伝搬経路を伝搬後の第2のクロック信号を少なくとも2回掛け合わせることにより出力信号を生成するミキサ回路と、ミキサ回路の出力信号の直流成分を検出する直流検出回路と、直流検出回路が検出した直流成分に応じて第1の信号伝搬経路及び第2の信号伝搬経路の少なくとも一方の伝搬遅延量を制御する制御回路とを含む。

(もっと読む)

クロック発生回路

【課題】ピーク電力の抑制が可能なクロック発生回路を提供すること。

【解決手段】基準クロック11のエッジをカウントし所定のクロックサイクル数毎にタイミング信号を生成するカウンタ回路5と、所定のクロックサイクル数と等しいビット数を有するビットマップ情報14aを記憶するビットマップ回路4aと、基準クロック11からビットマップ情報14aが示す組み合わせでパルスを間引きして間欠するパルス列である間欠クロック12aを生成しタイミング信号に応じて出力する間欠クロック生成回路2aと、所定のクロックサイクル数と等しいビット数を有するビットマップ情報14bを記憶するビットマップ回路4bと、基準クロック11からビットマップ情報14bが示す組み合わせでパルスを間引きして間欠するパルス列である間欠クロック12bを生成しタイミング信号に応じて出力する間欠クロック生成回路2bと、を有する。

(もっと読む)

クロック発生回路及びその制御方法

【課題】従来技術のクロック発生回路は、クロックの周波数の切り替え時において、電流変動を抑制することができないという問題があった。

【解決手段】本発明にかかるクロック発生回路は、第1の周波数を有するクロック信号を第1の周波数よりも周波数が高い第2の周波数に切り替え可能なクロック発生部と、クロック信号のクロックパルスを所定の間引き率でマスクする間欠クロック生成部と、を有する。そして、間欠クロック生成部は、クロック信号の周波数が第1の周波数から第2の周波数に切り替わる場合に、第2の周波数に切り替わる時点から所定の期間、第2の周波数を有するクロック信号のクロックパルスを所定の間引き率でマスクすることを特徴とする。

(もっと読む)

省電力マルチCPUシステム、画像形成装置

【課題】誤って全てのCPUの内部クロックを停止させることなく、一部のCPUの内部クロックのみを停止させて、消費電力を適切に抑制することができる、堅牢性のある省電力マルチCPUシステム及び画像形成装置を提供することを目的とする。

【解決手段】クロック信号を受け付けて動作する複数のCPU10,11と、各CPUにより制御され、当該CPU以外の他のCPUに対するクロック信号の供給及び当該供給の遮断を行う信号供給制御部12〜15と、各CPUに対するクロック信号の供給を監視して、各CPUに対するクロック信号の供給の全てが遮断されているか否かを判断する監視部16と、監視部16により、各CPUに対するクロック信号の供給の全てが遮断されていると判断されたときには、信号供給制御部12〜15により、各CPUのうちいずれかのCPUに対するクロック信号の供給を再開する遮断解除制御部17と、を備える。

(もっと読む)

クロック生成装置、クロック切り替え方法及びプログラム

【課題】クロック生成装置に接続されるスレーブ装置の数が変化し、接続先の負荷容量が変動したとしても、クロック生成装置とスレーブ装置間で定められた切り替え仕様を満たすクロック選択信号を出力する。

【解決手段】クロック生成装置は、スレーブ装置実装検出部において接続されたスレーブ装置の数を検出し、その検出数をバッファタイプ選択部に通知する。バッファタイプ選択部においては、この通知に基づきクロック選択信号を出力する際のバッファタイプを選択する。

(もっと読む)

電子回路、電子機器、デジタル信号処理方法

【課題】多相クロックを使用してデジタル信号処理を行なう場合に、クロック信号の各位相関係を正しく保ったまま高速動作が要求される各デジタル信号処理部まで多相クロックを分配できるようにする。

【解決手段】基準タイミング生成部110は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低い基準タイミング信号J0を生成して局所タイミング再生部120に供給する。局所タイミング再生部120は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低いクロック信号であって、高速信号処理部140におけるデジタル信号処理の基準となる複数のクロック信号でなる多相タイミング信号J2を生成して高速信号処理部140に供給する。高速信号処理部140と局所タイミング再生部120を1対1で設け、1つの局所タイミング再生部120から複数の高速信号処理部140へ多相タイミング信号J2を分配しないようにする。

(もっと読む)

クロックツリー形成システム、クロックツリー形成方法及びプログラム

【課題】タイミング収束のイタレーションを削減する。

【解決手段】半導体集積回路600のクロックツリー700Aが、分周器752が追加されたクロックツリー700Bで置換されない場合について、モジュール761及び762に関するホールドエラー値HEV1を算出する(S105)。クロックツリー700Aがクロックツリー700Bで置換された場合について、モジュール761及び762に関するホールドエラー値HEV2を算出する(S107)。ホールドエラー値HEV1及びHEV2に基づいて、クロックツリー700Aをクロックツリー700Bで置換することで半導体集積回路600のホールドエラーが削減されるか判定する(S108)。半導体集積回路600のホールドエラーが削減されると判定された場合、クロックツリー700Aがクロックツリー700Bで置換された半導体集積回路600を記述する回路データを生成する(S109)。

(もっと読む)

集積回路のメモリインターフェースのためのデューティサイクル補正器回路

集積回路(IC)内のデューティサイクルの歪みを補正するための回路および方法が、開示される。ICは、クロック信号を受信するように連結されるスプリッタ回路を含む。クロック信号は、2つの異なるクロック信号に分割される。クロック信号のうちの1つは、他方の反転したバージョンである。遅延回路は、クロック信号の各々に連結される。遅延回路の各々は、対応するクロック信号の遅延したバージョンを発生させる。補正器回路は、クロック信号の遅延したバージョンの両方を受信するように連結される。補正器回路は、補正されたデューティサイクルを有するクロック出力信号を発生させる。  (もっと読む)

(もっと読む)

共振クロック分配ネットワークの周波数スケール調整された作動のためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。このアーキテクチャにより、選択的にイネーブルされるフリップフロップの導入によって、複数のクロック周波数での共振クロック分配ネットワークのエネルギ効率の良い作動が可能になる。提示されたアーキテクチャは、主として一体化インダクタを有する共振クロックネットワーク設計を目的としており、インダクタのオーバヘッドが出現しない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

プログラム可能な駆動回路を備えた共振クロック分配ネットワークアーキテクチャ

プログラム可能なサイズのクロック駆動回路及びプログラム可能なデューティサイクルの基準クロックを使用して、共振又は非共振モードで複数のクロック周波数の中の任意の1つの周波数で作動する場合に小さなエネルギ消費で目標クロック立ち上がり時間及びクロック振幅を実現する共振クロック分配ネットワークアーキテクチャが開示さる。一般に、このネットワークは、複数のクロック周波数をもつ半導体デバイス、及び高性能で低電力クロックを必要とするマイクロプロセッサ、ASIC、及びSOC等に適用可能である。 (もっと読む)

共振クロックネットワークを従来モードで作動させるためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。提示されたアーキテクチャにより、共振クロック分配ネットワークの従来モードでのエネルギ効率の良い作動が可能になり、クロック波形の目標仕様を満たすことができる。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、アットスピード試験及び達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

1 - 20 / 244

[ Back to top ]