Fターム[5B125BA11]の内容

リードオンリーメモリ (43,397) | メモリ種別 (5,638) | マスクROM (109)

Fターム[5B125BA11]の下位に属するFターム

配線接続 (41)

Fターム[5B125BA11]に分類される特許

1 - 20 / 68

半導体記憶装置

【課題】リーク電流に起因した半導体記憶装置の誤動作を抑制する。

【解決手段】半導体記憶装置1は、グローバルビット線50及びそれに接続された複数の回路ブロック30を有する。各回路ブロック30は、メモリセル部11、センスアンプ22、及びセンスアンプ22の出力をゲート入力とし、ドレインがグローバルビット線50に接続されたプルダウントランジスタ23を含む。センスアンプ起動信号SAEに基づき、一の回路ブロック30が選択されたときには、選択された回路ブロック30のプルダウントランジスタ23のソースがHレベルになり、非選択の回路ブロック30のプルダウントランジスタ23のソースがLレベルになる。

(もっと読む)

半導体不揮発記憶回路及びその試験方法

【課題】メモリセルを形成するトランジスタペアのオン電流差(マージン)自体を確認した上で出荷することができ、製品の製造時テストや出荷時テストをより厳しく行い、製品の信頼性を高めることが可能な半導体不揮発性記憶回路を提供する。

【解決手段】半導体不揮発記憶回路は、メモリセル(例えばCEL<1>)を形成する一対の第1トランジスタ(例えばN11)及び第2トランジスタ(例えばN22)と、前記第1トランジスタに流れる第1オン電流I1(例えば20μA)と前記第2トランジスタに流れる第2オン電流I2(例えば50μA)との高低関係に応じた論理レベルの出力信号を生成するセンスアンプSAと、第1オン電流I1にオフセット(例えば20〜40μA)を与えるか否か、及び、第2オン電流I2にオフセット(例えば20〜40μA)を与えるか否かを個別に制御するテスト回路TESTと、を有する。

(もっと読む)

半導体記憶装置

【課題】動作中のメモリセルアレイのリーク電流を抑制する半導体記憶装置を提供する。

【解決手段】メモリセルアレイに行方向に配列するメモリセルのゲート端子が行線ノードに接続され、隣り合う2つの行線ノードの集合毎に共通ソースノード駆動回路により電位を制御される1つの共通ソースノードが設けられ、前記2つの行線ノードの何れかにゲート端子が接続するメモリセルのソース端子が前記共通ソースノードに接続され、前記共通ソースノードに係る前記2つの行線ノードの何れにも行デコーダから行選択信号が送信されない場合に、前記共通ソースノード駆動回路が前記共通ソースノードを接地電位から切り離して、前記共通ソースノードにソース端子が接続された前記メモリセルのリーク電流を遮断する。

(もっと読む)

半導体記憶装置及びその回路の電位測定方法

【課題】大規模な半導体記憶装置における不良トランジスタの検出と、不良トランジスタの特性の測定とを高速で行うことができる、半導体記憶装置を提供する。

【解決手段】メモリ素子が縦横にマトリックス状に配列されたメモリセルアレイと、接地ノードあるいは電源ノードに接続する枝配線を有する半導体記憶装置において、電源ノードあるいは接地ノードに接続する少なくとも1つの枝配線の複数箇所に電圧測定点を接続したモニター用スイッチを有し、クロック信号に同期して前記モニター用スイッチのゲートを順に開くスイッチ選択信号発生回路を有し、前記スイッチ選択信号発生回路で選択されてゲートが開かれたモニター用スイッチを介して前記電圧測定点の電位を測定する。

(もっと読む)

半導体記憶装置の製造方法及び半導体記憶装置

【課題】メモリセルアレイの保持内容に起因するリーク電流による誤読み出しを抑制可能な半導体記憶装置を製造する。

【解決手段】接地電位制御要否判定部3が、設計対象のメモリセルアレイの保持内容から、メモリセルのトランジスタの接地電位の制御の要否を判定し、接地電位の制御が必要と判定された場合、接地電位制御回路生成部4が、読み出し動作時に非選択となるトランジスタの接地電位を引き上げる接地電位制御回路を生成する。

(もっと読む)

半導体装置

【課題】メモリ回路を含む半導体装置の低消費電力化を図ることを課題とする。

【解決手段】メモリ回路を含む半導体装置において、メモリ回路はワード線とビット線で規定される領域に設けられた半導体素子を有するメモリセルと半導体素子を有さないメモリセルを含み、該半導体素子には、酸化物半導体を用いて形成したオフ電流が極めて低いトランジスタを用いるため、読み出し精度が高まり、低電圧動作が可能となる。また、メモリセルは、ハイまたはローのいずれか一方のデータを記憶し、半導体素子を有するメモリセルは、前記データを構成するハイおよびローのうち、少ない方を記憶し、半導体素子を有さないメモリセルは、多い方を記憶する。

(もっと読む)

半導体記憶装置

【課題】電力消費をより低減可能な新たなビット線階層化方式を備えた半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、行列状に設けられた複数のメモリブロックBと、複数のメモリブロックBに対応して設けられた複数の主ビット線GLとを具備する。メモリブロックBは、行列状に設けられた複数のメモリセルCと、列ごとに設けられた複数の副ビット線BLと、列及び行ごとに設けられ、複数のメモリブロックBに共通である複数のワード線WLと、対応する主ビット線GLを複数の副ビット線BLのいずれかに接続するスイッチ回路SCとを備える。読出し対象の対象セルC1の読出し動作時に、対象セルC1に対応する主ビット線GL1を選択し、対象セルC1の列に対応する副ビット線BL1をスイッチ回路SC1により選択し、複数のワード線WLのうち、対象セルC1の列及び行に対応するワード線WL1を選択する。

(もっと読む)

電流検出回路

【課題】 印加される電源電圧が低電圧であってもメモリ装置のメモリセルに流れる電流を検出する電流検出動作を正常に行うことができる電流検出回路を提供する。

【解決手段】 同一チャネル型の第1及び第2のMOSトランジスタと、第1及び第2のMOSトランジスタとは異なるチャネル型の第3ないし第6のMOSトランジスタとからなる電流検出手段と、電源電圧が第1及び第2のMOSトランジスタ各々の閾値電圧の絶対値以上であるとき電源電圧から閾値電圧の絶対値を差し引いた電圧を第1及び第2のMOSトランジスタ各々の制御電極に供給するMOSゲート制御手段と、を備える。

(もっと読む)

メモリ

【課題】消費電流(消費電力)が増加するのを抑制することが可能なメモリを提供する。

【解決手段】このメモリ(クロスポイント型のダイオードROM)では、半導体基板の表面に形成された不純物領域22は、メモリセルにおけるダイオードのカソードとして機能するセル領域22bと、コンタクト領域24が形成される配線接続領域22aとを含み、不純物領域22のうちの配線接続領域22aの近傍(抵抗領域22c)の抵抗は、セル領域22bの抵抗よりも大きい。

(もっと読む)

半導体メモリの内部電源制御回路

【課題】スタンバイモード時における消費電流を抑制すると共に、通常動作モードに移行した場合のアクセス速度の低下を抑制する。

【解決手段】内部電源制御回路26は、ROMの内部電源回路から内部回路に常時電源が供給される通常動作モードから消費電力を抑えるスタンバイモードに移行した場合に、内部電源回路から内部回路への電源供給を予め定めた周期で間欠的に許可するための内部電源イネーブル信号CEB_GENを生成するための周期信号TIM2を発生する周期信号発生回路34と、通常動作モード及びスタンバイモードの何れかのモードを示すチップイネーブル信号CEBと、周期信号TIM2と、が入力され、入力されたチップイネーブル信号CEBがスタンバイモードである場合に、周期信号TIM2に同期した内部電源イネーブル信号CEB_GENを内部電源回路に出力する間欠内部電源イネーブル信号発生回路36と、を含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】製造技術の限界によりトランジスタの最小サイズが決まるため、ROMの高容量化にも限界があるという課題があった。

【解決手段】本発明の不揮発性半導体記憶装置は、EEPROMとマスクROMとを一体とした不揮発性半導体記憶装置であり、メモリトランジスタの電荷蓄積膜に蓄える電荷の有無によりデータを記憶するEEPROMと選択コンタクトホールの有無によりデータを記憶するマスクROMとを同一平面上に構成する。これにより、トランジスタサイズを小さくすることなく、ROM容量を増やすことが可能となる。

(もっと読む)

メモリデバイス内の漏洩電流の低減

メモリデバイスと、メモリデバイス内に漏洩電流を低減する方法とが開示される。メモリデバイスは、複数のビットラインを含むメモリコアアレイと、このメモリコアアレイとインターフェースするように構成された周辺論理回路とを含む。メモリデバイスはさらに、周辺論理回路をグランド電圧から分離するように構成されたフットスイッチと、プリチャージ電流経路をメモリコアアレイの複数のビットラインから分離するように構成されたヘッドスイッチとを含む。メモリデバイス内の漏洩電流は、フットスイッチおよびヘッドスイッチで行われる分離によって低減することができる。  (もっと読む)

(もっと読む)

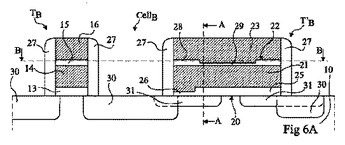

EEPROM構造を有する読出し専用メモリ

【解決手段】本発明は、少なくとも第1及び第2のメモリセル(CellB) を備えた不揮発性メモリ(M) に関しており、第1及び第2のメモリセルは、デュアルゲート(21,23) とデュアルゲート(21,23) 間に設けられた絶縁層(22)とを有する蓄積MOS トランジスタ(TB') を夫々備えている。第2のメモリセル(CellB) の蓄積トランジスタ(TB') の絶縁層(22)は、第1のメモリセルの蓄積トランジスタの絶縁層より絶縁性が低い少なくとも1つの部分(29)を有している。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】分割されたメモリアレイの端部について、ダミーパターンを配置することにより、面積増加要因となってしまう。

【解決手段】分割されたメモリアレイの端部Y1列に構成された回路をメモリセルトランジスタと同形状のブロック選択トランジスタBTで構成する。主ビット線GBと副ビット線LBとの接続部のパターンをメモリセル(Y2,Y3列)と同形状にすることで、パターンを均一にすることができメモリアレイ生成用のダミーパターンを不要とする。

(もっと読む)

半導体集積回路

【課題】不揮発性メモリ及び/又は揮発性メモリの不良箇所を救済可能な新たな半導体集積回路を提供する。

【解決手段】救済対象の不揮発性メモリと、前記不揮発性メモリをテストするテスト回路と、前記不揮発性メモリの不良箇所のアドレス及び正常データを保持することが可能な救済情報保持回路と、前記不揮発性メモリの不良箇所を救済するのに利用可能な救済メモリであって、メモリ回路又はロジック回路に設けられている救済メモリと、前記不揮発性メモリの不良箇所のアドレス及び正常データを前記救済情報保持回路から前記救済メモリに書き込み、前記不揮発性メモリの不良箇所からの読み出しを前記救済メモリからの読み出しに切り替える救済回路とを備えることを特徴とする半導体集積回路。

(もっと読む)

非線形導体メモリ

高速で低電力のメモリ素子は、非線形導体のアレイを備え、格納、アドレスデコーディング、および出力検出はすべて、ダイオードまたは他の非線形導体によって達成される。様々な実施形態において、行抵抗器および列抵抗器は、選択されていない行または列に接続されているときの高抵抗と、選択された行および列に接続されたときの低抵抗との間で切り替え可能である。電子メモリ素子は、情報回路と、複数の行スイッチと、複数の列スイッチと、選択回路とを含む。  (もっと読む)

(もっと読む)

半導体集積回路及びテスト方法

【課題】半導体記憶回路の不良が発生した位置を特定することができななかった。

【解決手段】半導体記憶回路(ROM100)と、半導体記憶回路に記憶するデータを指定する入力アドレスAin[i:0]を生成し、前記半導体記憶回路へ入力することを、開始アドレスAsta[i:0]から終了アドレスAstp[i:0]まで繰り返すアドレス入力部200と、開始アドレスと終了アドレスの範囲について、入力アドレスに対応して半導体記憶回路から読み出された出力データのうち、計数対象とする選択データを選択し、前記選択データの値を計数する出力データ処理部300と、チップ上に備える。

(もっと読む)

メモリ

【課題】消費電流(消費電力)が増加するのを抑制することが可能なメモリを提供する。

【解決手段】このメモリ(ダイオードROM)は、複数のワード線7と、複数のワード線7に交差するように配置される複数のビット線8と、ワード線7とビット線8とが交差する位置に配置されるメモリセル9と、ビット線8に接続されるトランジスタ42とを備え、トランジスタ42の電流駆動能力は、ビット線8が配置される位置によって異なるように構成されている。

(もっと読む)

半導体集積回路

【課題】メモリの自己テスト回路が組み込まれた半導体集積回路の故障診断を容易に実行できるようにする。

【解決手段】半導体集積回路50には、BIST回路1及びメモリカラー2が設けられる。メモリカラー2には、メモリ出力結果解析回路3及びメモリセル21が設けられる。BIST実行時では、不良検出された時点で検出された不良をメモリ出力結果解析回路3の取り込みレジスタ31に保存した状態でBIST動作が完了する。メモリ出力結果解析回路3の2入力OR回路OR1から出力される故障検出信号S109がBIST回路1の診断データ転送・保存回路16に入力されると、診断データ転送・保存回路16は動作を開始する。診断データ転送・保存回路16からシフトイネーブル信号S108が出力されると、取り込みレジスタ31に保存されているデータが診断データ転送・保存回路16に自動的に転送される。

(もっと読む)

電圧検出回路、電圧安定化回路、バッテリ状態監視回路及びバッテリ装置並びにトリミング方法

【課題】 回路構成の簡略化を図ると共に電圧検出精度の向上を図ることのできる電圧検出回路を提供する。

【解決手段】 可変抵抗回路と、基準電圧源と、中点電圧と基準電圧との大小関係が反転した場合に被測定電源の電圧が所定電圧に到達したことを示す比較回路と、発振回路と、分周回路と、トリミング用導通素子の切断前ではクロック信号を第1のスイッチング素子の制御端子に出力する一方、切断後には第1のスイッチング素子をオフ状態に維持させる信号を出力する第1の抵抗値設定回路と、トリミング用導通素子の切断前では分周信号を各々に対応する第2〜第nのスイッチング素子の制御端子に出力する一方、切断後には第2〜第nのスイッチング素子をオフ状態に維持させる信号を出力する第2〜第nの抵抗値設定回路と、テストモード時の場合は比較回路の出力信号を外部に出力するモード選択回路とを備える。

(もっと読む)

1 - 20 / 68

[ Back to top ]