Fターム[5B125CA01]の内容

リードオンリーメモリ (43,397) | 目的、効果 (6,321) | 高速化 (1,043)

Fターム[5B125CA01]に分類される特許

1 - 20 / 1,043

半導体記憶装置

暗号化演算装置を搭載する不揮発性半導体記憶装置

不揮発性半導体メモリおよびそのデータの読出し方法

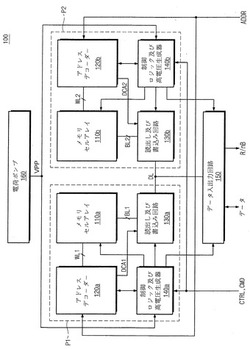

不揮発性メモリ装置及び不揮発性メモリ装置を制御するコントローラの動作方法

【課題】向上された動作速度を有する不揮発性メモリ装置及び不揮発性メモリ装置を制御するコントローラの動作方法を提供する。

【解決手段】本発明の不揮発性メモリ装置は、データのプログラム、読出し又は消去を遂行する第1プレーン、データのプログラム、読出し又は消去を遂行する第2プレーン、及び第1プレーン又は第2プレーンから共通バスを通じて伝送されるデータを外部へ出力し、外部から受信されるデータを、共通バスを通じて第1プレーン又は第2プレーンへ伝送するデータ入出力回路を含む。第1プレーンでプログラム、読出し又は消去が遂行される時、データ入出力回路は共通バスを通じて第2プレーンとデータを交換する。

(もっと読む)

不揮発性半導体記憶装置およびそのベリファイ制御方法

【課題】ベリファイに要する時間の短縮を図る。

【解決手段】ワード線WLとローカルビット線BLに接続された電気的に書き換え可能な複数のメモリセルMCを含むメモリセルアレイと、前記ローカルビット線に接続され前記各メモリセルのデータを反転してグローバルビット線GBLに出力する複数のローカルセンスアンプLSAと、前記複数のローカルセンスアンプの出力の論理和を演算するグローバルセンスアンプGBSAと、前記複数のローカルセンスアンプを動作させて該複数のローカルセンスアンプに接続された複数のメモリセルのデータを同時にベリファイする第1ベリファイと,前記複数のローカルセンスアンプを停止させて,該各ローカルセンスアンプに接続された前記ローカルビット線と前記グローバルビット線を直結して該複数のローカルセンスアンプに接続された複数のメモリセルのデータを同時にベリファイする第2ベリファイとを切り替えるアドレスデコーダと、を有する。

(もっと読む)

半導体装置

【課題】メモリセルの動作を従来よりも高速化できる半導体装置を提供する。

【解決手段】フローティングゲートFGとコントロールゲートCG、第1導電型ソース13s及び第1導電型ドレイン13dを有する第1導電型MOSトランジスタ13と、前記フローティングゲートFGと前記コントロールゲートCG、第2導電型ソース14s及び第2導電型ドレイン14dを有する第2導電型MOSトランジスタ14と、前記第1導電型ドレイン13d及び前記第2導電型ドレイン14dに接続される第1のソース/ドレイン11bと、第2のソース/ドレイン11aと、ゲートを有する選択トランジスタ11と、前記第1導電型ソースに接続される第1電源線VpLと、前記第2導電型ソースに接続される第2電源線VnLと、前記選択トランジスタ11の第2のソース/ドレイン11aに接続されるビット線BLと、前記選択トランジスタ11のゲートに接続されるワード線WLと、を有する。

(もっと読む)

半導体記憶装置

【課題】高速動作が可能な半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、制御可能な閾値に基づいてデータを記憶し、データの消去状態において正の閾値分布を有し、制御電極を有する複数のメモリセルを含む。複数のワード線(WL)は、複数のメモリセルの制御電極と選択的に電気的に接続され、メモリセルへのデータの書き込みに先立って特定の電位へと充電される。電圧生成回路(9)は、出力において電圧を出力し、出力の電位を放電する放電経路(DP2)を含む。接続回路(WF)は、電圧生成回路と特定のワード線とに選択的に接続され、接続されているワード線を特定の電位を供給する供給ノードに選択的に接続する。

(もっと読む)

メモリシステム及びそれの動作方法

【課題】動作速度及び電力消耗を減らすことができるメモリシステム及びそれの動作方法が提供される。

【解決手段】本発明の実施形態によるメモリシステムは不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、前記メモリ制御器は前記不揮発性メモリ装置から読み出されたデータのエラーの位置情報を含むエラーフラッグ情報を前記不揮発性メモリ装置へ提供する。

(もっと読む)

半導体記憶装置

【課題】インタリーブ動作を実行可能に構成され且つLMアドレススキャン動作を実行する半導体記憶装置における消費電力の削減、及び動作の高速化を図る。

【解決手段】複数のカラムのうちの少なくとも1つは、複数ビットのデータの書き込み動作の進行状況を示すLMフラグデータを記憶するためのLMカラムである。カラム制御回路の各々は、対応するメモリコアにLMカラムが存在するか否かを確認するためのLMアドレススキャン動作をする。そのLMアドレススキャン動作の結果をレジスタに格納し、その後の各種動作においては、前記データラッチ回路に保持されたデータが第1のデータである場合、そのメモリコアにおいて前記LMカラムからLMフラグデータを読み出す動作を実行する一方、前記レジスタに保持されたデータが第2のデータである場合、そのメモリコアにおいて前記LMカラムからLMフラグデータを読み出す動作を実行しない。

(もっと読む)

半導体記憶装置

【課題】読出速度が速い半導体記憶装置を提供する。

【解決手段】フラッシュメモリ3は、選択ビット線BLをプリチャージするプリチャージ回路45と、定電流源50と、電流検知型のセンスアンプ23と、選択ビット線BLがメモリアレイMA2に属する場合は、選択ビット線BLおよび定電流源50をそれぞれセンスアンプ23の入力ノードLBT,LBBに接続し、選択ビット線BLがメモリアレイMA3に属する場合は、選択ビット線BLおよび定電流源50を入力ノードLBB,LBTに接続する切換回路SWT2,SWB2,SWとを含む。したがって、ビット線BLのプリチャージとデータ読出を並列に実行できる。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体メモリの情報書き換え方法

【課題】不揮発性半導体メモリの書き換え時に、適切なパルス電圧および適切なパルス幅を備える信号を印加可能な不揮発性半導体記憶装置を提供することである。

【解決手段】本発明にかかる不揮発性半導体記憶装置は、記録されている情報を所定のパルス電圧および所定のパルス幅を備える信号を印加することで書き換え可能な不揮発性半導体メモリ11と、不揮発性半導体メモリ11の書き換えを制御する書き換え制御部12と、を備える。書き換え制御部12は、不揮発性半導体メモリの総書き換え回数に基づき仮のパルス電圧および仮のパルス幅の少なくとも一つを決定する。更に、決定された仮のパルス電圧および仮のパルス幅の少なくとも一つを不揮発性半導体メモリ11の温度に基づいて補正することで、書き換え時に不揮発性半導体メモリ11に印加する信号のパルス電圧およびパルス幅の少なくとも一つを決定する。

(もっと読む)

メモリ装置

【課題】、復号効率のよいメモリカード3を提供する。

【解決手段】メモリカード3は、複数のメモリセル13Dと、HB読み出し電圧とSB読み出し電圧とを、メモリセル13Dに印加する制御を行うCPUコア11と、閾値電圧をもとにLLRテーブルから取得したLLRに基づき軟判定復号を行うECC部1と、を具備し、第1のLLRテーブル20Aから取得したLLRに基づいた復号が失敗した場合に、最高電圧の第1のHB読み出し電圧H07を中心とする閾値電圧分布を測定し、閾値電圧分布の最小頻度電圧VMと第1のHB読み出し電圧H07との差である第1のシフト値ΔV1が「負」の場合には、第2のLLRテーブル20Bから取得したLLRに基づき復号を行い、第1のシフト値ΔV1が「正」の場合には、第3のLLRテーブル20Cから取得したLLRに基づき復号を行う。

(もっと読む)

高速OTP感知スキーム

【課題】不揮発性メモリアレイのための高速感知スキームを提供する。

【解決手段】メモリアレイは、ビット線をVSSなどの第1電圧レベルまで予備充電するための予備充電回路を備えた、相補形ビット線構成で配置された不揮発性メモリセルと、相補形ビット線対の基準ビット線に基準電荷を印加するための基準回路と、相補形ビット線対の間の電圧差を感知するためのビット線感知増幅器とを備えている。データビット線の電圧は、起動されたワード線に接続されたプログラム済みの不揮発性メモリセルがワード線電圧をデータビット線に結合すると変化する。

(もっと読む)

半導体記憶装置

【課題】消費電力を低減出来る半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、選択トランジスタ、メモリセル、ワード線、セレクトゲート線、ドライバ回路12、ロウデコーダ11−0、及び検知回路16を備える。ドライバ回路12は、第1電圧Vss,Vccを出力する。ロウデコーダ11−0内の第1転送トランジスタは、ワード線及びセレクトゲート線の各々に関連付けられ、ドライバ回路12から出力された第1電圧を、ワード線及びセレクトゲート線に転送する。検知回路16は、データの消去時において、ビット線及び/またはソース線に印加される第2電圧を検知して、検知結果に応じてフラグを生成する。ドライバ回路12は、フラグが生成されたことに応答して第1電圧の値を変更して、第1転送トランジスタをカットオフさせる。

(もっと読む)

不揮発性メモリ装置及びそのソフト判定読出し方法

【課題】不揮発性メモリ装置に対して、読出し/プログラム時間を短縮できる、向上された読出しスキームを提供する。

【解決手段】本発明の一特徴に係る不揮発性メモリ装置のソフト判定読出し方法は、ソフト判定読出し命令を受信し、選択されたワードラインへ読出し電圧を印加し、前記選択されたワードラインの選択されたメモリセルに各々連結されたビットラインをプリチャージし、前記ビットラインのプリチャージされた電圧及び前記選択されたワードラインに供給された読出し電圧は変化されない状態で、前記選択されたメモリセルの状態を連続的に感知することを含む。

(もっと読む)

半導体装置

【課題】適切に電源電圧を負荷回路に供給することができる、半導体装置を提供する。

【解決手段】電圧トランスファ20及びセンスノード配線33が設けられており、電圧トランスファ20は、各Sub−Arrayに応じて設けられたNMOSトランジスタTRにより、ノード32とノード30との間が接続される。電圧トランスファ20のトランジスタTRは、ソース及びドレインの一方が電源線31の各Sub−Arrayに応じた位置に接続されており、ソース及びドレインの他方がセンスノード配線33に接続されている。また、トランジスタTRのゲートには、対応するSub−Arrayのデコード信号A0〜AXが入力される。

(もっと読む)

不揮発性メモリ装置のデータリード方法、及びそれを行う装置

【課題】新たなリードパラメータで不揮発性メモリ装置をリードするリードリトライを行う方法、該方法を行う装置を提供する。

【解決手段】リードリトライ動作及び/またはその部属的なリードリトライ動作は、リードリトライ動作が保証(warranted)されるか否かを判断する前に初期化されるか、完了することができる。例えば、NANDフラッシュメモリ装置のページは、新たなリード電圧レベルをページのワードラインに印加して、リードリトライ動作でリードされうる。例えば、リードリトライ動作は、エラー訂正動作でターゲットページのデータの以前リードページのエラーを訂正不能と判断される前に、ターゲットページで行われる。

(もっと読む)

半導体記憶装置

【課題】インタリーブ動作を実行可能に構成された半導体記憶装置における更なる動作の高速化を図る。

【解決手段】複数のアドレス変換回路151a〜151dが、メモリコア11a〜11dの各々にそれぞれ設けられ、外部から供給される論理アドレスデータを物理アドレスデータに変換する。アドレス変換回路は、インタリーブ動作において第1のメモリコアが第2のメモリコアより先にアクセスされる場合には、論理アドレスデータを変換せず物理アドレスとして出力する一方、第2のメモリコアが第1のメモリコアより先にアクセスされる場合には、論理アドレスデータに所定値を加算したアドレスデータに対応する物理アドレスデータとして出力する。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】カラムブロックのデータラッチに対するデータの高速転送を可能にする。

【解決手段】半導体記憶装置1は、メモリセルアレイ2と、データバスDBと、転送制御部TC0〜TC2と、複数のカラムブロックC(0+4×i)〜C(3+4×i)と、カラムセレクタCSとを含む。カラムブロックおよびカラムセレクタはメモリセルアレイより下に形成される。データバスDBは複数のステージS0〜S3に分割される。転送制御部は複数のステージのそれぞれにデータが割り当てられるようにデータをシリアル転送する。カラムブロックは選択された場合にデータを一次記憶する。カラムセレクタCSはカラムブロックの中から、ステージごとにいずれかのカラムブロックを選択し、ステージごとに選択されたカラムブロックとの間でデータをパラレル転送する。データバスDBはカラムブロックの配列方向の一方の端側から他方の端側へ向かい、他方の端側で折り返す。

(もっと読む)

半導体記憶装置

【課題】ゲート面積に依存するトランジスタばらつきを抑制し、読み出し動作を高速化した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ロウ方向に延びるワード線WL、カラム方向に延びる複数のビット線BL0,BL1,BL2で構成されたビット線グループ、並びに、トランジスタからなりワード線及びビット線グループの交差部に設けられたメモリセル、を有するメモリセルアレイと、ビット線を介してメモリセルからデータを読む読み出し回路とを備え、メモリセルは、トランジスタのソース又はドレインを、ビット線グループに属する複数のビット線BL0,BL1,BL2のいずれとも接続しないか又はいずれか1本とだけ接続するかの異なる接続状態を有し、トランジスタのゲートとなるアクティブ領域AAは、ビット線グループの複数のビット線BL0,BL1,BL2の配置領域及び各ビット線間のスペースに連続的に形成されている

(もっと読む)

1 - 20 / 1,043

[ Back to top ]