Fターム[5B125DC12]の内容

リードオンリーメモリ (43,397) | 消去動作 (1,518) | 消去信号制御 (408) | 消去パルス電圧値制御 (267)

Fターム[5B125DC12]に分類される特許

1 - 20 / 267

半導体記憶装置

【課題】半導体記憶装置の回路面積を削減する。

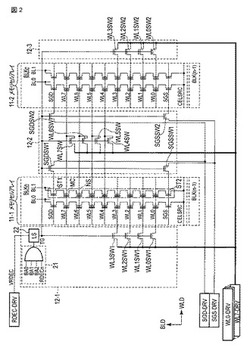

【解決手段】半導体記憶装置10は、複数のメモリセルを有する第1のブロックを含むメモリセルアレイ11−1と、複数のメモリセルを有する第2のブロックを含むメモリセルアレイ11−2と、メモリセルアレイ11−1及び11−2に配設された複数のワード線と、複数のワード線のそれぞれに電圧を転送する複数の転送ゲートSWを有するロウデコーダ12とを含む。第1のブロックに配設された複数のワード線は、第1及び第2のグループを有し、第2のブロックに配設された複数のワード線は、第3及び第4のグループを有する。上記第1及び第3のグループは、転送ゲートSWを共有する。

(もっと読む)

不揮発性プログラマブルスイッチ

【課題】セル面積の小さい不揮発性プログラマブルスイッチを提供する。

【解決手段】第1配線に接続される第1端子と第2配線に接続される第2端子と第3配線に接続される第3端子とを有する第1不揮発性メモリトランジスタと、第4配線に接続される第4端子と第2配線に接続される第5端子と第3配線に接続される第6端子とを有する第2不揮発性メモリトランジスタと、第2配線にゲート電極が接続されたパストランジスタと、を備え、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも高い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が増加し、第2不揮発性メモリトランジスタの閾値電圧が低下し、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも低い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が低下し、第2不揮発性メモリトランジスタの閾値電圧が増加する。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

半導体記憶装置

【課題】読出速度が速い半導体記憶装置を提供する。

【解決手段】フラッシュメモリ3は、選択ビット線BLをプリチャージするプリチャージ回路45と、定電流源50と、電流検知型のセンスアンプ23と、選択ビット線BLがメモリアレイMA2に属する場合は、選択ビット線BLおよび定電流源50をそれぞれセンスアンプ23の入力ノードLBT,LBBに接続し、選択ビット線BLがメモリアレイMA3に属する場合は、選択ビット線BLおよび定電流源50を入力ノードLBB,LBTに接続する切換回路SWT2,SWB2,SWとを含む。したがって、ビット線BLのプリチャージとデータ読出を並列に実行できる。

(もっと読む)

ページ消去を有する不揮発性半導体メモリ

【課題】NANDフラッシュメモリにおいてにおいて完全なフルブロックよりも小さい1つもしくはそれ以上のページ単位での消去を可能とする。

【解決手段】消去動作時、選択電圧は、パストランジスタを介して複数の選択されたワードラインの各々に印加され、非選択電圧は、パストランジスタを介して選択されたブロックの複数の非選択ワードラインの各々に印加される。基板電圧は、選択されたブロックの基板に印加される。共通選択電圧は、各選択されたワードラインに印加され、共通非選択電圧は、各非選択されたワードラインに印加される。選択および非選択電圧は、選択されたブロックのいずれかのワードラインに印加することができる。ページ消去ベリファイ動作は、複数の消去されたページと複数の消去されていないページをもつブロックに適用することができる。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体メモリの情報書き換え方法

【課題】不揮発性半導体メモリの書き換え時に、適切なパルス電圧および適切なパルス幅を備える信号を印加可能な不揮発性半導体記憶装置を提供することである。

【解決手段】本発明にかかる不揮発性半導体記憶装置は、記録されている情報を所定のパルス電圧および所定のパルス幅を備える信号を印加することで書き換え可能な不揮発性半導体メモリ11と、不揮発性半導体メモリ11の書き換えを制御する書き換え制御部12と、を備える。書き換え制御部12は、不揮発性半導体メモリの総書き換え回数に基づき仮のパルス電圧および仮のパルス幅の少なくとも一つを決定する。更に、決定された仮のパルス電圧および仮のパルス幅の少なくとも一つを不揮発性半導体メモリ11の温度に基づいて補正することで、書き換え時に不揮発性半導体メモリ11に印加する信号のパルス電圧およびパルス幅の少なくとも一つを決定する。

(もっと読む)

不揮発性半導体記憶装置

【課題】周辺回路の面積を縮小する。

【解決手段】

複数のメモリブロックの各々には、基板に対し垂直な方向に延びるように複数のメモリストリングが配列される。各メモリストリングは、複数のメモリトランジスタ及びダミートランジスタを直列接続してなる。ドレイン側選択ゲート線及びソース側選択ゲート線は、メモリブロックが選択されるときには転送トランジスタが導通することにより電圧を制御回路から供給される一方、メモリブロックが非選択とされるときは転送トランジスタが非導通状態となることによりフローティング状態とされる。ダミーワード線は、メモリブロックが選択されるときには第1の転送トランジスタが導通することにより制御回路から電圧を供給される一方、メモリブロックが非選択とされるときは第1の転送トランジスタとは別の第2の転送トランジスタにより電圧を供給される。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルに与える影響を緩和し、正確にデータを書き込むことのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は、メモリセルアレイと、選択メモリセルに書き込みパルス電圧を印加するとともに非選択メモリセルに中間電圧を印加する書き込み動作、書き込みベリファイ動作及び書き込みパルス電圧を第1のステップアップ値だけ上昇させるステップアップ動作を繰り返す制御を実行する制御部とを備える。制御部は、書き込みパルス電圧の印加回数が第1の回数より少ない第1期間では中間電圧を一定の値に保ち、書き込みパルス電圧の印加回数が第1の回数以上である第2期間では中間電圧を第2のステップアップ値だけ上昇させるようにステップアップ動作を制御し、且つ、第2のステップアップ値に基づき第1のステップアップ値を決定する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルの劣化による影響を考慮した読み出し動作を実行できる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は、メモリセルアレイと、読み出し動作及び書き込みベリファイ動作を制御する制御回路とを備える。制御回路は、第1の場合に、選択ワード線に印加する電圧を第1の書き込みベリファイ電圧又は第1の読み出し電圧に設定して、動作を行う。制御回路は、第1の場合よりもメモリセルの劣化が進んだ第2の場合に、選択ワード線に印加する電圧を第2の書き込みベリファイ電圧又は第2の読み出し電圧に設定して、動作を行う。制御回路は、第1の書き込みベリファイ電圧の最大値と第1の読み出し電圧の最大値との差を、第2の書き込みベリファイ電圧の最大値と第2の読み出し電圧の最大値との差よりも大きい値に設定する。

(もっと読む)

半導体記憶装置

【課題】書き込み/消去の繰り返しによる信頼性の低下を抑制することが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ウェル上にトンネル絶縁膜を介して形成された浮遊ゲートに蓄積する電荷量を制御することにより電気的にデータを書き換え可能な複数のメモリセルを備える。半導体記憶装置は、前記ウェル、及び前記浮遊ゲート上に絶縁膜を介して形成された制御ゲートに、電圧を印加する制御回路を備える。

前記メモリセルの消去動作において、前記制御回路は、第1の消去電圧が階段状に上昇する第1のパルス波を、前記ウェルに印加し、その後、第2の消去電圧の第2のパルス波を、前記ウェルに印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルの過消去を防止し、データの誤書き込みを低減した不揮発性半導体記憶装置を提供することを目的とする。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、メモリストリングに隣接するダミーに接続された第1配線、並びに、メモリセル毎に接続された第2配線を有するセルアレイを備え、ダミーセルに隣接する前記メモリセルを第1対象メモリセル、第1対象メモリセルに隣接する前記メモリセルを第2対象メモリセルとし、第1配線に印加される電圧を隣接第1配線電圧とし、第1対象メモリセルに接続された第2配線に印加される電圧を第2配線電圧とし、第2対象メモリセルに接続された第2配線に印加される電圧を第3配線電圧とした場合、駆動回路は、消去動作時において、第1配線電圧よりも第3配線電圧が小さい場合、第1配線電圧と第3配線電圧の差を第1配線電圧と第2配線電圧の差よりも小さくする。

(もっと読む)

双方向分割ゲートNANDフラッシュメモリ構造及びアレイ、そのプログラミング方法、消去方法及び読み出し方法、並びに、製造方法

【課題】NANDフラッシュメモリ構造において、各セルについてのライン数を削減して、不揮発性メモリデバイスのピッチを改善すること。

【解決手段】分割ゲートNANDフラッシュメモリ構造が、第1伝導型の半導体基板上に形成される。このNAND構造は、第2伝導型の第1領域と、基板内にこの第1領域から間隔をおいて配置されてこの第1領域との間にチャネル領域を定める、第2伝導型の第2領域と、を備える。各々が上記チャネル領域から絶縁された複数の浮動ゲートが、互いに間隔をおいて配置される。各々が上記チャネル領域から絶縁された複数の制御ゲートが、互いに間隔をおいて配置される。該制御ゲートの各々は、1対の浮動ゲートの間にあって該1対の浮動ゲートに容量的に接続される。各々が上記チャネル領域から絶縁された複数の選択ゲートが、互いに間隔をおいて配置される。該選択ゲートの各々は、1対の浮動ゲートの間にある。

(もっと読む)

フラッシュメモリ装置

【課題】低操作電圧および低電力消費量のフラッシュメモリを提供する。

【解決手段】フラッシュメモリ装置は、複数のメモリセルと、複数のプログラミング制御電圧生成器とを含む。各メモリセルは、制御エンドポイントを介してプログラミング制御電圧を受信し、プログラミング制御電圧に基づいてデータプログラミング操作を実行する。各プログラミング制御電圧生成器は、プリチャージ電圧送信機と、ポンピングキャパシタとを含む。プリチャージ電圧送信機は、第1期間中に、プリチャージイネーブル信号に基づいて、対応するメモリセルの制御エンドポイントにプリチャージ電圧を提供する。ポンプ電圧は、第2期間中にポンピングキャパシタに提供され、各メモリセルの制御エンドポイントでプログラミング制御電圧を生成する。

(もっと読む)

不揮発性メモリ装置、不揮発性メモリ装置の消去方法、不揮発性メモリ装置の動作方法、不揮発性メモリ装置を含むメモリシステム、メモリシステムの動作方法、不揮発性メモリ装置を含むメモリカード、及びソリッドステートドライブ

【課題】向上された信頼性を有する不揮発性メモリ装置、不揮発性メモリ装置の消去方法、不揮発性メモリ装置の動作方法、不揮発性メモリ装置を含むメモリシステム、及びメモリシステムの動作方法が提供される。

【解決手段】本発明の消去方法は複数のメモリセルに消去電圧を供給する段階、複数のメモリセルのワードラインに読出し電圧に読出し動作を遂行する段階、及び複数のメモリセルのワードラインの少なくとも1つのワードラインに消去検証電圧を利用して消去検証動作を遂行する段階を含む。消去検証電圧は読出し電圧より低い。

(もっと読む)

半導体記憶装置

【課題】メモリセルトランジスタからのデータの読み出しを高速化する。

【解決手段】メモリセルアレイ121は、メモリセルトランジスタ131及びローカルビット線LBLを含む第1回路部と、ローカルビット線LBLをグローバルビット線GBLに接続してメモリセルトランジスタ131に対する書き込み及び読み出しを行う第2回路部を含む。この第2回路部の、グローバルビット線GBLの電圧が印加されるnMOSトランジスタ151,152,154等に、耐圧を電源電圧としたものを用い、読み出しの高速化を図る。書き込みは、グローバルビット線GBLに電源電圧以下の電圧を印加し、ソース線SLに電源電圧よりも高い電圧を印加することで行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】読み出し動作を正確に実行する。

【解決手段】 制御回路は、メモリトランジスタの読み出し動作を実行する際、選択メモリトランジスタに接続される選択ワード線には、第1の電圧を印加する。選択メモリトランジスタを除く非選択メモリトランジスタに接続される非選択ワード線には、メモリトランジスタの保持データに拘わらずメモリトランジスタを導通させる第2の電圧を印加する。ビット線には、第3の電圧を印加する。ソース線のうち、選択メモリブロック中の前記選択メモリトランジスタが含まれるメモリストリングに接続される選択ソース線には第3の電圧より小さい第4の電圧を印加する。ソース線のうち、選択メモリブロック中の非選択のメモリストリングが接続される非選択ソース線には第3の電圧と略同一の第5の電圧を印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数のメモリストリングのうち特定のメモリストリングに対して選択的に消去動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】制御回路は、選択メモリストリング内の選択メモリトランジスタのデータを選択的に消去し、選択メモリストリング内の非選択メモリトランジスタ及び非選択メモリストリングに対する消去動作を禁止する。制御回路は、選択メモリストリングの半導体層をフローティング状態としたのち、選択メモリストリング内の非選択メモリトランジスタのゲートに接続される非選択ワード線に第1電圧を印加し、選択メモリストリング内の選択メモリトランジスタのゲートに接続される選択ワード線に前記第1電圧よりも小さい第2電圧を印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数のメモリストリングのうち特定のメモリストリングに対して選択的に消去動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、メモリセルアレイ、複数のメモリストリング、ドレイン側選択トランジスタ、ソース側選択トランジスタ、複数のワード線、複数のビット線、ソース線、ドレイン側選択ゲート線、ソース側選択ゲート線、及び制御回路を有する。制御回路は、選択したビット線に第1電圧を印加して当該ビット線に接続されたメモリストリングに対し消去動作を実行する一方、非選択としたビット線に第2電圧を印加して当該ビット線に接続されたメモリストリングに対し消去動作を禁止する。

(もっと読む)

バイト、ページおよびブロックに書き込むことができ、セルアレイ中で干渉を受けず分割が良好な特性を備え、新規のデコーダ設計とレイアウトの整合ユニットと技術を使用する単体式複合型不揮発メモリ

【課題】

バイト、ページおよびブロックで書き込むことができる新単体式複合型不揮発メモリを提供する。

【解決手段】

不揮発メモリアレイは、シングルトランジスタフラッシュメモリセルおよびダブルトランジスタEEPROMメモリセルを備え、同じ基板上に整合することができ、該不揮発メモリセルは低いカップリング係数の浮遊ゲートを備えて、メモリセル体積を減少でき、該浮遊ゲートをトンネル絶縁層の上に配置し、該浮遊ゲートは該ソース領域の辺縁および該ドレイン領域の辺縁に揃って、且つ該ソース領域辺縁および該ドレイン領域辺縁の幅に画定される幅を備え、該浮遊ゲートと該制御ゲートは50%より小さい相対的に小さなカップリング係数を備えて、該不揮発メモリセルを縮小できるようにし、該不揮発メモリセルのプログラムはチャネル熱電子方式で達成し、消去は高電圧でFNトンネル方式で達成する。

(もっと読む)

熱アシスト誘電体電荷トラップメモリ

【課題】

誘電体電荷トラップメモリの動作速度及び/又は耐久性を向上させる技術を提供する。

【解決手段】

メモリデバイスは、ワードライン及びビットラインを含む誘電体電荷トラップ構造メモリセルのアレイを含む。該アレイに、読み出し、プログラム及び消去の動作を制御するように構成された制御回路が結合される。コントローラは、該アレイのメモリセル内の誘電体電荷トラップ構造を熱アニールする支援回路を備えるように構成される。熱アニールのための熱を誘起するために、ワードラインドライバ及び前記ワードライン終端回路を用いて、ワードラインに電流を誘起することができる。熱アニールは、サイクルダメージからの回復のために、通常動作とインターリーブされて適用されることが可能である。また、熱アニールは、消去のようなミッション機能中に適用されることもでき、それにより該機能の性能を向上させ得る。

(もっと読む)

1 - 20 / 267

[ Back to top ]