Fターム[5B125ED10]の内容

リードオンリーメモリ (43,397) | ビット線まわり (1,351) | ビット線まわり (1,351) | 列選択回路 (282)

Fターム[5B125ED10]に分類される特許

1 - 20 / 282

半導体記憶装置

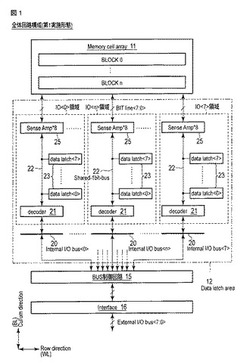

【課題】微細化に対して有利な半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、複数のメモリセルが配置されるメモリセルアレイ11と、前記複数のメモリセルのデータをラッチし、前記メモリセルアレイのデータの入力または出力(I/O)ごとに分割して配置される複数のアドレス領域(IO<0>領域〜IO<7>領域)と、前記複数のアドレス領域に対応して配置され、それぞれが前記複数のアドレス領域と電気的に直列に接続される内部バス配線20と、前記内部バス配線のデータ転送を制御する制御回路15とを具備する。

(もっと読む)

半導体記憶装置

【課題】インタリーブ動作を実行可能に構成され且つLMアドレススキャン動作を実行する半導体記憶装置における消費電力の削減、及び動作の高速化を図る。

【解決手段】複数のカラムのうちの少なくとも1つは、複数ビットのデータの書き込み動作の進行状況を示すLMフラグデータを記憶するためのLMカラムである。カラム制御回路の各々は、対応するメモリコアにLMカラムが存在するか否かを確認するためのLMアドレススキャン動作をする。そのLMアドレススキャン動作の結果をレジスタに格納し、その後の各種動作においては、前記データラッチ回路に保持されたデータが第1のデータである場合、そのメモリコアにおいて前記LMカラムからLMフラグデータを読み出す動作を実行する一方、前記レジスタに保持されたデータが第2のデータである場合、そのメモリコアにおいて前記LMカラムからLMフラグデータを読み出す動作を実行しない。

(もっと読む)

半導体記憶装置

【課題】読出速度が速い半導体記憶装置を提供する。

【解決手段】フラッシュメモリ3は、選択ビット線BLをプリチャージするプリチャージ回路45と、定電流源50と、電流検知型のセンスアンプ23と、選択ビット線BLがメモリアレイMA2に属する場合は、選択ビット線BLおよび定電流源50をそれぞれセンスアンプ23の入力ノードLBT,LBBに接続し、選択ビット線BLがメモリアレイMA3に属する場合は、選択ビット線BLおよび定電流源50を入力ノードLBB,LBTに接続する切換回路SWT2,SWB2,SWとを含む。したがって、ビット線BLのプリチャージとデータ読出を並列に実行できる。

(もっと読む)

不揮発性半導体記憶装置

【課題】高集積化を図ることができる不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、セルの書き込みにおいて、制御装置は複数の第2の選択ゲートトランジスタに第1電位を与えた後、第1電位よりも低い第2電位を与える。複数のビット線のうち、書き込み不十分のセルに第3電位を与え、書き込み終了に間近のセルに第3電位より高い第4電位を与え、書き込みが終わったセルに第4電位より高い第5電位を与える。制御装置は、第2電位を与えた後、複数のワード線のうち選択されたワード線に書き込み電位を与え、第1電位は、第2の選択ゲートトランジスタをオンすることにより第3電位をNANDストリングに転送する電位であり、第2電位は、第3電位をNANDストリングに転送した後、前記第2の選択ゲートトランジスタをオフする電位である。

(もっと読む)

不揮発性半導体記憶装置

【課題】高速で動作し得る不揮発性半導体記憶装置を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタMTとを有するメモリセルMCがマトリクス状に配列されて成るメモリセルアレイ10と、ビット線BLの電位を制御する列デコーダ12と、第1のワード線WL1の電位を制御する電圧印加回路14と、第2のワード線WL2の電位を制御する第1の行デコーダ16と、ソース線SLの電位を制御する第2の行デコーダ18とを有し、列デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されており、第1の行デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されている。ビット線と第2のワード線とが高速で制御され得るため、メモリセルトランジスタに書き込まれた情報を高速で読み出すことができる。

(もっと読む)

半導体記憶装置

【課題】 ビット線選択回路の小型化を図るとともにビット線の駆動時間を高速に行うことができる半導体記憶装置を提供する。

【解決手段】 フラッシュメモリ10は、セルユニットNUが行列状に複数配置されたメモリアレイ100と、セルユニットNUに接続されたビット線を選択するビット線選択回路200とを有する。ビット線選択回路200は、偶数ビット線GBL_e、奇数ビット線GBL_oをセンス回路に選択的に接続するための選択トランジスタSEL_e、SEL_o、BLSを含む第1の選択部210と、偶数ビット線GBL_eおよび奇数ビット線GBL_oに選択的にバイアス電圧を印加するためのバイアストランジスタYSEL_e、YSEL_oとを含む第2の選択部220とを有する。第2の選択部220のバイアストランジスタYSEL_e、YSEL_oは、記憶素子と共通のウエル内に形成される。

(もっと読む)

半導体記憶装置及びその試験方法

【課題】ローデコーダ側に配置される転送トランジスタの特性評価を実施する。

【解決手段】一つの実施形態によれば、半導体記憶装置は、切り替え部、第一の転送トランジスタ、第一のトランジスタ、及び第二のトランジスタが設けられる。切り替え部が第一の状態のときに第一及び第二のトランジスタがオフし、第一の転送トランジスタがオンし、切り替え部が第二の状態のとき第一及び第二のトランジスタがオンする。

(もっと読む)

不揮発性メモリ装置、不揮発性メモリ装置の消去方法、不揮発性メモリ装置の動作方法、不揮発性メモリ装置を含むメモリシステム、メモリシステムの動作方法、不揮発性メモリ装置を含むメモリカード、及びソリッドステートドライブ

【課題】向上された信頼性を有する不揮発性メモリ装置、不揮発性メモリ装置の消去方法、不揮発性メモリ装置の動作方法、不揮発性メモリ装置を含むメモリシステム、及びメモリシステムの動作方法が提供される。

【解決手段】本発明の消去方法は複数のメモリセルに消去電圧を供給する段階、複数のメモリセルのワードラインに読出し電圧に読出し動作を遂行する段階、及び複数のメモリセルのワードラインの少なくとも1つのワードラインに消去検証電圧を利用して消去検証動作を遂行する段階を含む。消去検証電圧は読出し電圧より低い。

(もっと読む)

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼でき、非常に小型の3次元集積回路メモリ用の構造を低い製造コストで提供する。

【解決手段】3次元アレイは第1の端部と第2の端部を含む2つの端部を有し、第1の端部と第2の端部の一方はビット線BLに接続され、第1の端部と第2の端部の他方はソース線CSLに接続される不揮発性メモリセルのNANDストリングのスタック1412、1413、1414と、ビット線BL及びソース線SLの一方をメモリセルのストリング1412、1413、1414に接続させるダイオード1492を有する。

(もっと読む)

ページバッファとそれを含む不揮発性メモリ装置

【課題】ページバッファとそれを含む不揮発性メモリ装置を提供する。

【解決手段】不揮発性メモリ装置はメモリセルアレイとページバッファを含む。ページバッファはメモリセルアレイのビットラインに選択的に連結される感知ノードと、感知ノードに選択的に連結される第1メインラッチと、第2メインラッチを含むメインラッチ回路と、第1及び第2メインラッチノードに選択的に連結されるラッチ入力ノードを含む。ページバッファ回路はまた、第1及び第2キャッシュラッチノードを含むキャッシュラッチ回路と、ラッチ入力ノードに第2キャッシュラッチノードを選択的に連結するスィッチ回路と、ラッチ入力ノードと参照電位との間に連結された共有感知回路を含む。ここで、共有感知回路は感知ノードの電圧及び第1キャッシュラッチノードの電圧に回答して、ラッチ入力ノードを参照電位に選択的に連結する。

(もっと読む)

不揮発性半導体記憶装置

【課題】データ読み出しの処理時間を短縮する共にデータの信頼性を向上させた不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、複数のNANDストリングを有するメモリセルアレイと、複数のメモリセルのうちデータ読み出し対象となる着目メモリセルからデータを読み出す読み出しシーケンスにおいて、複数のワード線のうち着目メモリセルに接続された選択ワード線に隣接する隣接ワード線に一定の読み出しパス電圧を供給し、その間に、ビット線に現れる着目メモリセルの状況に応じた複数の電気的物理量を検知する主読み出し動作を実行する読み出し回路とを備える。

(もっと読む)

半導体記憶装置

【課題】データの読み出し速度を向上する。

【解決手段】半導体記憶装置1は、メモリセルアレー1aと、コラム線1bと、第1および第2のデータ線1d,1eと、データの読み出し時には、コラム線1bに第1および第2のデータ線1d,1eの一方を選択して接続し、データの書き込み時には、コラム線1bに第1および第2のデータ線1d,1eを接続するスイッチ1cと、第1および第2のデータ線1d,1eに接続された読み出し回路1fと、第1および第2のデータ線1d,1eに接続された書き込み回路1gと、を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去動作の実行単位を小さくすると共に正確な読出動作を実現可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、複数のメモリストリング、複数のメモリブロック、複数のソース線、及び制御回路を有する。複数のメモリストリングは、積層された複数のメモリトランジスタを含む。複数のメモリブロックは、複数のメモリストリングを含む。複数のソース線は、複数のメモリストリングそれぞれに接続される。制御回路は、複数のソース線に供給する信号を制御する。複数のメモリストリングは、各々、半導体層、電荷蓄積層、及び導電層を有する。制御回路は、メモリトランジスタに対する動作の種類に基づいて、複数のソース線を電気的に共通接続するか否かを切り替える。

(もっと読む)

半導体記憶装置

【課題】メモリセルトランジスタからのデータの読み出しを高速化する。

【解決手段】メモリセルアレイ121は、メモリセルトランジスタ131及びローカルビット線LBLを含む第1回路部と、ローカルビット線LBLをグローバルビット線GBLに接続してメモリセルトランジスタ131に対する書き込み及び読み出しを行う第2回路部を含む。この第2回路部の、グローバルビット線GBLの電圧が印加されるnMOSトランジスタ151,152,154等に、耐圧を電源電圧としたものを用い、読み出しの高速化を図る。書き込みは、グローバルビット線GBLに電源電圧以下の電圧を印加し、ソース線SLに電源電圧よりも高い電圧を印加することで行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数のメモリストリングのうち特定のメモリストリングに対して選択的に消去動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】制御回路は、選択メモリストリング内の選択メモリトランジスタのデータを選択的に消去し、選択メモリストリング内の非選択メモリトランジスタ及び非選択メモリストリングに対する消去動作を禁止する。制御回路は、選択メモリストリングの半導体層をフローティング状態としたのち、選択メモリストリング内の非選択メモリトランジスタのゲートに接続される非選択ワード線に第1電圧を印加し、選択メモリストリング内の選択メモリトランジスタのゲートに接続される選択ワード線に前記第1電圧よりも小さい第2電圧を印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数のメモリストリングのうち特定のメモリストリングに対して選択的に消去動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、メモリセルアレイ、複数のメモリストリング、ドレイン側選択トランジスタ、ソース側選択トランジスタ、複数のワード線、複数のビット線、ソース線、ドレイン側選択ゲート線、ソース側選択ゲート線、及び制御回路を有する。制御回路は、選択したビット線に第1電圧を印加して当該ビット線に接続されたメモリストリングに対し消去動作を実行する一方、非選択としたビット線に第2電圧を印加して当該ビット線に接続されたメモリストリングに対し消去動作を禁止する。

(もっと読む)

多値ROMセル及び半導体装置

【課題】集積度が高く、製造ばらつきの影響が小さく、製造歩留まりの高い多値ROMセルを提供する。

【解決手段】多値ROMセルは、ROMセルトランジスタTrと、複数のビット線BT1〜BT3と、第1金属配線31〜44とを具備している。ROMセルトランジスタTrは、基板表面の領域に設けられている。複数のビット線BT1〜BT3は、基板表面の上方に設けられ、Y方向に伸び、Z方向に並んで配置されている。第1金属配線31〜44は、ROMセルトランジスタTrのソース・ドレイン22の一方に接続され、複数のビット線BT1〜BT3の各々の近傍にまで連なる。第1金属配線31〜44は、複数のビット線BT1〜BT3のうちのいずれかに接続されているか、又は、いずれにも接続されていない。

(もっと読む)

半導体記憶装置

【課題】リファレンスセルを有する半導体記憶装置でのデータ読み出しにおけるアクセス速度を向上することができる半導体記憶装置を提供することを課題とする。

【解決手段】リファレンスセル側において、リファレンスセルが接続されたビット線の一端をグローバルビット線に接続し、他端を負荷用ローカルビット線に接続することで、リファレンスセルが接続されたビット線及び負荷用ローカルビット線をグローバルビット線に対して直列に接続し、センスアンプからみたメモリセル側及びリファレンスセル側の負荷を揃え、データ読み出し動作のプリチャージにおける電位変化を過渡状態においても等しくなるようにする。所定のレベルに達したらプリチャージを終了しセンス動作を行えるので、プリチャージに要する時間を短縮でき、データ読み出しに係るアクセスタイムが短縮される。

(もっと読む)

半導体メモリ

【課題】メモリの動作特性の向上を図る。

【解決手段】半導体メモリは、ロウ方向及びカラム方向に沿って配列され、複数のしきい値にそれぞれ対応するデータを記憶する複数のメモリセルを含むメモリセルアレイ1と、メモリセルアレイ1のロウを制御するロウ制御回路2と、外部からのアドレス信号に対応するポインタPTに基づいてメモリセルアレイ1のカラムを制御するための信号CNTを生成する制御ユニット70を有するカラム制御回路3と、を含む。

(もっと読む)

半導体記憶装置

【課題】VGA型半導体記憶装置のビット線ディスチャージ時の消費電力を低減する。

【解決手段】ビット線BL[0]〜[7]のディスチャージ時に、ビット線同士をビット線接続スイッチ00〜03で接続し、複数のビット線選択トランジスタ30〜37のうち一部のビット線選択トランジスタ30,32,34,36のみを導通させ、主ビット線MBL[0]及びディスチャージトランジスタ40を介して一部のビット線BL[0],[2],[4],[6]のみを接地電源に接続し、他のビット線BL[1],[3],[5],[7]はビット線接続スイッチ00〜03を介してディスチャージする。

(もっと読む)

1 - 20 / 282

[ Back to top ]