Fターム[5B125EK04]の内容

リードオンリーメモリ (43,397) | 外部接続構成、外部出力情報 (1,198) | ライター (35)

Fターム[5B125EK04]に分類される特許

1 - 20 / 35

プログラム書込システム

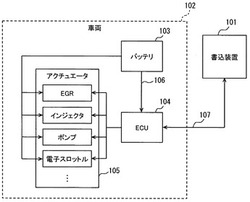

【課題】バッテリ電圧が異なる車両の制御対象機器を制御するための、同じハードウエア構成を備えた電子制御装置に対して、正しい制御プログラム以外の書き込みを防止すること。

【解決手段】ECU104が、書込装置101から制御プログラムの提供を受けたときに、検出されたバッテリ電圧VVと、制御プログラム内の使用電圧情報110から取得した使用電圧VSとに基づき、制御プログラムの正誤を判定する。そして、正しい制御プログラムではないと判定した場合、制御プログラムのフラッシュROMへの書込処理を中止する。

(もっと読む)

データ書き込み装置およびデータ書き込み方法

【課題】全てのROMに共通するデータと個々のROMごとに異なるデータとを1つの工程で書き込むことができ、また、書き込みデータの秘匿性を保つことができるデータ書き込み装置およびデータ書き込み方法を提供する。

【解決手段】データ書き込み装置10は、経路切り替え手段11とデータ書き込み手段12とデータ格納手段13とを備え、経路切り替え手段11は、制御装置から受信した共通データをデータ格納手段13に記憶させ、制御装置から共通データの書き込み開始の要求があった場合は、データ格納手段13から読み出した共通データをデータ書き込み手段12に出力し、制御装置から個別データの書き込み開始の要求があった場合は、制御装置から受信した個別データをデータ書き込み手段12に出力し、データ書き込み手段12は、経路切り替え手段11から入力されたデータをデータ書き換え可能な記憶素子の所定領域に書き込む。

(もっと読む)

半導体集積回路及び書込処理方法

【課題】複数種類の外部不揮発性記憶装置に対して、それぞれに適した書込パラメータを自動選択することにより、書込処理が可能な半導体集積回路を提供すること。

【解決手段】複数種類の外部不揮発性記憶装置のそれぞれに対して書込処理を行なうための複数種類の書込パラメータが格納された内部不揮発性記憶回路102と、接続された外部不揮発性記憶装置200の識別情報を取得し、識別情報に基づいて複数種類の書込パラメータから接続された外部不揮発性記憶装置200に適した1つの書込パラメータを選択し、選択された書込パラメータを用いて接続された外部不揮発性記憶装置200に対して書込処理を行なう制御回路101と、を備えた半導体集積回路100。

(もっと読む)

NANDフラッシュメモリおよびNANDフラッシュメモリへのデータ書込方法

【課題】ソケットとの接触不良によるインバリッドマークへの意図しない書き込みを防止する。

【解決手段】I/Oライン8−1〜8−Nにスイッチ11−1〜11−Nを介して抵抗(プルアップ抵抗)12−1〜12−Nの一端を接続し、プルアップ抵抗12−1〜12−Nの他端を所定の電源電位Vccに接続する。コントローラ1に、スイッチ11−1〜11−NのON/OFFモードを設定するROM書きモード設定用レジスタ10を設け、ソケットを使用してのメモリアレイ2へのプログラムの書き込み時に、スイッチ11−1〜11−NをONモードとする。

(もっと読む)

データ書込装置、及び、データ書込方法

【課題】CPUはSRAM異常が自発的に行う学習又は受動的に行う学習の何れで発生したかを判断し受動的に行う学習で発生した場合に学習結果を表示させる技術を提供する。

【解決手段】

電源第1系統より電力を受給し、不揮発性の第1記憶部にデータを書込む装置は、書込要求判定データを発生源に応じ記憶し、揮発性の第2記憶部に書込要求判定データが書込まれている場合に電源第2系統より電力を受給し、書込対象データと書込要因とを記憶する第3記憶部に記憶された書込対象データを第1記憶部に書込み、第3記憶部に記憶された書込要因がユーザ受付の場合に第1記憶部への書込対象データの書込結果を表示し、第3記憶部がデータ異常で初期化された場合に第2記憶部にユーザ受付を示す書込要求判定データが記憶されるときは第1記憶部への書込対象データの書込結果を表示する。従って制御結果を適切に表示できる。

(もっと読む)

データ書込装置、及び、データ書込方法

【課題】ユーザに制御結果を誤解させない学習制御の技術を提供する。

【解決手段】車両の電源から導かれる第1系統より電力の供給を受け、不揮発性の第1記憶部にデータを書き込むデータ書込装置は、書込要求に応答して、電源から導かれる第2系統より電力の供給を受け、データを記憶可能な第2記憶部に記憶された書き込みの対象データを、第1記憶部に書き込み、主電源からの電力供給が停止した後に開始する際は所定の初期表示を行う表示装置に、第1記憶部へのデータの書込結果を表示させ、第1記憶部に書込む際に、第1系統からの電力供給が停止された後に開始された場合は、第2記憶部に記憶された対象データを第1記憶部に書き込む第2書込手段は、書込要求を制御手段から受け付けたときに有効化し、書込要求をユーザから受け付けたときに有効化しない。このため、ユーザに制御結果を誤解させない学習制御を実現することができる。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において、書き換え回数の増加に伴う特性変化に応じてセルからデータを読み出す際の閾値を調整する。

【解決手段】電圧の保持状態によってデータを記憶する複数のセルに対し、電圧の保持状態を変化させることでデータの書き込み若しくはデータの消去を行い、書き込み若しくは消去した際のデータの電圧値に応じて、閾値を更新させる。また、複数の閾値のうち、前記セルにデータを書き込んだ状態で読出しエラーが無く読み出せた閾値と前記セルのデータを消去した状態で読出しエラーが無く読み出せた閾値の中間値に最も近い閾値に更新する。

(もっと読む)

不揮発性記憶装置の制御方法、および不揮発性記憶装置

【課題】ベリファイ動作において、内部降圧電源回路から出力される内部降圧電圧を調整してベリファイ対象のメモリセルからデータを読み出すことにより、メモリセルの書き換え状態の印加電圧依存性を検出することが可能な不揮発性記憶装置の制御方法、および不揮発性記憶装置を提供すること。

【解決手段】内部降圧電源回路が搭載される不揮発性記憶装置に関して、メモリセルに対して書き換え用のバイアスを印加し、書き換え用バイアスの印加の後、内部降圧電源回路から出力される内部降圧電圧の降圧電圧値を調整する。内部降圧電圧の降圧電圧値が調整された状態で、書き換えられたメモリセルの内容を読み出してベリファイする。

(もっと読む)

電子回路

【課題】電子回路において、プリント回路基板を大型化させることなく、複数個の不揮発性メモリにそれぞれ別のデータを書き込めるようにする。

【解決手段】単一のコネクタ4と、第1系統の信号伝送ライン10と、第2系統の信号伝送ライン20を設ける。信号伝送ライン10は、第1トランジスタ11、12のスイッチング動作により、コネクタ4を介してデータ送信装置100から送信されたデータをEEPROM2に伝送する。信号伝送ライン20は、第2トランジスタ21、22のスイッチング動作により、コネクタ4を介してデータ送信装置100から送信されたデータをシリアルフラッシュメモリ3に伝送する。制御部5は、第1トランジスタ11、12及び第2トランジスタ21、22を排他的にオン/オフさせ、EEPROM2又はシリアルフラッシュメモリ3に排他的に書き込む。

(もっと読む)

メモリコントローラ、メモリシステム、及びメモリデバイスへのデータの書込方法

【課題】メモリデバイスへの書き込み動作にかかる時間を従来よりも短縮するメモリコントローラを提供する。

【解決手段】メモリコントローラ10には、内蔵する揮発性メモリ22a、22bから対応する不揮発性メモリ21a、21bへのデータのコピーが可能になっているメモリデバイス20a、20bが接続される。メモリコントローラ10からメモリデバイス20a、20bの揮発性メモリ22a、22bにデータが書き込まれると、メモリデバイス20a、20b内で、揮発性メモリ22a、22bから不揮発性メモリ21a、21bにデータのコピーが行われる。メモリコントローラ10は、不揮発性メモリ21aに書き込まれたデータを、揮発性メモリ22bに書き込まれたデータを用いてベリファイする。

(もっと読む)

再書き込み装置及びプログラム

【課題】フラッシュメモリ等の記憶媒体に記憶されているデータのリフレッシュ処理が中断してしまう可能性を低減することが可能な再書き込み装置を提供する。

【解決手段】フラッシュメモリに記憶されているファイル毎に、データリテンションによりデータが破壊されてしまう危険度を算出し(S305)、算出された危険度の高さに応じて設けられているリフレッシュ処理開始条件が成立したか否かを判定する(S340、S350)。リフレッシュ処理開始条件が成立した場合、リフレッシュ処理を最後まで実行可能である可能性が高いとみなし、リフレッシュ処理を実行する(S355)。

(もっと読む)

マイクロコンピュータ

【課題】マイクロコンピュータに内蔵されたフラッシュメモリの使い勝手を向上させる。

【解決手段】本発明のマイクロコンピュータは、CPUとI/Oポートとフラッシュメモリとランダムアクセスメモリとを単一の半導体チップに構成される。フラッシュメモリは、複数の一括消去可能な記憶領域に分割され、書換え制御プログラムと転送制御プログラムとを格納し、消去・書込み等の動作状態を設定するコントロールレジスタを有する。コントロールレジスタは、消去動作を指示するビット、書込み動作を指示するビット、ベリファイ動作を指示するビット、および消去対象となる記憶領域を指定するビットとを有し、CPUによって制御される。CPUは、転送制御プログラムを実行して、書換え制御プログラムを前記ランダムアクセスメモリへ転送し、さらに、転送された前記書換え制御プログラムを実行して、用意されたデータをフラッシュメモリへ書き込む。

(もっと読む)

制御プログラム及びマイクロコンピュータ

【課題】EEPROMライタを有効に活用する。

【解決手段】マイコン1は、EEPROMライタ2からEEPROM通信のプロトコルを介して、情報を書き込む旨の信号である書込指令信号を受け付けて、この書込指令信号が受け付けられた場合に、EEPROMライタ2からEEPROM通信のプロトコルを介して書き込み対象の情報を受信する情報受信部12と、情報受信部12によって受信された書き込み対象の情報を、フラッシュメモリ11に書き込む書込実行部13と、を備えている。

(もっと読む)

不揮発性メモリへの書込み方法とこれに用いる電気機器及びROMライタ

【課題】 マイコンの仕様に関係なく使うことのできる汎用性の高いROMライタと電気機器とこれらを用いた書込み方法を提供する。

【解決手段】 本発明に係る不揮発性メモリへの書込み方法は、書込み制御端子が所定電圧にプルダウン若しくはプルアップされた時にデータの書換えが可能となる不揮発性メモリを内蔵した電気機器と、この不揮発性メモリにデータの書込みを行うROMライタとからなる書き込み方法であって、前記電気機器は、前記所定電圧を発生する発生回路を備えると共に、前記ROMライタは、前記発生回路による所定電圧を前記書込み制御端子に繋げる手段を備えたものである。

(もっと読む)

メモリ試験装置

【課題】フラッシュメモリのようにブロック機能を持つメモリを短時間にテストすることができるメモリ試験装置を提供する。

【解決手段】被試験メモリMUTの全ビットの不良を格納できる不良解析メモリAFMに加えて、被試験メモリが持つブロックの数に対応する記憶容量を持つ第1バッドブロックメモリBBMと第2バッドブロックメモリCFMとを設け、第1バッドブロックメモリには初期テストの結果を格納し、初期テストの結果をマスクデータとして利用してバッドブロックはマスクして機能テストを省略し、正常なブロックだけを機能テストし、この機能テストの結果を第2バッドブロックメモリに格納し、この第2バッドブロックメモリにバッドブロックデータが格納されているブロックだけを救済可能か否かを判定処理する。

(もっと読む)

NAND型フラッシュメモリの制御システム

【課題】NAND型フラッシュメモリコントローラを種々のNAND型フラッシュメモリに対応可能とし、機能やスペックを落とさずに制御基板を長いライフサイクルで使えるようにする。

【解決手段】システム電源をONして、メインCPUを起動させると共に、NAND型フラッシュメモリコントローラ12を起動させる。NAND型フラッシュメモリコントローラ12の起動においては、NAND型フラッシュメモリ13からNAND ID20を読み込んで、メモリアクセスに必要な個別仕様を設定すると共に、コンフィグデータ21を読み込んで、メモリアクセス時におけるスピード(アクセスタイム)を設定する。そして、NAND型フラッシュメモリ13のユーザデータ22をDRAMへコピーして、メインCPUがメインプログラムを実行する。

(もっと読む)

電子部品、基板、データ書き込みシステム、電源制御方法

【課題】 書き込み装置の書き込み電源のみで書き込みを可能とする。

【解決手段】内部電源をオフになると、書き込み電源領域410、および、内部電源領域420には、内部電源が供給されず、電源スイッチ450が、オフになり、書き込み電源領域410と内部電源領域420とは電源パターンが不導通になる。接続コネクタ500からの書き込み電源をオンになると、書き込み電源が、データ格納回路411、書き込み制御回路412に供給される。ここで、電源スイッチ450がオフなので、書き込み電源は、内部電源領域420には、供給されない。接続コネクタ500、書き込み用ピン403を経由し、書き込み制御情報、書き込みデータが書き込み制御回路412に入力される。書き込み制御回路412は、書き込み制御情報に基づき、書き込みデータをデータ格納回路411に書き込む。

(もっと読む)

不揮発性メモリ・モジュール、半導体集積回路チップ、電子回路ユニット

【課題】 チップ/モジュールの面積を小さくして、製品単価を低くすること。

【解決手段】 不揮発性メモリ・モジュール(100A)は、メモリセル(102)と、外部クロック信号(SCLK)に同期して、外部のトリミングデータ書込み回路(500)で生成された昇圧回路(VPP)に基づいてトリミング情報をメモリセル(102)に書き込む書込制御回路(110A)とを有する。

(もっと読む)

記憶装置及びデータ出力回路

【課題】供給側での製造処理を簡易にしつつ、ユーザ側から所望された仕様を満足するメモリを供給する。

【解決手段】メモリコア22のアドレス空間200Cは、情報格納領域201と、コード領域202と、非書き込み領域203とを有している。情報格納領域201にはその第1部分201aにおいて非書き込み領域情報WRGNが、第2部分201bにおいて固定値FXVLが、それぞれ書き込まれている。コード領域202にはプログラムコードCODEが書き込まれている。非書き込み領域情報WRGNは非書き込み領域203の位置を示し、固定値FXVLは非書き込み領域203において書き込まれるべき固定された値を示している。ROM2は、データ選定部213によってメモリコア22から直接に得られた読み出し原データDTRと固定値FXVLとを選択して、読み出しデータDTCとして出力する。

(もっと読む)

半導体集積回路装置のデータ記録方式

【課題】 大規模な記録容量とともに、高速なデータ書き込み、並びにデータ読み出しを実現する不揮発性半導体メモリを有した半導体集積回路装置のデータ記録方式を提供する。

【解決手段】 二値領域55と多値領域57とを含むメモリ領域51を備え、ホスト機器が送信したデータ(DATA1〜DATA3)を、二値領域55に二値データで記録し、二値領域55に記録したデータ(DATA1〜DATA3)を、ホスト機器からのアクセスが無いときに多値領域57に多値データでコピーする。

(もっと読む)

1 - 20 / 35

[ Back to top ]