Fターム[5C080DD09]の内容

陰極線管以外の表示装置の制御 (251,852) | 目的、効果 (44,953) | 誤動作防止 (2,465)

Fターム[5C080DD09]の下位に属するFターム

クロストーク防止 (911)

Fターム[5C080DD09]に分類される特許

1,521 - 1,540 / 1,554

シングルクロック駆動シフトレジスタ

【課題】 出力信号の重なり現象を改善するシングルクロック駆動シフトレジスタを提供する。

【解決手段】 複数のステージ構造を具え、該複数のステージ構造の第Mステージ構造が、クロック信号に基づき第M−1ステージ構造の入力信号をロックするラッチユニットと、該ラッチユニットの出力端に接続して出力信号と該クロック信号とに対してロジック演算を実行するロジックユニットと、該ロジックユニットの出力端に接続し、かつ少なくとも三つ以上の直列したインバータを含む無オーバーラップ信号バッファとを含み、該無オーバーラップ信号バッファにおいて、該ロジックユニットの出力端にカップリングし、かつ並びの順が奇数のインバータの出力信号が第M+1ステージ構造のラッチユニットにフィードインし、第M−1ステージ構造の無オーバーラップ信号バッファの出力信号が該無オーバーラップ信号バッファか、該ロジックユニットにフィードインして該無オーバーラップ信号バッファの出力信号を遅延させるように構成する。

(もっと読む)

プラズマディスプレイパネル用電極駆動装置

電極が維持位相及びアドレス位相のいずれにも用いられる。装置は、各々の電極Ynに対して、この電極に共有点が接続される直列のスイッチ(51、52)及び直列のダイオード(53、54)を有する駆動装置(5)を含む。ダイオードの直列の上位端子が維持ジェネレータ(2)の出力(92)に直接接続され、ダイオードの下位端子が電力スイッチ(6)を介して該同一ジェネレータに接続される。スイッチの直列の端子の1つは負電圧ジェネレータ(4、7)の出力(94、97)に接続される。このようにして、負電圧ジェネレータ(4、7)が電極に負電圧を印加する期間、維持ジェネレータ(2)のダイオード(25)を介して短絡を避けるために電極スイッチ(6)を開いていれば十分である。  (もっと読む)

(もっと読む)

液晶パネル駆動装置

【課題】 液晶パネルの負荷が増大しても、液晶パネルを点灯させることができる液晶パネル駆動装置を提供する。

【解決手段】 液晶パネル駆動基準電圧V100と液晶パネル駆動電圧の最低電位V101と昇圧回路110が生成した電圧V110と液晶パネル表示データS130とを基にセグメント信号生成回路140で複数のセグメント信号S140を生成する。液晶パネル駆動基準電圧V100と液晶パネル駆動電圧の最低電位V101と昇圧回路110が生成した電圧V110とを基にコモン信号生成回路120で複数のコモン信号S120を生成する。複数のセグメント信号S140と複数のコモン信号S120とで液晶パネル150を駆動する。昇圧回路110が出力する電圧V110と液晶パネル駆動基準電圧V100とを電圧比較回路170で比較し、比較結果に基づいて、クロック制御回路160で昇圧クロックS160の周波数を変化させる。

(もっと読む)

シフトレジスタ及び半導体表示装置

【課題】 信号の遅延や、波形の鈍りを抑えつつ、正常に動作することができるシフトレジスタの提供を課題とする。

【解決手段】 シフトレジスタは、クロックドインバータを用いたフリップフロップ回路を複数段有し、クロックドインバータは直列に接続された第1及び第2のトランジスタと、直列に接続された第3及び第4のトランジスタを有する第1の補償回路と、第5のトランジスタ及びトランスミッションゲートを有する第2の補償回路とを有する。第1の補償回路により、前々段の出力に同期して、当該フリップフロップ回路の出力の立ち上がりまたは立ち下がりのタイミングを制御できる。また第2の補償回路により、クロック信号の入力を制御することができる。

(もっと読む)

半導体表示装置およびその駆動回路

【課題】 低消費電力で、電磁ノイズ、不要輻射の小さい半導体表示装置を提供する。

【解決手段】 周辺駆動回路において、レベルシフタ回路によって電圧レベルが上げられたクロック信号を、シフトレジスタ回路に入力する。そしてシフトレジスタ回路からのタイミング信号をレベルシフタ回路に入力し、2段階で電圧レベルを上げてやる。これによって、駆動回路の消費電力を小さくし、電磁ノイズを抑え、不要輻射を小さくすることを実現した。

(もっと読む)

表示装置及びこれを用いた電子機器

【課題】

光センサを搭載し、このセンサの出力に応じて自動調光を行う表示装置の改良、特に、小型軽量でありながら、ノイズによる影響を受けにくく、また、衝撃等にも強い構成を提供する。

【解決手段】

薄膜トランジスタを用いたアクティブマトリクス型の表示装置の基板上に、光検出素子、アナログ−ディジタル変換回路、パラレル−シリアル変換回路を搭載し、外部からのチップセレクト信号により回路が選択された場合に、クロック信号に同期してディジタルデータに変換された光検出素子の信号を輝度制御回路に送出して輝度を調整する。

(もっと読む)

シフトレジスタ及びこれを用いたフラットパネルディスプレイ

【課題】クロック信号の変形又はゆがみに耐えられるシフトレジスタを提供する。

【解決手段】シフトレジスタの偶数ステージにおいては、ラッチ回路710、720の入力ターミナル及び出力ターミナルに変換器730、740が加えられる。また、シフトレジスタは2つのコントロールクロック信号CLK1、CLK2に基づいて作動する。

(もっと読む)

プラズマディスプレイパネルの駆動方法及びその装置

【課題】プラズマディスプレイパネルを選択的消去方式によって駆動するにおいて、消去アドレス放電を安定化して輝点誤放電を防止する。

サステイン期間の最後に印加されるサステインパルスと、前記最後のサステインパルス直前に印加されるサステインパルスとの間の時間差を1.0μs未満にすることで、スキャン電極及びサステイン電極に同時に低電位レベルの電圧が印加される間、消去される壁電荷の量を減少できるプラズマディスプレイパネルの駆動方法及びその装置を提供する。

【解決手段】第1電極及び第2電極にサステインパルスNSUSを印加する段階と、前記第1電極に印加される最後のサステインパルスFSUSと、前記第2電極に印加される最後のサステインパルスNSUS’と、の間の時間差dを0.1μs以上1.0μs未満に制御する段階と、を含んでプラズマディスプレイパネルの駆動方法を構成する。

(もっと読む)

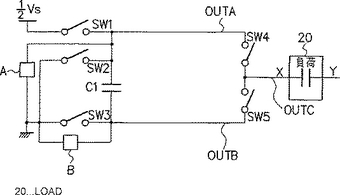

駆動回路および駆動方法

第1の信号ライン(OUTA)は、スイッチ(SW4)を介して負荷(20)のX側端子に第1の電位を供給する。第2の信号ライン(OUTB)は、スイッチ(SW5)を介して負荷(20)のX側端子に第2の電位を供給する。コイル回路(A、B)は、第1の信号ライン(OUTA)および第2の信号ライン(OUTB)とグランドとの間に接続される。また、コイル回路(A、B)は、例えばコイルとダイオードから構成される回路であり、そのコイルは負荷(20)とスイッチ(SW4、SW5)を介してL−C共振を行うように接続されている。  (もっと読む)

(もっと読む)

電界放出型表示装置の駆動装置及びその駆動方法

【課題】 本発明は、電界放出型表示装置に関し、安定なメモリー動作を実現することができ、また、小さい電圧振幅の消去パルスで絶縁体の帯電を消去することができる電界放出型表示装置を提供することを目的とする。

【解決手段】 1行の書き込み動作に割り当てられた時間を書込期間、非書込期間、消去期間の3つに分割し、第1の電子引出電極5には、対応した書込期間のタイミングで電圧Vgの走査パルスを印加し、その後、同数の書込期間と非書込期間とを含む任意の長さの電圧Vsの維持パルスを印加し、電子放出材料3から電子を放出させるが、放出された電子のエネルギーが小さく、絶縁体6の入射電子量より放射電子量が小さくなるような電圧Veの消去パルスを印加する。陰極2には、エミッションを生じさせたい画素には書込期間にデータパルスを印加し、エミッションを生じさせたくない画素には非書込期間にデータパルスを印加する。

(もっと読む)

パワーオンリセット回路及びパワーオンリセット方法

【課題】 パワーオンリセット回路に電源投入のシーケンスを検知させ、リセット信号を出力端子に安定的に出力させるパワーオンリセット回路及びパワーオンリセット方法を提供する。

【解決手段】 高位ロジック電源10と出力端子11との間で電気的に接続され、電源投入による高位ロジック電源10の電圧上昇より遅く電圧上昇する高位電源14に接続する第1制御電極13を有する第1導電型チャネルの第1MISトランジスタP01と、出力端子11と低位ロジック電源15との間で電気的に接続され、高位電源14に接続する第2制御電極16を有する第2導電型チャネルの第2MISトランジスタN01と、を備え、高位ロジック電源10の電圧上昇に応答して第1MISトランジスタP01を導通状態に遷移させ、高位ロジック電源10から出力端子11にリセット信号を供給する。

(もっと読む)

平面表示パネルの駆動方法及び平面表示装置

【課題】 TN型液晶表示装置に代わって、応答速度が速く視野角が広いOCB型液晶表示装置の開発が進められているが、表示画素電極と対向電極間に印加されている駆動電圧が、低電圧状態が継続されると逆転移状態となってしまうので、ブランキング期間も含めて定期的に高電圧を印加する黒挿入が実施されているが、ブランキング期間では充電不足が発生し、ゴーストの発生や白ベタでの逆転移が発生していたが、これらを改善してゴーストの発生や逆転移を防止し得る平面表示パネルの駆動方法及び平面表示装置を提供する。

【解決手段】 平面表示パネル17を駆動するゲートドライバ15及びソースドライバ16を制御しているコントローラ13内に、ブランキング期間における信号の階調を設定し得る信号階調設定手段を設けて中間調の階調に設定し、もしくはコントローラ13内に設けた黒信号挿入タイミング設定手段21によって、ブランキング期間内の黒信号挿入期間を映像信号書込み期間に相当する部分にも設定した。

(もっと読む)

画像表示媒体および画像表示装置

【課題】 画質維持性の改善(ドット欠陥の防止等)、及び駆動電源の低電圧化ができる画像表示媒体および画像表示装置を提供する。

【解決手段】 本発明の画像表示装置10を構成する本発明の画像表示媒体1は、透明性を有する表面基板2Aと、表面基板2Aに対向配置された背面基板2Bと、表面基板2Aと背面基板2Bとの空間を複数のセルに仕切る仕切り部材5と、複数のセル内に封入され、付与された電界に応じて前記セル内を移動する負に帯電した粒子群6A,6B、正に帯電した粒子群6Cとを備えた画像表示媒体であって、負に帯電した粒子群6A,6Bは、移動開始電圧が相違する2種類以上の粒子群を混合して構成されてなることを特徴とする。

(もっと読む)

液晶表示装置の表示制御装置及びそれを有する液晶表示装置

【課題】 外部クロックに依存することなく安定した表示駆動の制御を可能にする液晶表示装置の表示制御装置を提供する。

【解決手段】 外部クロックE-CLKと共に画像データE-DATAを供給され、液晶表示パネル10のデータドライバDD及びゲートドライバGDにそれらのドライブタイミングを制御するタイミング制御信号を供給する表示制御装置20において、外部クロックI-CLKに依存することなく内部クロックI-CLKを生成する内部クロック生成ユニットOSCと、供給される画像データE-DATAが外部クロックE-CLKに同期して書き込まれるバッファメモリ22と、バッファメモリ22に書き込まれた画像データD-DATAを内部クロックI-CLKに同期してデータドライバDDに供給し、データドライバDDによる画像データD-DATAに対応するデータ電圧のデータ線への印加タイミングを制御する電圧印加信号DVDと、ゲートドライバGDによるゲート線のドライブタイミングを制御するゲートクロックC-CLKとを少なくとも含むタイミング制御信号を、内部クロックI-CLKに同期して生成するタイミング制御ユニット24とを有する。

(もっと読む)

表示装置の動回路及びプラズマディスプレイ装置

【課題】 電源投入時の誤動作がなく、出力素子を破壊することがない表示装置の駆動回路の実現。

【解決手段】 入力信号のフロント及びバックエッジに対応したエッジパルスを発生するエッジパルス発生回路31と、フロント及びバックエッジパルスをそれぞれ出力基準電圧を基準としたパルスに変換する第1及び第2のレベルシフト回路Q1,Q2と、第1及び第2のレベルシフト回路に接続された論理回路32と、論理回路に接続されたフリップフロップ回路33と、フリップフロップ回路の内部又は前記フリップフロップ回路の後段における信号ラインに接続されたセットアップ抵抗R4と、セットアップ抵抗の後段に接続された出力増幅回路34と、出力素子LUとを備える表示装置の駆動回路において、セットアップ抵抗は、出力増幅回路34の電源電圧ラインと信号ライン間に接続される。

(もっと読む)

駆動回路及びそれを用いた表示装置

【課題】

複数の電圧に遷移させて出力電圧の切り替えを行うことができるとともに、電源回路の増大を抑止し、安定して動作することができる駆動回路を提供すること。

【解決手段】

本発明にかかる駆動回路は、駆動信号を出力端子7から出力する駆動回路であって、入力信号に基づいて電源電位VDD2又は接地電位VEEのいずれかを出力端子7から出力する出力回路と、出力回路の出力信号が電源電位前記第1の電圧から前記第2の電圧へ遷移する間に、電源電位VDD2から電源電位VDD2’に低下させた後、接地電位VEEに遷移させる出力調整回路と、を備えるものである。

(もっと読む)

画像表示媒体の駆動装置

【課題】 メモリー性を有する画像表示媒体に画像を長時間表示させる場合でも、欠陥画素が生じたり、コントラストが低下するのを防ぐ。

【解決手段】 画像表示装置10は、画像表示媒体12、専用電源26、制御装置28、駆動回路29、インターフェース回路34、画像メモリ36、及びカウンタ38を含んで構成され、画像表示装置10には制御用PC40が接続されている。制御用PC40から画像データが画像表示装置10へ出力されると、制御装置28が駆動回路29を制御して画像表示媒体12に画像を表示させる。画像表示媒体12は、表示側基板と背面側基板との間に、異なる帯電特性の黒粒子及び白粒子が封入された構成であり、時間経過と共に粒子と基板との付着力が強くなる。制御用PC40は、画像の書き換え時にドット不良が発生しないように、所定時間毎に画像を再書き込みするよう画像表示装置10に指示する。

(もっと読む)

画像表示装置及びその保護回路を備えた半導体装置

【課題】外部から供給される信号が不測の原因で途絶した場合、表示部や駆動回路部を誤動作もしくは損傷から保護可能な画像表示装置を提供する。

【解決手段】表示部Dはマトリクス状に配された画素を有し、システム制御部Sは画像信号及び制御信号を含む信号を供給し、駆動回路部H,Vはシステム制御部Sから供給された制御信号に応じて表示部Dを駆動し同じくシステム制御部Sから供給された画像信号に基いて表示部Dに画像を表示する。システム制御部Sから駆動回路部H,Vに供給される信号の経路中に保護回路Zが挿入されている。保護回路Zは、システム制御部Sから制御信号の供給が途切れた場合、これを検出してシステム制御部Sからの制御信号の外部的供給を遮断する一方、内部的に代替の制御信号を生成しこれを駆動回路部H,Vに供給する。

(もっと読む)

プラズマディスプレイパネルの駆動方法及びプラズマディスプレイ装置

【課題】 1本の走査電極が隣り合う2行の表示ラインで共用されるPDPにおいてプログレッシブ表示を行う場合、動作が不安定になったり、リセット期間が長くなって輝度が不足したり、バックグラウンド発光によりコントラストが悪化することを抑制する。

【解決手段】 1駆動期間の最初に全てのセルを維持可能状態にするリセット動作を行った後、選択消去アドレス動作と維持動作とをサブフィールド毎に繰り返し行う。 このとき、1本の走査電極Yを共有する一方の表示ラインLにおけるアドレス動作を行う前に、当該表示ラインのみがアドレス動作が可能で、他方の表示ラインはアドレス動作が行われないような壁電荷状態を作り出し、安定してアドレス動作を行うことができるようにした。

(もっと読む)

画像表示媒体の駆動装置、駆動方法、及び駆動プログラム

【課題】 メモリー性を有する画像表示媒体の駆動時に発生するノイズの影響を抑えて良好に画像を表示させることができる画像表示媒体の駆動装置、駆動方法、及び駆動プログラムを得る。

【解決手段】 シーケンス制御装置28は、列電極24に電源装置26からの電圧が印加された際に発生するノイズが、画像変換回路38と列電極駆動駆動回路30との間の信号線に生じる期間は、画像データが画像変換回路38から列電極駆動回路30に出力されないように、画像変換回路38に指示する。すなわち、画像変換回路38と列電極駆動回路30とのデータ通信を停止させる。そして、それ以外の期間、すなわち、ノイズが発生しない期間では、画像変換回路38と列電極駆動回路30とのデータ通信を許可する。

(もっと読む)

1,521 - 1,540 / 1,554

[ Back to top ]