Fターム[5C080JJ03]の内容

陰極線管以外の表示装置の制御 (251,852) | 図面情報 (70,797) | 回路線図 (9,431)

Fターム[5C080JJ03]に分類される特許

9,361 - 9,380 / 9,431

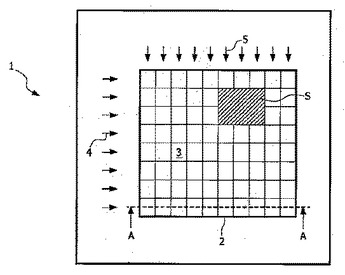

ディスプレイ上で周囲光を検出する回路

ディスプレイ上で周囲光を検出するための回路であって、光センサを有し、周囲光の強度を代表する連続光信号を定期的に発生させるため周囲光に応答する光集積光センサ回路と、該連続光信号を受信し、該連続光信号の連続進行平均を代表する平均周囲光信号を発生させるための平均化回路とを含む回路。  (もっと読む)

(もっと読む)

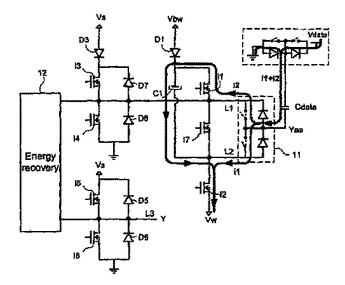

プラズマディスプレイパネルの駆動装置

行列状に配列された複数のセルを有するプラズマディスプレイパネルの駆動装置に関し、当該駆動装置は、アドレス期間においてディスプレイセルの行を選択的にアドレスし、必要な場合、ディスプレイの列に選択的にデータ電圧を与える手段と協働して、選択された行と列の交点に位置するセル内部での放電を生じさせる行アドレス手段(I1、I2、C1、D1、I7)と、アドレス期間のすぐ後に続くサステイン期間においてセルの放電を維持するためのサステイン手段(I3、I4、I5、I6)とを有する。本発明に従って、行アドレス手段及び/又はサステイン手段により、アドレス及び/又はサステイン期間において、両方向の電流が前記ディスプレイセルを自由に流れることができ、電磁干渉を発生しない。  (もっと読む)

(もっと読む)

カラーディスプレイパネル

カラーディスプレイパネルは、少なくとも1つの画素を有する。該画素は、第1の動作範囲にある電圧が印加される場合に、第1のスペクトル分布を有する光を放射し、且つ、第2の動作範囲にある電圧が印加される場合に、異なったスペクトル分布を有する光を放射する発光セル(13)を有する形式のサブピクセル回路を有する。当該カラーディスプレイパネルは、前記発光セルによる光の放射を制御する信号を第1のサブピクセル回路へ送る少なくとも1つのデータライン(8)を更に有する。前記サブピクセル回路は、前記信号の制御下で、夫々の基準電圧に依存して、夫々の電圧を前記セル(13)へ印加する少なくとも2つの能動部品(9,10)を更に有する。  (もっと読む)

(もっと読む)

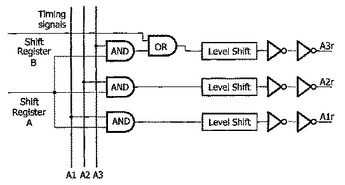

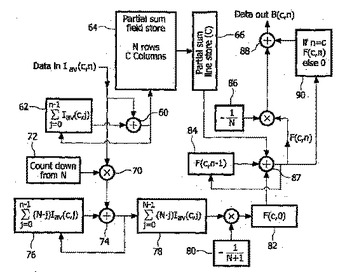

スクロールアドレス指定によるエレクトロルミネッセント表示装置

アクティブマトリクス型エレクトロルミネッセントディスプレイは、表示素子を流れる電流の駆動を中断する手段を有する。ディスプレイの行ドライバ回路は、実質的に完全なフィールド周期からアドレス指定期間を引いた期間まで変動する期間を有するパルスを含む、中断手段の駆動電圧を生成するシフトレジスタ及びロジック構成50、54を有する。シフトレジスタ構成50を伝播する1以上の信号は、パルス期間を制御する。この構成は、それぞれの行の全体の光放射周期の制御により、画素の行毎のアドレス指定の制御を可能にするため、低減されたドライバの複雑さを提供する。この制御は、スクローリングアドレス指定のスキームが実現されるのを可能にする。  (もっと読む)

(もっと読む)

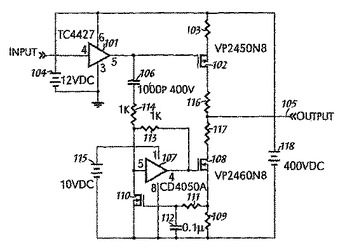

静電結合を用いた高電圧パルスドライバ

高電圧システムに共通する、高電源リプルにおいて有用である静電結合を用いた高電圧ドライバである。それは、デューティサイクルの最大範囲を許容するが、変圧器の磁気の制限はなく、または、光学式の結合方法における複雑さの増加もない。それはまた、出力駆動ラインにアークする高電圧によって作成される過渡電圧においても、強固である。本発明はまた、特に例示的ディスプレイの応用における使用のために、低コストでの静電結合の使用を再構築するが、静電結合に特有の制限はない。  (もっと読む)

(もっと読む)

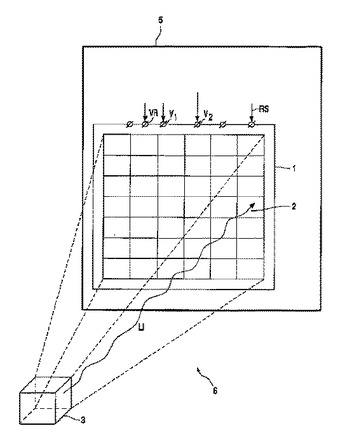

液晶マイクロディスプレイ

本発明は、液晶マトリックスマイクロディスプレイ、特に、液晶セルのマトリックスアレイを制御するための電子回路が一体化されたモノリシックシリコン基板に具現された液晶マトリックスマイクロディスプレイに関する。

マトリックスには、行および列のクロスオーバにおける各ドットのために、このクロスオーバに位置する基本液晶セルを制御するための基本電子回路が含まれる。この回路には、画像フレームの期間に、列によって印加されるアナログ電圧を蓄積するための少なくとも1つの蓄積コンデンサ(Ca、Cb)であって、その第1の端子がトランジスタ(Ta、Tb)のゲートに連結された蓄積コンデンサと、2つの電圧供給端子間で直列になった基本電流源(SC1)およびスイッチングトランジスタ(Ta、Tb)であって、スイッチングトランジスタのドレインが液晶セル(LC)に連結された基本電流源およびスイッチングトランジスタと、が含まれる。少なくとも1行の全てのセルに共通の周期的な電圧ランプが、この行のセルにおける蓄積コンデンサの第2の端子に印加される。

(もっと読む)

液晶表示装置及びその駆動方法及び液晶表示パネルの駆動装置

液晶層に印加する電圧の極性反転周期を2フレーム周期以上、より好ましくは、10秒程度と長く設定する。これにより、1フレーム程度の極性反転周期では防止できなったフリッカを防止し、また反転周期を長くすることで消費電力を低減することができる。液晶材料や配向膜材料として、イオン反応性が低く、残留分極の少ない材料を採用するなどにより、極性反転周期を長くしても、液晶層における残留DC成分の発生を防止でき、表示品質の低下を防止できる。印加電圧に対する透過率に極小値を備えるLCDの場合には、さらに、正極性印加期間と負極性印加期間とで、液晶の透過率が極小値を示す印加電圧が等しくなるよう、例えば共通電極電位を調整することで、黒を正確に表示できる。 (もっと読む)

電気泳動ディスプレイパネル

電気泳動ディスプレイパネルは、粒子(6)が極端位置の一を実質的に占めることが可能であるリセット電位差であるように、そして続いて、粒子(6)が画像情報に対応する位置を占めることが可能である階調電位差であるように、各々のピクチャ要素(2)の電位差を制御するための駆動手段(100)を有する。駆動手段は、少なくとも最大リセットパルスエネルギーの50%又はそれ以上を示すリセット電位差に対して、リセット電位差と階調電位差との間にリセット値より実質的に小さい電圧値を有する1つ又はそれ以上のパルスを適用するように備えられている。  (もっと読む)

(もっと読む)

電気泳動ディスプレイユニット

共通電極(6)と画素電極(5)との間に位置付けられた画素(11)を有する電気泳動ディスプレイユニット(1)は、全画像更新時間を短縮するために、画素電極(5)に結合されたトランジスタ(12)を危険にさらす画素(11)における駆動電圧の増加を必要とする。それらの駆動電圧に対してトランジスタ(12)を保護するために、設定信号(S1、S2)が、交流電圧信号(V6)における遷移からもたらされる画素(11)における電圧を低減するためにトランジスタ(12)により画素電極(5)に印加される。駆動フレーム期間(Fd)の間、データパルス(D1、D2、D3、D4、D5、D6)が印加され、そして設定フレーム期間(Fs)の間、設定信号(S1、S2)が印加される。  (もっと読む)

(もっと読む)

複数のセルを有するカラー表示スクリーン

カラー表示スクリーンは、複数のセル(2)を有する。夫々のセル(2)は、第1の色の第1の出力光及び第2の色の第2の出力光を供給する能力を有する画素(P)と、光学表示制御信号(Li)を電気信号(I)に変換するための感光性デバイス(D)とを有する。光学表示制御信号(Li)は、第1の出力光及び第2の出力光を制御するよう、第1の出力光及び第2の出力光に関する情報を含む。感光性デバイス(D)は、第1及び第2の出力光に関する情報をデコードするためのデコーダ(DM)を有する。  (もっと読む)

(もっと読む)

発光ピクセルのアレイを駆動する回路及び方法

発光エレメントを含むピクセルの列を駆動する技術が提供される。該技術は、アレイのデータ線及び帰還線に接続された帰還データ源から供給される帰還データ、並びに帰還経路を備えるピクセル駆動回路を含む。該技術は、入力信号の補正のために基準エレメントのブロックを含むこともできる。 (もっと読む)

必要メモリを低減された双安定ディスプレイ

ディスプレイ装置(401)は、波形(330、331)、即ち、電位差の列を印加することにより1つの光学状態から他の光学状態へ変えられる表示素子(118)の集合を有する。印加されるべき波形(330、331)は、当該装置のメモリ内の参照テーブル(445)に記憶される。参照テーブル(445)は、波形(330、331)の一部が表示素子(118)の異なる集合に対して再利用されるように、順序づけられている。これにより、波形を記憶するための必要メモリが低減される。

(もっと読む)

(もっと読む)

ピクセルドライバ回路

複数のピクセルを有する表示器に使用するためのピクセル回路が提供される。負荷がバランスされたカレントミラーピクセル回路は、デバイスの劣化及び/又は不整合、並びに温度及び機械的歪等の変化する環境的要因を補償することができる。上記ピクセル回路はピクセル駆動回路を有し、該ピクセル駆動回路はスイッチング回路と、基準トランジスタ及び駆動トランジスタを有するカレントミラーであって、基準トランジスタ及び駆動トランジスタの各々が第1及び第2ノード並びにゲートを有し、基準トランジスタのゲートが駆動トランジスタのゲートに接続されるようなカレントミラーと、基準トランジスタのゲートと接地電位との間に接続されたキャパシタとを有する。上記ピクセル回路は、更に、上記カレントミラーと接地電位との間に接続された負荷を有し、該負荷は第1負荷エレメントと第2負荷エレメントとを有し、第1負荷エレメントが上記基準トランジスタの第1ノードに接続され、第2負荷エレメントが上記駆動トランジスタの第1ノードに接続される。 (もっと読む)

セグメント化されたキャラクタ・ディスプレイ

キャラクタ・ディスプレイ(10、200、500)は、行(RW)と列(CL)に配置した59セグメント(111〜179)を備える。28セグメントは、ディスプレイ(10、200、500)の周縁(RP)を画定し、11の付加的なセグメント(115〜175、141〜149)は、4つの象限(Q)を画定するデバイダを画定し、5つの付加的なセグメント(122〜134、126〜138、152〜164、156〜168)は、象限の対角線を画定するために、4つの象限(Q)のそれぞれに配設される。キャラクタ・ディスプレイ(10、200、500)は、電気的機能性糸(FY)を含む編布式製品(200、500、510、520、530)で具体化することができる。アドレス指定信号(SIGNAL)は、ディスプレイ(10、200、500、510、520、530)を選択的に駆動するために、機能性糸(FY)のアドレス指定可能デバイス(U1、U2、U3)をアドレス指定するように、編布式製品(200、500、510、520、530)の導電性糸(240、242、244、540、542、544、546、548)を介して印加することができる。

(もっと読む)

(もっと読む)

照明装置制御方法及びシステム

本発明は、改良されたデジタル輝度制御システムを提供する。本システムは、点灯される発光体の数を選択することにより、照明装置の光度を制御できる。本システムは、全体の光度への各発光体の貢献度の相違に基づき、電力消費を低減するよう、点灯される発光体の数を最適化する。周囲環境の光度のサンプリング周波数を適正に調整することにより、本発明は輝度制御システムの動作周波数を低下させ、従って更に消費電力を低減させる。本発明はまた、アナログ輝度制御システムを提供する。アナログ輝度制御システムは、光センサー装置、アナログの輝度制御装置、及び一式の光源を有し、リアルタイムの輝度調整を実現し、消費電力を低減する。  (もっと読む)

(もっと読む)

光制御装置およびその駆動方法

光制御装置8の画素10には、現フレームの輝度値を記憶する第一の記憶素子18と、次のフレームの輝度値を記憶する第二の記憶素子16と、第二の記憶素子16に記憶された輝度値を第一の記憶素子18に転送して画素10の輝度値を変更するスイッチ素子である第一のトランジスタ14と、がそれぞれ設けられる。制御部60は、複数の画素10が第一の記憶素子18に保持された輝度値に応じて発光している間に、各画素10の第二のトランジスタ12を順次オンとして第二の記憶素子16に次のフレームの輝度値の書き込みを行う。 (もっと読む)

参照テーブルメモリを低減された電気泳動ディスプレイ

ディスプレイ装置(301)は、温度補償データに対するメモリ(314)の必要性を低減する。様々な温度に対するスケーリング係数(433)及び任意のディスプレイ温度に対してグレースケールを駆動するよう最適化された波形の参照テーブルは、メモリ(314)に記憶されている。ディスプレイ(301)の特定の温度に対する波形は、参照テーブル及びスケーリング係数(433)から導き出される。幾つかの温度では、波形のある部分のみが変えられる必要があり、これらの部分しか、参照テーブルからの正確な調整を必要としない。  (もっと読む)

(もっと読む)

表示装置

本発明は、複数の表示画素を有するディスプレイと、データ信号を受付するデータ入力と、少なくとも1つのフレーム期間中に各表示画素の全体輝度値により画像を前記ディスプレイ上に生成するため、前記表示画素に前記データ信号を分配するコントローラと、

を有するアクティブマトリックス表示装置に関する。本装置は、表示画素の少なくも一部に対してフレーム期間を分割し、少なくとも1つの部分の表示画素が、フレーム期間の第1サブ期間中に非ゼロの第1輝度レベルと、フレーム期間の第2サブ期間中に非ゼロの第2輝度レベルとによる光出力を少なくとも有するものとなるよう構成され、輝度レベルの時間平均和は、全体輝度レベルに実質的に等しくなるよう構成される。  (もっと読む)

(もっと読む)

アクティブマトリクスディスプレイ装置

アクティブマトリクスLEDディスプレイは、表示素子の輝度を検出するための光依存性デバイスと、画素の駆動トランジスタの閾値電圧を測定するための閾値電圧測定回路とを有する。このようにして、表示素子のエージング補償は、光学フィードバック経路により提供され、駆動トランジスタの閾値電圧の変動補償は、閾値電圧の測定によって提供される。これは、閾値電圧の変動に対する信頼性のある補償機構を提供し、一方で、エージング補償も提供する。  (もっと読む)

(もっと読む)

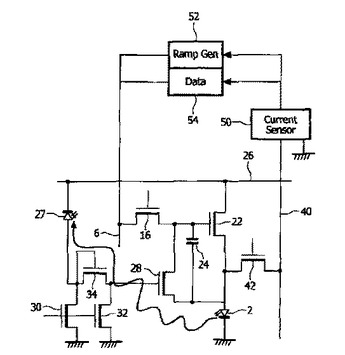

発光ディスプレイ用のデータ信号ドライバ

ディスプレイは、行及び列に配列される発光素子を有しており、列における画素には、それぞれの列の電源ライン26からの電流が供給される。目標とする画素を駆動する電流は、その電流−明るさの特性のモデルに基づいて所望の画素の明るさレベルに対応して決定される。これらは、列の電源ラインから引き出される電流から生じるそれぞれの画素での列の電源ライン26の電圧を考慮するために変更される。本発明は、電源ラインを構成するために使用される金属の有限の抵抗と同様に、電流供給型TFTの有限の出力インピーダンスによるアクティブマトリクス型LEDディスプレイで生じる垂直のクロストークの問題に対処する。  (もっと読む)

(もっと読む)

9,361 - 9,380 / 9,431

[ Back to top ]