Fターム[5E034DE03]の内容

サーミスタ、バリスタ (5,260) | 製造、試験(PTC、NTC、バリスタ) (588) | 粉砕 (29)

Fターム[5E034DE03]に分類される特許

1 - 20 / 29

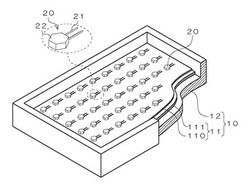

サーミスタ素子の製造方法

【課題】白金を含む電極線を有する未焼成サーミスタ素子を白金を含む支持体上に載置して焼成する工程を備える場合に、電極線と支持体との融着が防止されたサーミスタ素子の製造方法を提供する。

【解決手段】白金を含む電極線21と電極線21の一部が埋設されたセラミック粉末プレス体22とを有する未焼成サーミスタ素子20を焼成してサーミスタ素子を得るサーミスタ素子の製造方法において、支持体11上に未焼成素子20を載置して焼成する工程を備え、支持体11は、白金を含む金属からなる本体部110と、本体部110のうちの少なくとも未焼成素子20が載置される表面に、セラミック粉末プレス体22を構成するセラミックスと実質的に同じセラミックスが焼き付けられてなるコート層111を有する。

(もっと読む)

低温焼結による純銀内部電極を備えた多層チップ型酸化亜鉛バリスタの製造方法

【課題】低温焼結特性を備え、純銀を内部電極に使用した多層チップ型ZnOバリスタの製造方法を提供する。

【解決手段】本発明のZnOバリスタの製造方法は、十分な半導性を有するドープZnO粒子を調製するステップと、高インピーダンス焼結材料(またはガラス粉末)を別に調製するステップと、最後に前記ドープZnO粒子と前記高インピーダンス焼結材料を所定の比率でよく混合し、多層ZnOバリスタ(または積層バリスタ(Multilayer varistor、MLV)とも呼ばれる)の従来の作製手法に従って、850℃〜900℃の低温焼結温度下で純銀を内部電極として使用したZnOバリスタを作製するステップを含む。

(もっと読む)

温灸器

【課題】

部品点数が少なく、小型であっても十分な温熱効果があり、取り扱い容易な温熱灸を提案することにある。

【解決手段】

ケースと、ケースの内部に設けられた正特性サーミスタと、正特性サーミスタに電流を供給する乾電池と、を有する温灸器であって、正特性サーミスタの一方端面は、ケースの先端部に直接接合されており、ケースは乾電池と接続されるための第1の金属端子が引き出されており、正特性サーミスタの他方端面は、乾電池と接続されるための第2の金属端子が引き出されるとともに、正特性サーミスタの他方端面と乾電池との間に、保温部材を設けることを特徴とする。特に、正特性サーミスタの室温25℃における抵抗率が10Ω・cm以下であり、乾電池が1.5V以下であることが好ましい。

(もっと読む)

サーミスタ素子

【課題】外部電極層にリード端子を強固に抵抗溶接することが可能で、高温での連続使用においても信頼性の高いサーミスタ素子を提供すること。

【解決手段】サーミスタ層を有する素子本体と、素子本体の表面に形成される外部電極層とを有するサーミスタ素子であって、外部電極層は、素子本体の表面に直接に形成される第1外部電極層と、第1外部電極層の表面に形成される第2外部電極層とを有し、第1外部電極層が白金粒子とセラミック粒子とを含み、第2外部電極層が白金粒子で構成され、第1外部電極層の厚みをtaと表した場合に、5μm≦ta≦30μmであり、第2外部電極層の厚みをtbと表した場合に、5μm≦tb≦50μmであり、第2外部電極層には、リード端子が抵抗溶接されることを特徴とする。

(もっと読む)

チップ型バリスタの製造方法

【課題】凹凸がある表面にも均一に高抵抗層を塗布することが可能で、かつ生産性の良いチップ型バリスタの製造方法を提供する。

【解決手段】チップ型バリスタは、半導体である酸化亜鉛を主成分とするバリスタ素体表面5a〜5dと、少なくとも1対の電極層とを有し、その端部には導電性の外部電極4が、前記バリスタ素体よりも外側に盛り上がって形成されている。このように凹凸のあるチップ型バリスタ表面において、バリスタ素体表面の一部又は全部に、紫外線硬化樹脂等の高抵抗層を、少なくとも前記電極層の層間距離と同じ幅Dを持つ、帯状の範囲に均一に塗布することが可能な、インクジェット方式による高抵抗層6の形成手段を提供するものである。

(もっと読む)

サーミスタ素子およびその製造方法

【課題】 絶縁体の量を抑えながら抵抗値を従来構造よりも大幅に高くすることができるサーミスタ素子およびその製造方法を提供すること。

【解決手段】 板状の金属酸化物焼結体2と、該金属酸化物焼結体2の上下面にそれぞれ一部を電極接合部2aとして除いて形成された絶縁層3と、金属酸化物焼結体2の上下面の少なくとも電極接合部2aに形成された一対の電極層4と、を備えている。そして、金属酸化物焼結体2の原料に、焼結によって表面に一部が絶縁皮膜として析出する絶縁材料が混合されており、絶縁層3が、金属酸化物焼結体2の焼結時に表面に析出した絶縁皮膜である。

(もっと読む)

積層型複合電子部品

【課題】中間接合層の緻密性および保形性に優れ、特にバリスタ素子部の特性劣化が少ない積層型複合電子部品を提供すること。

【解決手段】バリスタ素子部20とフェライト素子部30と中間接合層40とを有する積層型複合電子部品である。中間接合層が、SiO2 :30〜60重量%、ZnO:0〜20重量%、Al2 O3 :0〜20重量%、B2 O3 :0〜5重量%、アルカリ土類金属酸化物:30〜50重量%、およびアルカリ金属酸化物:0〜1重量%を含むガラス組成物で実質的に構成してある。

(もっと読む)

酸化亜鉛バリスタおよびその製造方法

【課題】高い雷サージ耐量性能を有する酸化亜鉛バリスタおよびその製造方法を提供する。

【解決手段】酸化亜鉛(ZnO)100mol%に対して、酸化アンチモン(Sb2O3)2.5〜5.0mol%と、アルミナ(Al2O3)0.05〜0.15mol%とを添加し、さらに酸化コバルト(CoO)と二酸化マンガン(MnO2)をそれぞれ2.0〜6.0mol%添加してなるバリスタ組成物により酸化亜鉛バリスタを作製する。

(もっと読む)

電流−電圧非直線抵抗体およびその製造方法

【課題】非直線抵抗特性に優れた電流−電圧非直線抵抗体およびその製造方法を提供する。

【解決手段】電流−電圧非直線抵抗体10は、酸化亜鉛を主成分とし、副成分として少なくともビスマス(Bi)、アンチモン(Sb)を含んだ混合物の焼結体20を備える。また、電流−電圧非直線抵抗体10における焼結体20は、焼結体20の所定の断面における、焼結体20の微細構造を主に構成する各酸化亜鉛粒子21の断面において、断面に亘って最長となる最長直線の長さ(L)と、この最長直線の中点で直交し、断面に亘る直交直線の長さ(S)との比(S/L)を平均した値が0.66以上となるように構成されている。

(もっと読む)

酸化亜鉛バリスタを作製するための2つの独立した処理手順を介して酸化亜鉛バリスタを製造するプロセス

【課題】酸化亜鉛バリスタを製造するためのプロセスを提供すること。

【解決手段】ドープした酸化亜鉛と高インピーダンス焼結材料を所定の比率でよく混合し、次いでこれを使用して低温の焼結(900℃未満)によって従来技術により酸化亜鉛バリスタを作製することができるように、酸化亜鉛へのドーピングおよび酸化亜鉛粒子の高インピーダンス焼結材料との焼結を2つの独立した処理手順によって実施する。得られた酸化亜鉛バリスタは、内部電極として純銀を使用することができ、バリスタ特性、サーミスタ特性、キャパシタ特性、インダクタ特性、圧電性および磁性のうちの1つまたは複数を特に有する。

(もっと読む)

多層構造およびその作製方法

本発明により特定された多層構造は、モノリシック多層構造を形成するよう、バリスタセラミックと共焼結しうる誘電体セラミック材料を備える。多層構造は、そのため、バリスタセラミックの一つの層と、誘電体の別の層とを備える。多層構造において、両方の層は互いに直接的に隣接して配置されうる。多層構造では、メタライゼーション面がセラミック層の上または間に配置され、メタライゼーション面は伝導体区域を形成するよう構成されており、金属被覆領域が作られている。メタライゼーション面およびセラミック層は、バリスタと、キャパシタンス、レジスタンスおよびインダクタンスの素子機能のうちの少なくとも一つから選択されるさらなる素子を形成する。 (もっと読む)

電気的多層コンポーネント

電気的多層コンポーネントは、外部接点(2, 2´)および内部電極(3, 4)を設けた基体1、第1内部電極3を設けたセラミックバリスタ層5、ならびにバリスタ層5に隣接する誘電体層6を有する。誘電体層6には、少なくとも1つの開口8を設け、半導体材料または金属材料で充填する。 (もっと読む)

サーミスタ用金属酸化物焼結体及びサーミスタ素子並びにサーミスタ用金属酸化物焼結体の製造方法

【課題】 サーミスタ用金属酸化物焼結体及びサーミスタ素子並びにサーミスタ用金属酸化物焼結体の製造方法において、1000℃付近の高温でも還元による抵抗値変化が小さい特性を得ること。

【解決手段】 サーミスタ用金属酸化物焼結体1であって、一般式:(1−z)ABO3+zY2O3(ただし、ABO3はペロブスカイト型酸化物、0<z≦0.8)で示される複合酸化物焼結体部2の表面に層厚が3μm以上のY2O3層3が形成されている。また、サーミスタ素子が、このサーミスタ用金属酸化物焼結体1と、サーミスタ用金属酸化物焼結体1に一端が固定された一対のリード線と、を有する。

(もっと読む)

積層型セラミック電子部品

【課題】ESDに対する耐性が高く、しかも容易にショートしない積層型セラミック電子部品を提供する。

【解決手段】半導体セラミック層10と内部電極12a〜12c,14a〜14cとが交互に積層された素子本体4と、前記素子本体の端部に形成された複数の端子電極6と、を有する積層型セラミック電子部品2であって、前記端子電極6と、該端子電極の極性と異なる極性を有し、最外に配置された内部電極14aと、の最短距離をd(d1)とし、極性の異なる内部電極間の最短距離をt(t1)とすると、前記dおよびtが、d/t≦0.96である関係を満足する。

(もっと読む)

静電気保護素子とその製造方法

【課題】簡単な構成で、絶縁基板上に形成した厚膜素子により低静電容量化するとともに、性能のばらつきがなく、高速通信に必要な高周波帯域でも通信品質に影響を与えることなく十分な静電対策が可能な静電気保護素子とその製造方法を提供する。

【解決手段】絶縁基板14上の中央部に位置した中間電極12と、中間電極12に積層された静電気吸収体16と、静電気吸収体16を挟んで中間電極12に各々対向した対をなす端部電極17,18を有する。端部電極17,18及び静電気吸収体16を覆った絶縁体の保持層20を備える。対をなす端部電極17,18の互いに対向する端部間の間隔Gは、端部電極17,18と中間電極12間の静電気吸収体16の膜厚tよりも大きい。中間電極12若しくは対をなす端部電極17,18と静電気吸収体16との間に、絶縁体のガラス若しくはセラミックスの中間層20を備える。

(もっと読む)

積層型チップバリスタ

【課題】電子素子から発生した熱を効率よく放熱させ、且つバリスタ特性劣化を抑制できる積層型チップバリスタを提供すること。

【解決手段】積層型チップバリスタV1は、複数の第一内部電極11同士を電気的に接続する第一スルーホール導体13と、第一主面S1に最も近い第一内部電極11と第一外部電極5とを電気的に接続する第二スルーホール導体15と、複数の第二内部電極21同士を電気的に接続する第三スルーホール導体23と、第一主面S1に最も近い第二内部電極21と第二外部電極6とを電気的に接続する第四スルーホール導体55と、を備えている。第一及び第二外部電極5,6は、それぞれめっき層を有している。第二スルーホール導体15の数は第一スルーホール導体13の数よりも少なく、第四スルーホール導体55の数は第三スルーホール導体23の数よりも少ない。

(もっと読む)

アンチモン添加酸化亜鉛バリスタの製造方法

【課題】Sbの添加量ができるだけ少なく、高いバリスタ電圧を有し、高い非線形指数を有し、課電劣化特性に優れたZnOバリスタを提供する。

【解決手段】酸化亜鉛98.8mol%、酸化ビスマス0.5mol%、酸化マンガン0.5mol%、4酸化3コバルト0.2mol%およびアンチモンの水溶性塩200〜2400ppmに、平均粒径5〜10nmの二酸化ケイ素100〜1500ppmを添加したものを湿式混合し、得られた混合物を仮焼成した後粉砕し、粉砕物を加圧成形し、得られた成形物を本焼成することによってアンチモン添加酸化亜鉛バリスタを製造する。

(もっと読む)

静電気対策部品およびこの静電気対策部品を備えた発光ダイオードモジュール

【課題】焼成の際のセラミック基板とバリスタ層の熱収縮挙動の違いなどから発生する反りを低減し、実装信頼性が向上した薄型構成の静電気対策部品を提供することが課題であった。

【解決手段】この課題を解決するために、セラミック基板1とバリスタ層3とガラスセラミック層2を有する静電気対策部品において、製造時の反り解消用として、セラミック基板のバリスタ層を設けた面と反対側の面にガラスセラミック層4を設けた構成とするものである。

(もっと読む)

集合基板、集合基板の製造方法、及びバリスタ

【課題】熱を効率良く放熱することが可能なバリスタを製造するための反りを防止した集合基板の製造方法を提供する。

【解決手段】準備工程においてバリスタグリーンシートと、内部電極パターンと、放熱グリーンシートとを準備し、積層工程S5において、これらのグリーンシートを積層してグリーン積層体を得る。その後、焼成工程S6において、グリーン積層体を焼成して集合基板を得る。積層工程で形成するグリーン積層体は、第1及び第2のバリスタグリーン部と放熱グリーン部とを備える。第1及び第2のバリスタグリーン部とは、それぞれ、バリスタグリーン層と、バリスタグリーン層内において配列した複数の内部電極パターンと、を有する。放熱グリーン部は、互いに対向する一対の面を有し、一方の面は第1のバリスタグリーン部の面と接合し、他方の面は第2のバリスタグリーン部の面と接合している。

(もっと読む)

セラミック電子部品

【課題】セラミック素体にクラックが発生した場合であっても、導通不良の発生時期を遅らせることにより、長寿命化を図ることができるセラミック電子部品を提供する。

【解決手段】積層チップバリスタ1では、外部電極51において、第2の内部電極33の引出部分33aが接続される第1の領域61と、ハンダ電極53が接続される第2の領域62とが同一の平面部において互いに重ならない位置に形成されている。このため、バリスタ素体11側にクラックが発生した場合であっても、第2の内部電極33の引出部分33aの断裂が生じることはなく、内部電極対21から外部電極51における第2の領域62の外側部分を経由してハンダ電極53に至る導通経路Rが維持される。したがって、クラックが進行してハンダ電極53が完全に剥離してしまうまで、導通不良の発生時期を遅らせることが可能となる。

(もっと読む)

1 - 20 / 29

[ Back to top ]