Fターム[5E314GG22]の内容

印刷回路の非金属質の保護被覆 (18,974) | 目的、効果 (3,904) | はんだブリッジ防止 (58)

Fターム[5E314GG22]に分類される特許

21 - 40 / 58

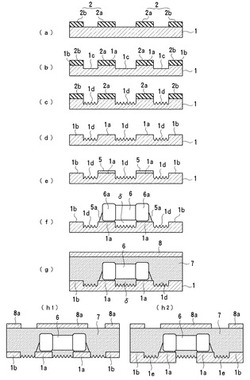

部品内蔵基板の製造方法

【課題】導電性接合材の濡れ広がりによるショートを防止し、信頼性の高い部品内蔵基板の製造方法を提供する。

【解決手段】一定の厚みを有する金属板1の一方主面上に、ランド領域1aに対応する部位を覆うエッチングレジスト層2を形成し、金属板1を所定厚みを残してエッチングすると共に、エッチングされた凹部底面にはんだ濡れ性が悪い濡れ防止領域1dを形成する。エッチングレジスト層を除去してランド領域を露出させた後、ランド領域に回路部品6をはんだ5aを用いて接続し、金属板上に未硬化の樹脂シートを重ねて圧着し、回路部品が埋設された樹脂層7を形成する。その後、金属板1の他方主面側を加工して配線パターンを形成する。濡れ防止領域1dは、ランド領域1aよりはんだの濡れ性が悪くなるよう金属板の一方主面を粗化又は酸化した領域、あるいははんだ濡れ性の悪い被膜よりなる。

(もっと読む)

配線基板およびその製造方法

【課題】 半導体素子および電子部品を良好に実装することが可能な配線基板を提供すること。

【解決手段】 絶縁基体1の搭載部1Aに配設されており、上面に半導体集積回路素子E1の電極が導電バンプB1を介して接続される半導体素子接続パッド2Aと、絶縁基体1の上面における搭載部1Aの外側に配設された電子部品接続パッド2Bと、半導体素子接続パッド2Aの上面および電子部品接続パッド2Bの上面を露出させる第1のソルダーレジスト層3aと、電子部品接続パッド2B上に半導体素子接続パッド2Aの上面を超える厚みで被着されており、上面に電子部品E2の電極が半田ボールB2を介して接続される導電突起7と、第1のソルダーレジスト層3a上に搭載部1Aを囲繞するように被着されており、導電突起7の側面を埋めかつ導電突起7の上面の全面を露出させる第2のソルダーレジスト層3bとを具備する。

(もっと読む)

部品内蔵配線基板および部品内蔵配線基板の製造方法

【課題】1対の接続用の端子付きの電子部品を内蔵した部品内蔵プリント配線基板の不良を防止することができる部品内蔵プリント配線基板および部品内蔵プリント配線基板の製造方法を提供することを目的とする。

【解決手段】コア層1にチップ部品7が実装された部品内蔵プリント配線基板において、コア層1において端子7aが半田接合される1対の電極3aの中間に位置してこの電極3aの幅寸法に対応した範囲にレジスト4を形成し、このレジスト4および電極3aと端子7aとを接合する半田部6a*を封止樹脂部6b*で覆う構造とする。これにより、チップ部品7の実装後のコア層1を対象として行われる粗化処理における半田部6a*やレジスト4へのダメージや、再加熱時に半田部6a*が再溶融した溶融半田の流動に起因する電極3a間の短絡などの部品内蔵配線基板17の不良を防止することができる。

(もっと読む)

配線基板およびその製造方法

【課題】 半導体素子の電極端子と半導体素子接続パッドとを導電バンプを介して強固かつ良好に接続することが可能な配線基板を提供すること。

【解決手段】 上面に半導体素子E1が搭載される搭載部1Aを有する絶縁基体1と、絶縁基体1の搭載部1Aに格子状の並びに被着されており、上面に半導体素子E1の電極が導電バンプB1を介して接続されるめっき層から成る円形の複数の半導体素子接続パッド2Aと、絶縁基体1上に被着されており、半導体素子接続パッド2Aの側面を覆うとともに半導体素子接続パッド2Aの上面を露出させるソルダーレジスト層3とを具備して成る配線基板10であって、ソルダーレジスト層3は、少なくとも半導体素子接続パッド2Aの上面全面を底面とする凹部3Aを有する。

(もっと読む)

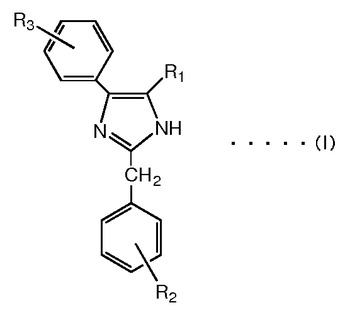

銅または銅合金の表面処理剤及びその利用

【課題】プリント配線板回路部の銅または銅合金表面の半田濡れ性が良好となる表面処理剤および表面処理方法を提供する。

【解決手段】一般式(I)で示されるイミダゾール化合物を含有する表面処理剤。

(式中、R1、R2およびR3は同一または異なって、水素原子または炭素数が1〜8のアルキル基を表す。)

(もっと読む)

電子部品実装方法

【課題】半田フロー工程により電子部品を実装する際、電子部品の実装方向の制約をなくし、実装後の半田不良箇所に対する手作業による修正を削減する。

【解決手段】基板S上に形成されているパッドに電極14を当接させた電子部品10を、該基板上に接着剤で仮固定した後、該基板Sを搬送方向に搬送しながら半田フロー工程を行ない、該電子部品を半田付けして実装する電子部品実装方法において、基板Sと該基板に実装する電子部品10とについて、搬送方向と実装方向との関係の実績データから予め求めてある半田付け不良が発生し易いパッドの近傍に、前記半田フロー工程における溶融半田の流れを阻害するダム用接着剤20を予め塗布しておく。

(もっと読む)

配線基板およびその製造方法

【課題】フリップチップ接続される導電突起・接続パッド上に半田層を良好に形成することができ、互いに隣接する導電突起・接続パッドの間に半田による電気的な短絡が発生するのを抑制することができる配線基板およびその製造方法を提供することである。

【解決手段】最外層の絶縁層4上に帯状配線導体5Aが複数並設されており、各帯状配線導体5A上の一部に半導体素子の電極端子がフリップチップ接続される導電突起12が形成されており、前記最外層の絶縁層4上および帯状配線導体5A上に、導電突起12の上面12aを露出させるソルダーレジスト層6が被着され、導電突起12の上面12aは、その周囲のソルダーレジスト層6の上面6aよりも低位に位置し、ソルダーレジスト層6によって囲まれた導電突起12の上面12a上に半田層11が形成されている配線基板10およびその製造方法である。

(もっと読む)

プリント配線基板の製造方法

【課題】十分な塗布膜厚、及び塗布領域と未塗布領域の境界線での直線性の確保を両立する熱硬化型ソルダーレジストを有するプリント配線基板を製造する。

【解決手段】電気的絶縁性を有する高分子樹脂を含む基材の表裏両面または片面に電気的導電性を有する金属配線をフォトリソグラフィによって形成し、その金属配線を保護するための熱硬化型ソルダーレジストを、乳剤で覆われていないソルダーレジスト用塗布領域と、乳剤で全部を覆ったソルダーレジスト用非塗布領域とで形成されたスクリーンを用いて塗布する配線基板の製造方法であって、前記スクリーンにおいて使用するメッシュのサイズを♯200〜♯500とし、前記未塗布領域に乳剤を配置するだけでなく、前記塗布領域にも微小な乳剤を均一に分散させて配置する。

(もっと読む)

プリント回路基板及びその製造方法

【課題】マイグレーションの発生及び溶融した半田がランド部間で繋がることによる電気的不具合を防止する。

【解決手段】プリント回路基板1は、基材3に形成した基板回路5と、この基板回路5に設けたランド部11と、このランド部11の外周又は隣り合うランド部11の間に形成したカーボンもしくはカーボンを主成分とする材料からなるカーボン部13と、隣り合う前記ランド部11に半田17で接続する実装部品19と、で構成されていることを特徴とする。

(もっと読む)

多層プリント回路基板およびその製造方法

【課題】多層プリント基板の厚さを減少させるうえ、生産工程を短縮し、生産効率を増大させることが可能な多層プリント基板およびその製造方法の提供する。

【解決手段】多数の回路層および多数の絶縁層を含むビルドアップ層(108)、バンプがプリントされた前記ビルドアップ層(108)の一面の最外層回路層に形成される絶縁樹脂層(101)、および前記ビルドアップ層(108)の他面の最外層に形成される半田レジスト層(112)を含むことを特徴とし、一面にバンプがプリントされた絶縁樹脂層(101)の他面にビルドアップ層(108)、および半田レジスト層(112)を順次積層することにより製造される、多層プリント基板を提供する。

(もっと読む)

配線基板及びその製造方法

【課題】搭載面に露出して形成された複数本の導体パターンの各露出面の全面が金属ろう材層で覆われた配線基板であって、導体パターンの狭ピッチ化によって、隣接する導体パターン間で金属ろう材のブリッジ等が発生する従来の配線基板の課題を解決する。

【解決手段】電子部品が搭載される搭載面に形成された複数本の導体パターン16のうち、少なくとも前記電子部品のバンプが当接する当接面及びその両側面から成る露出面の全面がはんだ層30で覆われており、はんだ層30が溶融されて、導体パターン16に対応する電子部品のバンプと当接して電気的に接続される配線基板10であって、前記当接面が露出して隣接する導体パターン16,16の間を充填する樹脂層32に、導体パターン16の側面を覆うはんだ層30が露出する溝34が、導体パターン16の両側面の各々に沿って形成され、且つはんだ層30が溶融されたとき、溶融状態のはんだが隣接する導体パターン16側に流出することを防止する隔壁が、前記樹脂層32によって形成されている。

(もっと読む)

プリント配線板、及び電子機器

【課題】 実装信頼性の低下を防止できるプリント配線板を提供する。

【解決手段】プリント配線板1は、絶縁層と、絶縁層上に積層され電子部品60が実装される部品実装領域Aを有した導体層と、導体層上に塗布された第1のソルダーレジスト40と、第1のソルダーレジスト40上であって、部品実装領域Aの近傍に塗布されたシルク印刷80と、第1のソルダーレジスト40上であって、少なくともシルク印刷80周囲に塗布された第2のソルダーレジスト50とを有する。

(もっと読む)

部品内蔵型多層プリント配線板及びその製造方法

【課題】内層に配置されたチップ部品の下にベタパターンや配線等の導体が配置されている場合であっても、チップ部品下部及び周辺の導体がリフロー時にショートすることが回避されると共に、チップ部品下部の埋め込み樹脂流れ込み不具合によるボイドの発生も防止することができる部品内蔵型多層プリント配線板の提供。

【解決手段】少なくとも内層にチップ部品が配置され、かつ当該チップ部品の上部及び側方が埋め込み樹脂によって覆われた部品内蔵型多層プリント配線板において、当該チップ部品の下部に、当該埋め込み樹脂を介して被覆樹脂に覆われた導体が配置されている部品内蔵型多層プリント配線板;少なくとも回路形成された内層に、凹溝部を有する被覆樹脂を形成した後、本硬化を行なう工程を有する部品内蔵型多層プリント配線板の製造方法。

(もっと読む)

回路部品内蔵基板およびその製造方法

【課題】回路部品を内蔵する回路部品内蔵基板において、半田リフローの際、回路部品1に接合した半田ボール10が銅箔パターン3へ流出することを防止し、回路部品1と銅箔パターン3の接続を確実に行う。

【解決手段】中層基板4の銅箔パターン3にエッチングレジスト2をかぶせ、回路部品1の半田ボールの位置から所定の距離離れた位置にてエッチングレジスト2をエッチングして開口部分を生成し、当該開口部分をエッチング等してパターン銅箔3の表面を粗くし、凹凸部3aを生成するようにした。

(もっと読む)

はんだ材料を用いて二つのコンポーネントを互いにはんだ付けするための方法

【課題】はんだ材料によって二つのコンポーネントを互いにはんだ付けまたはハイブリダイズするための方法を提供する。

【解決手段】本方法は、コンポーネントの対向する表面上に、はんだ材料によってぬらすことのできる表面を形成する段階と、ぬれ性の表面の一つの上にはんだまたはハイブリダイゼーションパッドを構成することができる適切な量のはんだ材料を堆積させる段階と、脱酸化機能、はんだ材料の再酸化を制限する機能、熱伝達機能、及び、表面張力を低減させる機能を有する液状のフラックス材料を堆積させる段階と、堆積させたはんだ材料に他方のコンポーネントのぬれ性の表面を接触させる段階と、少なくともはんだ材料の融点に達するまで、コンポーネントが配置されているチャンバの温度を上昇させる段階と、を含む。更に、液体のはんだフラックスに関して異なるぬれ性の領域を、コンポーネント上に画定する段階を含む。

(もっと読む)

多層印刷回路基板及びその製造方法

【課題】応力緩和絶縁層のために基板全体の反り、捻れなどを防止できる、信頼性に優れる多層印刷回路基板及びその製造方法を提供する。

【解決手段】本発明に係る多層印刷回路基板の製造方法は、外層回路を備え、−60℃〜150℃での熱膨張係数が10〜20ppm/℃のコア基板を提供するステップと、コア基板の両外側に熱膨張係数が−20〜6ppm/℃の応力緩和絶縁層を積層するステップと、絶縁層上に金属層を形成した後にパッドを形成し、前記パッドと前記外層回路とを電気的に接続させるステップと、を含むことを特徴とする。

(もっと読む)

プリント配線板及びその製造方法

【課題】回路導体の側面に抉れがなく、ソルダーレジストの被覆工程後に回路導体のエッジ部分が剥き出しの状態となる不具合が生じることがない厚い回路導体を備えたプリント配線板とその製造方法の提供。

【解決手段】絶縁層の上下両面に回路導体を備えたプリント配線板であって、当該回路導体の上底の幅が、該回路導体の左右両側面間の最小部幅以下となっているプリント配線板;スプレータイプのエッチング装置を用いて回路形成を行うプリント配線板の製造方法において、少なくとも上面の被回路形成面にエッチング液が溜まらない回路形成工程を有するプリント配線板の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】基板の主面上にチップ型電子部品がはんだで接続、固定され、その主面側が一体に樹脂封止された半導体装置をプリント基板等の実装基板にはんだ付けするリフロー加熱時に、はんだの再溶融流れ出しによる不良発生を防止することができる半導体装置を提供する。

【解決手段】基板1に半導体素子3とチップコンデンサ5を実装した後、封止樹脂を用いた中空封止により封止樹脂部8を形成するに際し、基板1の底面側から基板穿孔部9へ気体を加圧注入することで、封止樹脂部8内に、チップコンデンサ5の端部電極5a、5b及びはんだフィレット部6の全体を被覆する樹脂未充填の空洞10を形成する。

(もっと読む)

回路基板

【課題】 はんだ材の流出を防止してなおかつ、はんだ付け後の部品搭載やワイヤボンディングを阻害しない、実装性の良好なはんだ材流出防止構造を提供する。

【解決手段】 電子部品5を部品搭載部の導体パッド13に掛け渡した状態で、はんだ材4を用いてはんだ材4で固定した後、ワイヤーボンディングパッド14によりワイヤー6を接合するために、はんだ材がワイヤーボンディングパッド7に流出しないための、はんだ流れ出し防止部8を設けた。

(もっと読む)

配線基板

【課題】作業性の悪化を招くことなく、半田付け処理を行う部位以外の配線基板上への不要な半田の付着を防止する。

【解決手段】配線基板1は、基板コア5の両側に導体層7を、さらにその両側に絶縁層となるレジスト層9をそれぞれ備えており、レジスト層9の開口部に露出する導体層7の電極となるランド部13に、電子部品3のリード端子11を半田15により接続する。この半田15による接続部17近傍のレジスト層9上に、凹凸形状部19として、微細な多数の凸部21を、レジスト層9と同様の手法によって形成するか、あるいは、レジスト層9の形成時に一体的に形成する。

(もっと読む)

21 - 40 / 58

[ Back to top ]