Fターム[5E336BB03]の内容

プリント板への電気部品等の実装構造 (16,219) | プリント板の種類 (1,572) | 多層プリント板 (287)

Fターム[5E336BB03]に分類される特許

281 - 287 / 287

フリップチップ搭載用高密度多層プリント配線板

【課題】 孔径25〜300μmのレーザーで孔あけしたブラインドビア孔及び貫通孔を有する高密度の多層プリント配線板を得る。

【解決手段】 少なくとも3層以上の銅箔層を有するフリップチップ搭載用多層プリント配線板において、少なくともフリップチップ搭載部のパッドが各内外層の回路と、少なくとも1孔以上がレーザーで孔あけされた、孔径25〜300μmのブラインドビア孔及びスルーホールの導体で接続され、該内層回路は周囲に広がり、該周囲に広がる回路はブラインドビア孔及び表裏貫通したスルーホール導体を介して、裏面でハンダボールパッドに接続している形態である高密度多層プリント配線板。

【効果】 放熱性に優れ、高密度のスルーホールを有するプリント配線板を得ることができた。加えて、熱硬化性樹脂として多官能性シアン酸エステル樹脂組成物を用いることにより、耐熱性、プレッシャークッカー後の電気絶縁性、耐マイグレーション性等に優れたプリント配線板を作成できた。

(もっと読む)

フリップチップ搭載用高密度多層プリント配線板の製造方法

【課題】 放熱性、孔接続信頼性に優れた高密度の多層プリント配線板の製造方法を提供する。

【解決手段】 フリップチップを搭載する多層プリント配線板において、フリップチップのバンプを接続するパッドを表層に形成し、そのパッドを孔径25〜300μmのスルーホール導体で各層の回路と接続し、該内層の回路はプリント配線板の中央から周囲に広がる回路となっており、該内層回路はスルーホール導体により、少なくとも裏面でハンダボールパッドに接続している形態の高密度プリント配線板の製造方法。

【効果】 放熱性、孔接続信頼性に優れ、高密度のスルーホールを有するプリント配線板の製造方法を提供することができた。加えて、熱硬化性樹脂として多官能性シアン酸エステル樹脂組成物を用いることにより、耐熱性、プレッシャークッカー後の電気絶縁性、耐マイグレーション性等に優れたプリント配線板を作成できた。

(もっと読む)

フリップチップ搭載用高密度多層プリント配線板

【課題】 放熱性、孔接続信頼性に優れたプリント配線板を提供する。

【解決手段】 少なくとも3層以上の銅箔層を有するフリップチップ搭載用多層プリント配線板において、フリップチップ搭載部のバンプ接続用パッドを各内層の回路と孔径25〜300μmのスルーホール導体で接続し、該内層回路からは周囲に広がる回路を形成し、該周囲に広がる回路を表裏貫通した孔径25μm以上のスルーホール導体で、少なくともフリップチップ搭載部の裏面でハンダボールパッドに接続している高密度多層プリント配線板。

【効果】 放熱性に優れ、高密度のスルーホールを有するプリント配線板を得ることができた。

(もっと読む)

多層プリント回路基板

【課題】 多層プリント回路基板の電源層およびグランド層に回り込む集積回路素子の高周波電源電流が原因となる放射ノイズの発生を大幅に低減する。

【解決手段】 電源層とグランド層と信号層とがそれぞれ絶縁層を介して積層され、その表面層に各種集積回路素子が実装された多層プリント回路基板であって、電源層とグランド層との間に挿入されるバイパスコンデンサ30を、電源層とグランド層とが互いに対向する領域を同一形状かつ同一面積で均等に分割した均等分割領域のそれぞれに配置するとともに、均等分割領域の形状を正方形とし、バイパスコンデンサ30をその均等分割領域内のほぼ中心に配置し、かつ、バイパスコンデンサ30の静電容量値を、電源層とグランド層とが対向する領域で形成される基板容量値より大きい値に設定し、バイパスコンデンサ30の合成インダクタンスの値を全て同一に設定する。

(もっと読む)

インターポーザ及びその製造方法とそれを用いた回路モジュール

【課題】半導体チップをインターポーザを介して配線基板に搭載する際に、インターポーザの導電性ビアに起因する信号反射防止、クロストーク等の問題を解消すると共に、セラミック系ベース基板を用いた場合の焼結時の熱収縮や表面粗さによる問題、有機絶樹脂基板を用いた場合の耐熱性の問題をも解消して信頼性の高いインターポーザを実現する。

【解決手段】回路基板のベース基板1を導電性部材で構成し、この基板の中に基板の表裏2つの主表面を電気的に接続する導電性ビア3を設け、導電性ビア3と基板1とを第1の絶縁層2により電気的に絶縁して導電性ビア3を同軸構造とする。回路基板の2つの主表面上には実装用接続端子6、7を設ける。

(もっと読む)

半導体装置のフリップチップ実装基板

【課題】 本発明は、実装密度の高い半導体装置のフリップチップ実装基板を提供することを目的とし、また、放熱性に優れた半導体装置のフリップチップ実装基板を提供することを他の目的とする。

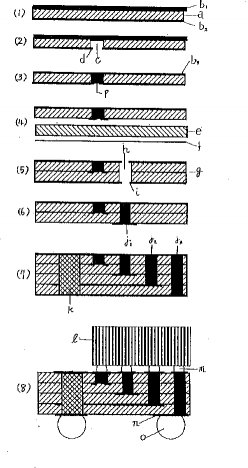

【解決手段】 半導体装置のベアチップ1がフリップチップ実装されるサブ基板2と、このサブ基板が装着されて、前記ベアチップが収容されるマザーボード6とを備え、前記マザーボードには、前記ベアチップが収納されるキャビティ5が形成されているとともに、このキャビティを取り囲む位置に、前記サブ基板の周縁部が嵌合させられる段差部12が形成されている。

(もっと読む)

回路基板

【課題】 内部配線パターンを電源/グランド層によりシールドすることにより特性インピーダンスやクロストークノイズの影響を改善でき、また厚さを薄く形成できる回路基板を提供する。

【解決手段】 コア基板1の両面に内部配線パターン2が形成されており、該内部配線パターン2の上に絶縁樹脂層3を介して電源/グランド層5が各々形成されてなる回路基板4であって、表層の絶縁樹脂層3がドライエッチングにより除去されて形成された凹部6に露出する内部配線パターン2に電子部品7が表面実装可能になっている。

(もっと読む)

281 - 287 / 287

[ Back to top ]