Fターム[5E336BB03]の内容

プリント板への電気部品等の実装構造 (16,219) | プリント板の種類 (1,572) | 多層プリント板 (287)

Fターム[5E336BB03]に分類される特許

141 - 160 / 287

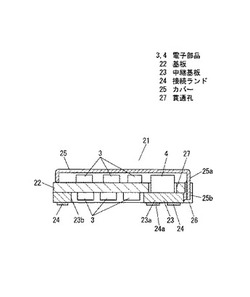

モジュール

【課題】本発明は部品を内蔵するモジュールにおいて、背の高い内蔵部品によってモジュールの高さが決定付けられ、モジュールの高さが厚くなるのを防止することを目的とする。

【解決手段】そしてこの目的を達成するために本発明は、基板22の下面側に接続された中継基板23と、この中継基板23の下面側に設けられた接続ランド24と、基板22の上面に装着された電子部品3と、電子部品3を覆う金属製のカバー25とを備え、基板22には貫通孔27を設けるとともに、中継基板23には貫通孔27を塞ぐように設けられた遮蔽部23aを設け、この遮蔽部23aの上面側には電子部品3の高さよりも高い電子部品4が貫通孔27を貫通するように配置されるものであり、これにより背の高い電子部品4の天面は基板22の厚み分低くなる。従って、その分カバー25と基板22との間の寸法を小さくでき、低背化が実現できる。

(もっと読む)

プリント配線板、プリント配線板の製造方法および電子機器

【課題】内蔵部品を有するプリント配線板に於いて、より回路の簡素化が図れるとともに、配線パターンの引き回しによる電圧降下、信号漏れ等に配慮した自由度の高い高密度回路配線を可能にした。

【解決手段】プリント配線板10は、部品実装面を有する第1の基材11と、この第1の基材11の部品実装面に実装された、貫通電極21a,21bを有する内蔵部品20と、上記第1の基材11に、上記内蔵部品20を覆う絶縁層13を介して積層された第2の基材12と、この第2の基材12に設けられ、上記内蔵部品20の貫通電極21aに連通する穴部に形成されて上記内蔵部品20の貫通電極21aに接合されたビアホール16と、上記第2の基材12に実装されて上記ビアホール16を介し上記内蔵部品20の貫通電極21aに直接回路接続された外装部品(表面実装部品)30とを有して構成される。

(もっと読む)

半導体素子の実装構造体

【課題】本発明は、配線基板に伝達される熱を放熱することによって、配線基板が熱変形するのを抑制し、熱耐性に優れた半導体素子の実装構造体を提供することを目的とする。

【解決手段】平面視において第1方向Xに沿って配置される複数の第1繊維8aと、前記第1方向Xと異なる第2方向Yに沿って配置される複数の第2繊維8bと、を有する配線基板1と、前記配線基板1上に、前記配線基板1に実装される矩形状の半導体素子2と、を備え、前記半導体素子2は、その一辺に沿った直線Lが、平面視して前記第1方向Xに沿った直線Lx及び前記第2方向Yに沿った直線Lyの双方と交わるように配置されていることを特徴とする半導体素子の実装構造体。

(もっと読む)

配線基板及びその製造方法

【課題】配線基板の各層と電子部品との位置精度を向上させることにより、小型化を可能とし、さらに、一括で半導体素子、キャパシタ、抵抗体、及びインダクタ等の電子部品を配線基板内に内蔵させることより、製造時間及びコストを低減させる。

【解決手段】半導体素子、キャパシタ、抵抗、及びインダクタ等の電子部品が内蔵される配線基板において、各層の積層の際に、電子部品が実装されているフィルムキャリアのスプロケットホール等により位置合せを行うことで、配線基板の各層と電子部品との位置精度を向上させることにより、また、技術的に確立されたILB接続技術を用いることにより、半導体素子の狭ピッチ化への対応、接続の信頼性確保、さらには、上層に最短距離で配線を引き出しが可能となり、小型化を実現する。

(もっと読む)

回路装置およびデジタル放送受信装置

【課題】実装密度が向上された回路装置およびそれが組み込まれたデジタル放送受信装置を提供すること。

【解決手段】本形態の回路装置10は、上面および下面に配線層が設けられた基材22から成る配線基板12と、配線基板12の上面および下面に配置された半導体素子34等(第1回路素子)およびパッケージ14等(第2回路素子)とを具備して差し込み実装される回路装置であり、配線基板12を貫通して設けた貫通接続部44を経由して第1回路素子と第2回路素子とが電気的に接続された構成となっている。

(もっと読む)

基板実装方法

【課題】凹部を備える基板を利用して大型部品の実装と他の面実装部品の実装を同じ工程で行い、半田付け箇所のより高い信頼性を確保する基板実装方法を提供する。

【解決手段】孔部に凸部を備えており、凹部と対応する凸部の側壁面と孔部の側壁面とが連続平面上にあるメタルマスクを多層基板にセットするステップと、メタルマスクをセットした多層基板にクリーム半田を印刷するときに、多層基板の配線パターンに印刷するとともに、凹部の側壁面から底面部に沿って形成される配線パターンにもクリーム半田を印刷するステップと、メタルマスクを多層基板から取り外すステップと、多層基板に面実装部品を搭載するときに、凹部に搭載する面実装部品もともに実装するステップと、面実装部品を搭載した多層基板をリフローするステップとを行う基板実装方法である。

(もっと読む)

プリント配線基板とこれを備えたモータ制御装置

【課題】 スルーホール部品のリードからの放熱を防ぎ、半田揚がりを良好にすることができるプリント配線基板と、これを用いたモータ制御装置を提供する。

【解決手段】 スルーホール部品2のリード2aを、両面にパターン配線を形成した2層基板や、内層にパターン配線を形成した多層基板3に形成された全層を貫通するスルーホール3aへ挿入して半田付けし、スルーホール部品2を、部品面に形成された部品面広域パターン3dへ接続するプリント配線基板において、スルーホール部品2を、部品面以外の層で、部品面広域パターン3dと接続する。

(もっと読む)

プリント回路板、プリント回路板の製造方法

【課題】 電子部品の転倒を防止するプリント回路基板を提供する。

【解決手段】 プリント回路板15は、電子機器に収容するために所定の形状を有したプリント配線板18aと、上面18b1及び下面18b2を有し、少なくとも一部がプリント配線板18aの縁部と接続してプリント配線板18aと同一平面を形成する基板18bと、プリント配線板18aを貫通するリード部材28と一部が基板18bの一部と対向する底面20A2を備えた突出部20Aとを有する電子部品20とを備えている。ここで、底面20A2は、基板18bの上面18b1と下面18b2との間に位置し、基板18bは、突出部20Aが基板18bと干渉しないように少なくとも底面20A2と対向する領域の基板18bの厚さを調節している。

(もっと読む)

電子制御装置

【課題】目標とするコイル特性を得ることのできる電子制御装置を提供すること。

【解決手段】基板10には、その二つの表面10a,10bに形成された第1表面配線層21及び第2表面配線層22に加え、同基板10の内部に形成された第1内部配線層23及び第2内部配線層24を有する多層配線基板が用いられる。また、第1表面配線層21上に実装される電子部品11には、コイル26が含まれる。このような場合、第1内部配線層23及び第2内部配線層24において、コイル26に対応する部分には配線パターンを形成しない。

(もっと読む)

半導体内蔵基板及びその製造方法

【課題】製造時においても使用時においても熱応力を緩和することにより、十分な放熱特性及び信頼性を有する半導体内蔵基板を提供する。

【解決手段】本発明による半導体内蔵基板100は、樹脂層1,2,3が積層された3層構造を有する多層基板であり、樹脂層2の内部に、バンプ32が内部配線13及び接続プラグ12を介して端子電極11に接続された半導体装置30が埋め込まれている。この半導体装置30の裏面30bに直上には、開口Hが形成された開口部Pを有する放熱部20が対向配置されており、半導体装置30で生じた熱がその放熱部20へ伝導しそこから放熱される。

(もっと読む)

貫通接続構造物を高密度に備えた積層可能な層構造体及び積層体

【課題】コンパクトな三次元の超小型電子モジュールを周知のプロセスを使用して比較的低価格で製造する。

【解決手段】1以上の集積回路チップ20と1以上の貫通接続構造物25とを備えた積層可能な層構造体1が開示されており、上記集積回路チップ20のI/Oパッド35を層構造体1の第1の面5から1以上の導電性構造物からなる貫通接続構造物25まで導線を使用して電気的に接続し、さらに、上記導電性構造物により集積回路チップ20のパッドを層構造体1の第2の面10の所定部分に電気的に接続し、次に、露出した導電性パッド或は導電性ポストのような上記所定の部分を別の層構造体或は他の回路に相互接続して1以上の積み重ねられた層構造体1から成る三次元の超小型電子モジュールが製造される。

(もっと読む)

電子部品の実装構造及び電子部品の実装方法

【課題】導電性接着材に含まれるはんだ粒子を凝集一体化させて、電子部品を実装する際、品質を損なう端子間ブリッジや未接合バンプや残留粒子の発生を防止する。

【解決手段】はんだチップ2と、パッケージ基板4とが、導電性接着材によって接合され、該導電性接着材に含有されるはんだ粒子が、チップ側電極端子1及び基板側電極端子3のパッド面で、凝集、一体化されて、チップ側電極端子1及び基板側電極端子3とがはんだ接続され、かつ、はんだチップ2とパッケージ基板4との隙間には導電性接着材の樹脂成分(樹脂層9)が充填硬化されている。はんだチップ2の接合面及び/又はパッケージ基板4の接合面には、ダミー電極6、7が設けられていて、ダミー電極6、7には、はんだ粒子のうち、余分なはんだ粒子が吸着されている。

(もっと読む)

多層基板と金属接合材料の印刷方法

【課題】多層基板のキャビティ構造部分に効率よく半田を塗布することができる多層基板への半田塗布とその方法を提供する。

【解決手段】部品面または半田面から中層まで貫通する凹部を設けた多層基板への金属接合材料の印刷方法であって、多層基板に、金属接合材料を多層基板の部品面または半田面の表面上の配線に金属接合材料を印刷するための孔部とマスク部を設けるとともに、凹部の高さ(深さ)と略同じであり、少なくとも凹部開口部から側面を経て底部に設けられた対象とする配線に金属接合材料を付着させるための前記凹部内と勘合する凸部を設けたメタルマスクをセットする工程と、多層基板にセットしたメタルマスクに金属接合材料を塗り込む工程と、メタルマスクを取り除く工程とを行う多層基板への金属接合材料の印刷方法。

(もっと読む)

部品内蔵基板

【課題】 本発明は、接続信頼性を損なうことなく、製造時に煩雑な作業を不要とする、部品内蔵基板を提供することを目的とする。

【解決手段】 本発明は、表面実装されたコア基板と、このコア基板の実装面に配置されるガラスペーパと、このガラスペーパの表面に積層される導電性金属箔又は基板とを備えた部品内蔵基板である。

(もっと読む)

部品内蔵プリント配線板および電子機器

【課題】 剥離し難い部品内蔵プリント配線板を提供する。

【解決手段】 部品内蔵プリント配線板10は、部品接合電極を形成する複数の導電パターンである導体3を部品実装面に設けた基材4と、前記導電パターン相互の間で電気的に接続して実装された電子部品2と、電子部品2を覆う樹脂層1とを備える。部品接合電極である導体3の少なくとも一方に貫通した複数の穴部31を有することで、穴部31から水分やアウトガスの滞留を防止する。

(もっと読む)

チップ部品の実装方法および電子モジュール

【課題】 基板面積を広げることなく、実装部品点数を増やすこと。

【解決手段】 電子モジュール(10A)は、表面(11a)と裏面(11b)と側面(11c)とを持つ実質的に直方体形状をしている。基板(11)は、表面(11a)上に形成された表面導体パターン(12)だけでなく、側面(11c)上に形成された側面導体パターン(22,23)をも持つ。表面実装用チップ部品(14)は、表面導体パターン(12)と電気的に接続されて、基板(11)の表面(11a)上に実装される。側面実装用チップ部品(24,25)は、側面導体パターン(22,23)と電気的に接続されて、基板(11)の側面(11c)上に実装される。

(もっと読む)

配線基板およびその製造方法ならびに半導体装置

【課題】ビア穴を形成する方法によらずに層間で配線パターンを電気的に接続するとともに、配線パターンを高密度に形成することができ、電気的特性および信頼性に優れた配線基板およびその製造方法ならびに半導体装置を提供する。

【解決手段】基板31の表面に、配線パターン40と突部32とが、突部32の頂部32b上に配線パターン40が延出して形成され、配線パターン40が形成された面が絶縁層60により被覆され、突部32の頂部32bに形成された配線パターン40の接続部40cの表面が、絶縁層60の表面と均一高さもしくは絶縁層60の表面よりも低位に露出して形成されている配線基板に半導体素子70が実装された半導体装置であって、接続部40cが、半導体素子70の接続電極に位置合わせして形成された接続用のパッドとして形成され、半導体素子70がフリップチップ接続により接続部40cと電気的に接続して実装されている。

(もっと読む)

配線基板の製造方法、多層配線基板の製造方法

【課題】液滴吐出法を用いて電子部品の周囲に絶縁膜を形成する場合に、該絶縁膜上に形成される配線と前記電子部品との間で良好な導通を得ることを可能とした、配線基板の製造方法、多層配線基板の製造方法を提供する。

【解決手段】導電部20a,21aを有する電子部品20,21を、導電部20a,21aを上方に向けて基体10上に配置するとともに、導電部20a,21a上に導電性を有した突起12を設ける。そして、液滴吐出法を用いて電子部品20,21の周囲に、電子部品20,21と略同じ高さとなるように絶縁材料を塗布し、絶縁材料を硬化させて絶縁膜13を形成する。そして、絶縁膜13上に、突起12に接続する配線15を形成する。

(もっと読む)

多層セラミック電子部品、多層セラミック基板、および多層セラミック電子部品の製造方法

【課題】表面実装型電子部品が実装されるセラミック台座部を備え、高密度実装が可能で、信頼性の高い多層セラミック電子部品、それに用いられる多層セラミック基板、多層セラミック電子部品を効率よく製造するための製造方法を提供する。

【解決手段】セラミック基材層1と、収縮抑制層2とを積層してなる多層セラミック素体3の第1主面4に、セラミック材料からなる台座部本体5と、下側端面6、上側端面7が台座部本体から露出し、下側端面の面積が上側端面の面積より大きい柱状厚膜導体8とを備えたセラミック台座部9であって、柱状厚膜導体の外周面と台座部本体との間に空隙Gを有するセラミック台座部を配設し、セラミック台座部上に、柱状厚膜導体と導通するように第1の表面実装型電子部品10を実装する。

上記空隙Gを、多層セラミック素体に近い下部から多層セラミック素体に遠い上部に向かって大きくなるようにする。

(もっと読む)

プリント回路基板

【課題】 高速DRAMとメモリコントローラとを搭載したプリント回路基板における高速DRAMの安定動作を実現する。

【解決手段】 高速DRAM42とメモリコントローラ41とを搭載したプリント回路基板1において、メモリバス配線43の並列終端抵抗44の接続先であるVTT電源パターン20と、GNDパターン30との間に、コンデンサ45と、VTT電源パターンの特性インピーダンスとほぼ同じ抵抗値を持つ抵抗46との直列接続回路が設けられる。これにより、高速DRAMとメモリコントローラ41との動作に伴いVTT電源パターンに発生あるいは伝搬する高周波ノイズを当該直列接続回路で消費するようにした。

(もっと読む)

141 - 160 / 287

[ Back to top ]