Fターム[5E336BC34]の内容

プリント板への電気部品等の実装構造 (16,219) | プリント板の部分構造 (1,644) | 導電層の構造又は機能が特定されたもの (312)

Fターム[5E336BC34]に分類される特許

101 - 120 / 312

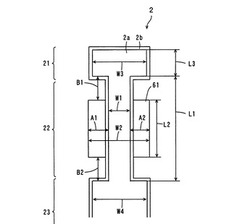

配線回路基板と電子部品との接続構造

【課題】熱融着時における短絡の発生が防止された配線回路基板と電子部品との接続構造を提供する。

【解決手段】各配線パターン2は、導体層2aおよび錫めっき層2bからなり、先端部21、接続部22および信号伝送部23を含む。先端部21の幅と信号伝送部23の幅とは互いに等しく、接続部22の幅は先端部21および信号伝送部23の幅より小さい。電子部品の実装時には、各配線パターン2の接続部22と電子部品の各バンプ61とが熱融着によって接続される。距離A1,A2は、0.5μm以上に設定される。距離B1,B2は、20μm以上に設定される。錫めっき層2bの厚みは0.07μm以上0.25μm以下に設定される。

(もっと読む)

フレキシブル配線体及び液滴吐出ヘッド

【課題】コスト上昇を抑制しながら、フレキシブル配線体における配線の高密度化を実現する。

【解決手段】電気的負荷32と外部信号源側とを接続するフレキシブル配線体4は、基材の一方の広幅面に多数の導線が配線された配線材が複数備えられ、電気的負荷32に対して、複数の配線材41,42が広幅面同士を重ねて積層されている。各配線材における電気的負荷側の広幅面の導線56には、電気的負荷32と接続するための突起状のバンプ体44a、44bがそれぞれ設けられ、電気的負荷32に対して他の配線材41を介して重なる配線材42のバンプ体44bは、他の配線材41に形成された貫通穴43を介して、電気的負荷32と対向するように構成されている。

(もっと読む)

半導体チップの実装構造体

【課題】対向する位置にバンプが形成されていない2個の半導体チップを回路基板上に実装する場合であっても、バンプと回路基板の電極パッドとの間の良好な接触状態を確保できる半導体チップの実装構造体を提供する。

【解決手段】2個の半導体チップ4aおよび4bが回路基板10を挟むように配置され、接着剤3により回路基板10に実装される。半導体チップ4aは、バンプ8a1〜8a4が回路基板10の上面USに設けられた電極パッド2aに圧接された状態で、回路基板10に接着剤3で接合されている。また半導体チップ4bは、バンプ8b1〜8b4が回路基板10の下面LSに設けられた電極パッド2bに圧接された状態で、回路基板10に接着剤3で接合されている。半導体チップ4bのフリーバンプ8b3と対向する回路基板10の裏側には、電極パッド2b3の変形を抑制する変形抑制部材15aが設けられている。

(もっと読む)

回路基板及び回路基板の製造方法

【課題】効率よく製造することができる回路基板及び回路基板の製造方法を提供することを目的とする。

【解決手段】回路基板1は、金属基材2及び前記金属基材2上に設けられたプリント基板3からなる基板本体4と、前記基板本体4上に実装した実装部品5と、前記基板本体4に穿設した貫通穴7に圧入されたスタッド部材6とを備え、前記スタッド部材6により装置本体に固定する。前記基板本体4は、前記貫通穴7の前記プリント基板3側周縁にグランドパターン10を設け、前記スタッド部材6は、半田15を印刷した前記グランドパターン10側から前記貫通穴7に圧入され、前記金属基材2と前記グランドパターン10とを電気的に接続する。

(もっと読む)

プレスフィット端子と基板との接続構造

【課題】端子挿入力を下げても、端子保持力を向上させることができ、信頼性の高い電気的接続を実現できるプレスフィット端子と基板との接続構造を提供する。

【解決手段】本接続構造は、プレスフィット端子3の表面には第1のメッキ層4が被覆され、基板1のスルーホール2の内壁には第2のメッキ層7が被覆され、基板1の内部には熱伝導性を備えたコア層5を有し、コア層5の端部は、第2のメッキ層7又はその近傍まで延びて形成され、第1のメッキ層4と第2のメッキ層7との間を拡散接合させることにより、プレスフィット端子3を基板1のスルーホール2内に保持させる。

(もっと読む)

回路板

【課題】高抗張力銅箔を用いてデバイスホール内に長いフライングリードを有し、複数のデバイスホールを有する配線板にそれぞれ電子部品が安定に実装された回路板を提供する。

【解決手段】絶縁フィルム10からなる一のキャリアに形成された複数のデバイスホール12に電子部品20が実装された回路板において、該配線15が、常態における引張り強さが70kgf/mm2以上の高抗張力銅箔から形成され、該配線15の端部がデバイスホール縁に片持ち状態で複数延設されてインナーリードを形成しており、該デバイスホール12内に延設されたインナーリードの延設長さ(L)が、該インナーリードの線幅(W)に対して、40以上(L/W)であり、電子部品20がデバイスホール12内に収納されてインナーリードと電気的に接続されている。

(もっと読む)

プリント基板およびモジュール構造体

【課題】フローはんだ工法によってはんだをスルーホールに充填しても、250μmを超える高さのはんだ突起が形成されることがないプリント基板を提供する。

【解決手段】積層基材20、50に、スルーホール3を穿設するとともに、スルーホールを露出させる開口を有する絶縁保護膜42、62を積層基材の裏面に形成して、積層基材の露出面に金属メッキ24、25を施すことにより積層基材の裏面における絶縁保護膜の開口に第2のランド24b、25bを形成したプリント基板1、5とした。スルーホールを半径R≦0.75mmの横断面円形状に形成するとともに、上記第2のランドをπ(0.6R+0.09) mm2以下の環状に形成した。または、スルーホールを0.75mm<半径R≦1.0mmの横断面円形状に形成するとともに、上記第2のランドをπ(0.2R+0.01) mm2以下の環状に形成した。

(もっと読む)

電子部品搭載基板及び電子部品搭載方法

【課題】 電子部品を電子部品搭載基板に載せ換えるための仮搭載と、電子部品を電子部品搭載基板に固定して本搭載することを容易に確実に行うようにする。

【解決手段】 電子部品のリード端子2と接続される配線層端子6を備える電子部品搭載基板3において、配線層端子6のリード端子2と接続される部分にリード端子2の全長に対して短い長さにわたり凹部7を形成し、凹部7の内壁に配線層端子6と連なる導電層8を形成し、載せ換えの際の仮搭載では、リード端子2を折り曲げて凹部7に嵌合させて配線層端子6と接続させ、固定して本搭載する場合には、リード端子2と配線層端子6とを半田付けして固着する。

(もっと読む)

実装基板およびリード付き電気素子

【課題】従来、扁平形電気素子では、プリント基板実装後に、不良実装素子をプリント基板から外して交換するため、はんだコテを用いて手作業で不良素子を外すことがあるが、従来の扁平形電気素子では、はんだが電気素子の影に隠れて、不良素子を外すことが困難となり、結果、リワークが困難であった。

【解決手段】リード付きコイン形電池20において、2つのリード22,23の各々を、コイン形電池21の主面21a,21bの縁よりも内側の領域に、当該主面21a,21bに交差する方向に折り曲げられてなる折曲部分22a,23aを備えさせた。

(もっと読む)

電子回路モジュールおよび多層配線板

【課題】集積回路を多層配線板にフリップチップ接続する際に、多層配線板に対して集積回路が傾いてしまうことを抑制することにより、集積回路のバンプを多層配線板の接続電極に確実に接続することができる電子回路モジュールおよび多層配線板を提供すること。

【解決手段】本発明の電子回路モジュール1は、多層配線板3および集積回路2を備える。また、本発明の多層配線板3は、樹脂製の多層樹脂基板4、接続電極5および内層電極6を備える。多層配線板3は、接続電極5および内層電極6が最も積層された最多積層箇所7を集積回路2の四隅に1箇所ずつ有している。また、合計4箇所の最多積層箇所7は、最多積層箇所7を頂点として隣位する最多積層箇所7を結ぶことにより形成される四角形の内側に集積回路2の重心2gが重なるように配置されている。

(もっと読む)

回路基板

【課題】 はんだ材の流出を防止してなおかつ、はんだ付け後の部品搭載やワイヤボンディングを阻害しない、実装性の良好なはんだ材流出防止構造を提供する。

【解決手段】 電子部品5を部品搭載部の導体パッド13に掛け渡した状態で、はんだ材4を用いてはんだ材4で固定した後、ワイヤーボンディングパッド14によりワイヤー6を接合するために、はんだ材がワイヤーボンディングパッド7に流出しないための、はんだ流れ出し防止部8を設けた。

(もっと読む)

プリント配線基板

【課題】プリント配線基板において、スルーホールの外縁のうち、端子の圧入端となる入口部は端子よりも小径に形成されており、スルーホールに端子を圧入する際には、入口部が端子の表面に接触し、入口部と端子は強く摩擦する。この摩擦によって端子のメッキ層が削られると、剥がれ落ちた破片や削り屑がプリント配線基板の表面に付着し、回路を短絡させる問題がある。

【解決手段】基板と、該基板に形成されている導電部と、該基板に穿設され外縁の少なくとも一部に該導電部が表出しているスルーホールを備え持つプリント配線基板において、前記スルーホールは、周方向に面取りされた形状に形成され、かつ、入口部の厚さ方向の断面が略円弧状に形成されていることを特徴とするので、端子を取り付けする際に端子のメッキ層の破片や削り屑が生じ難くなることで、導電部からなる回路を短絡させる問題を解消できる。

(もっと読む)

基板およびその製造方法、半導体パッケージおよびその製造方法、並びに半導体装置およびその製造方法

【課題】半導体パッケージの端子の狭ピッチ化を可能とすると共に、半導体パッケージ間の距離を確保することで高実装化を図った半導体装置等を提供する。

【解決手段】回路基板10は、ソルダーレジスト層16上に形成された開口部62を有するポスト部形成層28と、開口部60,62の連通した孔内部に形成されたポスト部28と、ポスト部28の先端部に形成されたはんだボール18とを備える。半導体パッケージ30は、半導体チップ42と電極パッド34とを備える。半導体装置100は、回路基板10のはんだボール18と半導体パッケージ30の電極パッド34とがリフローにより電気的に接続されて構成される。回路基板10のポスト部28の高さを調節することによって回路基板10および半導体パッケージ30間の距離を調整できる。

(もっと読む)

電子部品実装基板の製造方法及び電子部品実装基板

【課題】電子部品とプリント配線板との接続不良を低減し、半田ボールの発生を防止可能な電子部品実装基板の製造方法及び電子部品実装基板を提供する。

【解決手段】基材18上にランド部12と該ランド部が露出する第1開口部14及び第2開口部15を有するソルダーレジスト16とを形成してプリント配線板10を作製し、このプリント配線板にクリーム半田20を塗布した後に電子部品をクリーム半田を介して載置し、このプリント配線板を所定温度に加熱してさらに冷却することによって電子部品実装基板を得る手順を有し、ソルダーレジストを形成する際、第1開口部をランド部上の所定範囲に、第2開口部をランド部上の第1開口部の周部よりも外側に第1開口部を囲うように形成すると共に、第1開口部及び第2開口部が形成された範囲並びにソルダーレジストが第1開口部と第2開口部との間に介在する範囲にクリーム半田を塗布する。

(もっと読む)

積層型電子部品の実装構造

【課題】インダクタンスを低減することができる、積層コンデンサのような積層型電子部品の実装構造を提供する。

【解決手段】積層コンデンサ21の内部電極24と配線基板36の表面導体40とが互いに面対向するように配置し、外部端子電極27と表面導体40とが電気的に接続された状態で、配線基板36上に積層コンデンサ21を実装する。内部電極24の引出し方向であって実装面37と垂直な方向に延びる仮想平面に投影したとき、内部電極24を流れる電流45の方向と、表面導体40からビア導体41に向かって流れる電流46の方向とが逆向きとなるように、ビア導体41を配置する。

(もっと読む)

モジュラ電気システム

本発明は、モジュラ電気システムであり、基板3、12、電源40、電力/データ伝送手段4、16及び保持手段を有するベースモジュール2、11と、電気的負荷、電力/データ受け取り手段8、26及び保持手段を有する少なくとも1つのロードモジュール7、20、30とを備えるモジュラ電気システムであって、前記ロードモジュールが、第1及び第2位置において前記基板に配置可能であるよう適合させられ、前記第1位置(接続位置)において、前記ベースモジュールの前記伝送手段4、16が、前記ロードモジュール7、20、30の前記受け取り手段8、26と相互に作用し、前記第2位置(反発位置)において、前記伝送手段4、16と前記受け取り手段26との相互作用が、許容されない又は可能ではないモジュラ電気システムに関する。前記モジュラ電気システムは、前記ベースモジュール及び前記ロードモジュールの前記保持手段が、磁石素子5、9、49、59であって、前記ロードモジュール7、20、30が、前記第1位置においては、着脱可能に保持され、前記第2位置においては、保持されないように、互いに対して配置される磁石素子5、9、49、59を有することを特徴とする。  (もっと読む)

(もっと読む)

配線基板

【課題】発光素子の搭載面を有するセラミック層を備え、前記発光素子の熱を効率良く放熱でき、且つ所要の配線層を内部に自在に形成できると共に、簡単で且つ少ない工程で製造可能な配線基板を提供する。

【解決手段】発光ダイオード(発光素子)18の搭載面6を有し且つWまたはMoなどの金属成分を含有するセラミック層s1(s11〜s13)と、上記搭載面6において、その3分の2以上の面積で形成され、且つ表層にAgメッキ膜12およびAuメッキ膜13の少なくとも一方が被覆されているパッド(導体)8a,9aと、上記金属成分を含有するセラミック層s1の搭載面6(上層)側に積層され、当該搭載面6とかかる搭載面6の周辺から斜めに立ち上がる側面7aとからなるキャビティ5aを形成すると共に、上記金属成分を含有するセラミック層s1よりも白色度が大きいセラミック層s21と、を含む、配線基板1a。

(もっと読む)

プリント基板およびプリント基板ユニット並びに導電体の上がり量検出方法

【課題】導電体の上がり量を確実に検出することができるプリント基板およびプリント基板ユニットを提供する。

【解決手段】基板14の貫通孔23は絶縁体で空間を仕切る。貫通孔23は電子部品15のリード端子28を受け入れる。リード端子28は導電体29に接触する。導電体29は基板14の第1面および第2面の少なくともいずれかで露出する。貫通孔23内の空間には任意の絶縁層17同士の間から導電パターン24、25、26、27が臨む。導電パターン24、25、26、27は、基板14の第1面および第2面の少なくともいずれかで露出する導電材33、34、37、38のいずれかに接続される。リード端子28と導電材33、34、37、38のいずれかとの間で導通の確立の有無が検出される。導通が検出されれば、導電体29が導電材33、34、37、38の位置まで上がっていることが確認される。導電体29の上がり量は確実に検出される。

(もっと読む)

回路装置及びデジタル放送受信装置

【課題】接続電極の増加に伴うサイズの増大を抑制する。

【解決手段】少なくとも一方の面側に配線層を有する配線基板と、配線基板の一方の面に配設され、配線層と接続される回路素子と、配線基板の一方の面に配設され、配線層と接続される複数の接続電極と、を備え、複数の接続電極の配線基板の一方の面から突出する高さが、回路素子の配線基板の一方の面から突出する高さより低く、複数の接続電極が他の配線基板の一方の面に配設された複数の接続部と当接されるとともに、回路素子が他の配線基板の一方の面と干渉しない位置に配設されることにより接続可能である。

(もっと読む)

プリント配線板、プリント配線板の電極形成方法およびハードディスク装置

【課題】フリップチップ実装される半導体素子接合用の電極を、ソルダーレジスト被膜により規定した配線パターンの露出部分により形成したプリント配線板に於いて、強固なはんだ接合を可能にするとともに、接合部の高密度化が図れるプリント配線板を提供する。

【解決手段】プリント配線板11は、フリップチップ実装される半導体素子の実装面部に所定の間隔を存して配列された、半導体素子接合用の電極形成部分を有する多数本の配線パターン12p,12P,…と、部品実装面部を電極形成部分を残しソルダーレジスト(SR)で被覆することにより電極形成部分に露出形成された多数の電極12,12,…と、各電極12,12,…に一体に設けられ、半導体素子の電極に接合する部分の電極幅を他の部分より広幅に形成し、この広幅の部分が上記電極の配列方向に隣接しないように該電極の延長方向に位置的にずらせて配置した電極拡張部12a,12a,…とを有して構成される。

(もっと読む)

101 - 120 / 312

[ Back to top ]