Fターム[5E339BD01]の内容

プリント配線の製造 (8,867) | 導体層の形成、パターン化 (920) | 特定区域への導体層の形成 (42)

Fターム[5E339BD01]の下位に属するFターム

スルーホール部への形成 (27)

Fターム[5E339BD01]に分類される特許

1 - 15 / 15

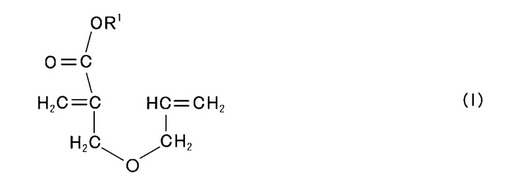

剥離レジスト形成用硬化性組成物

【課題】低粘度で吐出性に優れ、かつ耐熱性、エッチング耐性、めっき耐性など各種耐性に優れる剥離レジスト形成用硬化性組成物、及びその硬化物並びにそれを用いた電子回路基板を提供する。

【解決手段】式(I):

(R1は、水素原子又は1価の有機基。有機基は、エーテル基、ハロゲン原子を有していてもよい。)で表わされる化合物を含むことを特徴とする。

(もっと読む)

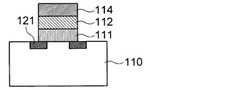

薄膜電極セラミック基板及びその製造方法

【課題】本発明は、薄膜電極セラミック基板及びその製造方法に関する。

【解決手段】薄膜電極セラミック基板は、セラミック基板と、セラミック基板の表面に形成されたエッチング防止金属層と、エッチング防止金属層上に形成された薄膜電極パターンと、薄膜電極パターン上に形成されたメッキ層と、を含み、薄膜電極パターンの各エッジ部は前記エッチング防止金属層と接することを特徴とする。薄膜電極セラミック基板は、セラミック基板の表面に陰刻形状のエッチング防止金属層を形成することにより、セラミック基板の表面と薄膜電極パターンとの間、及び薄膜電極パターンの間でエッチング液によって発生するアンダーカットを防止できる。また、薄膜電極パターンのエッジ部のセラミック基板表面の金属層に対する接着力が向上されることができ、薄膜電極パターン全体の固着力を向上させることができるため、薄膜電極パターンの耐久性及び信頼性を確保できる。

(もっと読む)

回路基板の製造方法およびウェットエッチング装置

【課題】金属膜のウェットエッチングの終点を的確に検出できる回路基板の製造方法を提供する。

【解決手段】回路基板の製造方法は、基板上に、少なくとも第1の金属材料よりなる第1の金属層を介して、前記第1の金属材料とは異なる第2の金属材料よりなる第2の金属層を形成する工程と、前記第2の金属層上に第3の金属材料よりなる金属配線パタ―ンを形成する工程と、前記金属配線パタ―ンの形成工程の後、エッチング液中におけるウェットエッチングにより前記第2の金属層をエッチングし、前記第2の金属層を前記第1の金属層に対して選択的に除去するエッチング工程と、を含み、前記ウェットエッチング工程は、前記エッチング液中における前記第2の金属層の浸漬電位の時間変化を測定する工程を含み、前記浸漬電位がいったん降下した後上昇に転じ、その後さらに前記浸漬電位の時間変化率が減少したのが検出された場合に、前記ウェットエッチング工程を終了する。

(もっと読む)

配線基板の製造方法

【課題】損傷の少ない、良好な導電率となる導電膜が形成される配線基板の製造方法を提供する。

【解決手段】基板101上の導電膜形成予定位置Pに、有機材料がコーティングされた導電性材料を分散溶媒中に分散させてなる金属微粒子分散インク102を塗布する。

基板101に塗布された金属微粒子分散インク102の分散溶媒を揮発させて導電性材料の堆積膜102Aを形成する。加熱により発泡する発泡カプセルを混合した保護膜103で堆積膜102Aを覆い、除去対象物Eをエッチングする際に堆積膜102Aを保護する。除去対象物Eをエッチング後、基板101を焼成して保護膜103の発泡カプセルを発泡させて多数の通気孔105を形成すると共に、堆積膜102Aの導電性材料に含まれる有機材料のガスを通気孔105を介して放出させる。このように堆積膜102Aからガスを放出させて導電膜102Bを形成する。

(もっと読む)

電子回路形成方法、電子回路及び電子回路形成用銅張積層板

【課題】銅層のエッチングによるダレを防止し、均一な回路幅を形成して、配線の直線性を良好にする。

【解決手段】銅層のエッチング面側に、銅よりエッチングレートの遅い層を形成すると共に、前記銅層の非エッチング側の面を樹脂基板に張付け、エッチング面に回路形成用レジストパターンを形成する。銅よりエッチングレートの遅い層を先にエッチングした後、次に銅層をエッチングして、樹脂基板上に電子回路を形成することで回路形成時のサイドエッチングを抑制し、高いエッチファクタを可能であるだけでなく、エッチングに先立ち、エッチングされるべき銅箔の直上にある表面処理層を予め除去するプリエッチング工程を導入することで、目的とする回路幅の、より均一な回路を形成でき、パターンエッチングでのエッチング性の向上、ショートや回路幅の不良の発生を防止できる銅箔及び電子回路形成用銅張積層板並びにこれを用いた電子回路基板を提供する。

(もっと読む)

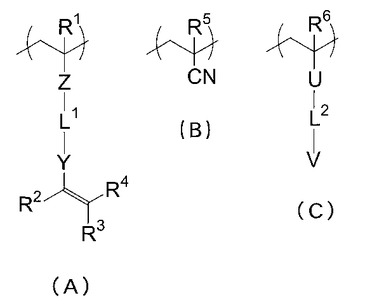

絶縁性樹脂、絶縁性樹脂層形成用組成物、積層体、表面金属膜材料の作製方法、金属パターン材料の作製方法、配線基板の作製方法、電子部品、半導体素子

【課題】めっき触媒又はその前駆体との吸着性及び加水分解に対する耐性に優れた絶縁性樹脂、絶縁性樹脂層形成用組成物、基板との密着性に優れた金属膜又は金属パターンを簡易に形成しうる積層体、表面金属膜材料及び金属パターン材料の作製方法を提供する。

【解決手段】下記式で表されるユニットを含み、(C)で表されるユニットの含有率が共重合体に含まれる全ユニット中20モル%未満である共重合体からなる絶縁性樹脂。 (もっと読む)

(もっと読む)

プローブ基板の製造方法

【課題】 配線パターンに応じた凹凸や段差が当該配線パターンを構成する導電層上の絶縁層の表面に生じるのを抑制することができるプローブ基板の製造方法を提供する。

【解決手段】 配線基板上に導電層からなる第1配線パターンを形成する第1配線パターン形成ステップと、第1配線パターンの形成後の配線基板上に第1絶縁層を形成する第1絶縁層形成ステップと、第1配線パターンに対応する第1絶縁層の領域を選択的に露光させる第1絶縁層露光ステップと、露光された第1絶縁層を除去する第1絶縁層除去ステップと、第1絶縁層の除去後に第2絶縁層を形成する第2絶縁層形成ステップからなる。

(もっと読む)

電気的固体装置の製造方法、電気的固体装置、および電気光学装置

【課題】ウエットエッチングを採用した場合でも、未エッチング部分を発生させずに微細なパターンを形成することができる電気的固体装置の製造方法、電気的固体装置、および電気光学装置を提供すること。

【解決手段】電気光学装置の素子基板上に、スリット7bを備えた透光性の画素電極7aを形成するにあたって、透光性導電膜7の上にレジストマスク96を形成した後、ウエットエッチングを行なう。レジストマスク96において、マスク開口部96bを挟むマスク線状部96eの側面部96fは斜め上向きのテーパ面になっている。

(もっと読む)

配線回路基板の製造方法

【課題】工数を低減して、生産効率の向上を図ることができる配線回路基板の製造方法を提供すること。

【解決手段】金属支持基板7と、金属支持基板7の上に形成されるベース絶縁層8と、ベース絶縁層8の上に形成され、端子14および端子14から連続するめっきリード16を備える導体パターン9と、導体パターン9を被覆するように、ベース絶縁層8の上に形成されるカバー絶縁層10とを形成し、金属支持基板7をエッチングした後、ベース絶縁層8をエッチングして、金属支持基板7およびベース絶縁層8から、めっきリード16を露出させ、露出させためっきリード16をエッチングする。

(もっと読む)

チップ搭載用基板の製造方法

【課題】銅配線間のニッケルの異常析出が生じることもなく、Niブリッジを減少させることと、チップの実装のズレを防止することと、銅配線の線幅が細くなることを防止して銅配線のはく離を防止することを同時に達成するチップ搭載用基板の製造方法を提供する。

【解決手段】基板1表面に形成した銅配線2を覆うエッチングレジスト3を設ける工程と、前記銅配線2表面が露出するまで前記エッチングレジスト3を除去する工程と、前記銅配線2を途中までエッチングする工程と、前記エッチングレジスト3をはく離する工程とを有する。

(もっと読む)

積層回路基板の製造方法

導電パターンを特徴とする回路基板の製造方法であって、i)最終生産物のための所望領域(3a)と最終生産物における導電性領域間の狭小領域(3c)とを備える金属箔(3)などの導電層の一部は、ボンド(2)によって基板物質(1)に接着され、

例えば金属箔(3)などの導電層において後に除去されるさらに広範囲の領域(3b)は、基板物質と実質的に非接着状態で残っており、除去領域(3b)は、続く工程ii)でパターン化される予定の縁部分よりも小さい部分、可能であれば、続く工程iii)の前に除去領域が解放されるのを防ぐ領域にて、基板物質と接着するように、金属箔(3)などの導電層を基板物質(1)へ選択的に接着する工程と、ii)導電パターンを確立するために、所望の導電性領域(3a)間の微小ギャップと、固体状態で除去可能な領域(3b)の外側周囲から、材料を除去することにより、金属箔(3)などの導電層をパターン化する工程と、iii)工程ii)において除去領域の外側周囲から除去された導電層の縁領域が、基板物質と縁が接着している除去領域(3b)をもはや保持しなくなった後に、基板物質(1)に付加されていない除去領域(3b)を金属箔(3)などの導電層から除去する工程、とを備える回路基板の製造方法。  (もっと読む)

(もっと読む)

電極回路付キャパシタ層形成材の製造方法

【課題】プリント配線板のキャパシタ層を構成するために用いる電極回路付キャパシタ層形成材に対し、ブラスト処理を用いて、上部電極間に露出した誘電層を除去しても、キャパシタ品質の変化が少ない製造方法を提供する。

【解決手段】上記課題を達成するため、誘電体層の片面に仮上部電極回路を備え、他面側に下部電極回路用の導電体層を備え、仮上部電極回路と仮上部電極回路との間に誘電体層が露出した状態の第1仮上部電極回路付キャパシタ層形成材を準備し、この第1仮上部電極回路と第1仮上部電極回路との間に露出した誘電体層をブラスト処理を用いて除去した第2仮上部電極回路付キャパシタ層形成材を得て、当該第2仮上部電極回路付キャパシタ層形成材の第2仮上部電極回路の外周縁端部をエッチング除去して上部電極回路とすることを特徴とした電極回路付キャパシタ層形成材の製造方法等を採用する。

(もっと読む)

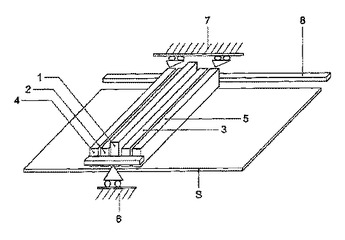

スタンピング方法及び装置

【解決手段】基板(S)上にスタンプ形状部(P)を形成する方法は、基板の少なくとも一方の表面に複数のスタンピングツールセグメント(32,40a,40b,40c,50,60,70,80,92)を押し当てる段階を含む。基板(S)上にスタンプ形状部(P)を形成する構成(30,90)は、個々に、一以上からなるグループで協調的に、又はそれらの組み合わせで動作可能な複数のスタンピングツールセグメント(32,40a,40b,40c,50,60,70,80,92)を含む。 (もっと読む)

セラミックス回路基板及びその製造方法

【課題】回路パターン部とセラミックス基板との間に隙間が形成されており、且つ前記隙間にエッチング残渣が残るのを防止できる耐熱衝撃性に優れたセラミックス回路基板及びその製造方法を提供する。

【解決手段】本発明に係るセラミックス回路基板は、セラミックス基板1上に形成されたろう材パターン8,9と、前記ろう材パターン上に接合された回路パターン部と、を具備し、前記ろう材パターンは、前記回路パターン部の端部に沿ったろう材パターンを有し、前記セラミックス基板と前記回路パターン部との間には前記ろう材パターンの内側に位置する隙間が形成されていることを特徴とする。

(もっと読む)

基板に対して構造体を正確に塗布するための方法および装置

基板が設けられ、走査ステップでは、処理ヘッドの少なくとも1つの走査設備により、基板に対して既に塗布された構造体が検出され、処理ヘッドには少なくとも1つの照明設備が設けられ、この照明設備は、照明ステップにおいて、走査ステップを用いて得られた情報を使用することにより、塗布されたラッカー構造体を局部的に照明する方法。また、この方法を行なうための装置が記載されている。この装置には、基板キャリアに対して移動可能な処理ヘッドが設けられ、処理ヘッドは、少なくとも1つの走査設備と少なくとも1つの照明設備とを備えている。  (もっと読む)

(もっと読む)

1 - 15 / 15

[ Back to top ]