Fターム[5E346AA33]の内容

多層プリント配線板の製造 (97,916) | 多層の形状、構造 (21,562) | 層相互の形状、構造が特定されたもの (4,419) | 導体層と誘電体層 (211)

Fターム[5E346AA33]に分類される特許

1 - 20 / 211

コアレス構造多層配線板及びその製造方法

【課題】アンカー効果に依存しないでも回路を形成する金属層との接着力を向上させることが可能で、反りの発生が低減されたコアレス構造多層配線板の製造方法及びコアレス構造多層配線板を提供する。

【解決手段】剥離可能な銅箔上に接着層X1が形成されてなる銅箔フィルムの前記接着層X1上に、接着層A1と絶縁樹脂層とからなる絶縁フィルムの前記絶縁樹脂層を貼り合わせ、硬化処理を施してこれらのフィルムを積層する積層工程を含み、かつ、前記積層工程後に、(1)接着層A1上にセミアディティブ法により回路を形成する回路形成工程、(2)前記銅箔フィルムの銅箔を剥離する銅箔剥離工程と、銅箔剥離後の接着層X1の所定位置にビアホールを形成するビアホール形成工程と、ビアホール形成後に接着層X1上にセミアディティブ法により回路を形成する回路形成工程、を含むコアレス構造多層配線板の製造方法及びコアレス構造多層配線板である。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

電子部品及びその製造方法

【課題】拘束層材料と素子層材料の電子特性との相対的な関係を選択することにより、側電極の深さを全体的な電気の影響を最小限に抑える。

【解決手段】電子部品およびその製造方法は、まず、第二電子特性を有する拘束層を第一電子特性を有する素子層に形成する。前記電子部品の特性は、前記第一電子特性によって主に影響される。その後、両方の拘束層及び素子層を焼結温度で焼結する。第一電子特性と第二電子特性との関係を選択することにより、電子部品の特性が安定になる。

(もっと読む)

多層配線基板およびその製造方法、並びに半導体装置

【課題】薄膜キャパシタの導電層と誘電層との界面での剥離を抑えることが可能な多層配線基板およびその製造方法、並びにこの多層配線基板を備えた半導体装置を提供する。

【解決手段】上部電極および下部電極の間に誘電層を有する薄膜キャパシタを備えた機能領域と、前記機能領域以外の周辺領域とを有し、前記周辺領域の少なくとも一部に、前記誘電層および導電層が積層された係留部が設けられ、前記導電層の前記誘電層に接する面のラフネスが、前記上部電極または前記下部電極の前記誘電層に接する面のラフネスよりも大きい多層配線基板。チップおよび前記多層配線基板を備えた半導体装置。

(もっと読む)

多層基板

【課題】層間密着性に優れ、高温高湿の環境下においても誘電特性の変動が少なく、伝送損失の小さい、シールドストリップラインを備えた多層基板を提供すること。

【解決手段】伝送線路が埋設された第一の誘電体層の少なくとも片面に導体層を積層してなる回路板の両面に、第一の誘電体層よりも高い比誘電率を有する第二の誘電体層を積層してなる積層板を含んでなり、第一の誘電体層は脂環式構造含有ポリマーを含む架橋性樹脂成形体(I)を硬化してなるものである、多層基板。

(もっと読む)

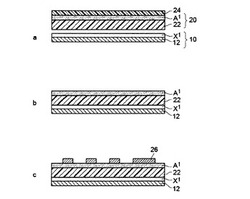

車両用多層配線基板、およびこの基板を用いた車両用電動コンプレッサ

【課題】コンデンサを搭載することなくノイズ低減することができる車両用多層配線基板を提供することを目的とする。

【解決手段】車両のボディ4に接地する低電圧用金属グランドパターン24を形成した低電圧グランド層21と、車両のボディ4と絶縁する高電圧用金属グランドパターン25を形成した高電圧グランド層22とを有し、基板材20を挟んだ一方の面が低電圧グランド層21であり、他方の面が高電圧グランド層22である車両用多層配線基板である。

(もっと読む)

プリント配線板

【課題】高速伝送を実現しつつも設計が容易なプリント配線板の構造を提供する。

【解決手段】

第1絶縁層10の一方主面に形成されたグランド層30と、他方主面に形成された信号線41と、第1絶縁層10の他方主面に形成され、信号線41を挟んで並設された2本の導電線42と、信号線41と導電線42とを覆う第2絶縁層20と、を備え、第2絶縁層(絶縁層A)20の誘電正接A>第1絶縁層(絶縁層B)10の誘電正接Bである場合は、関係式1:比誘電率B×信号線41の幅(W41)÷第1絶縁層(絶縁層B)10の厚さ(T10)>比誘電率A×{信号線41の厚さ(T41)÷信号線41と一方の導電線42aとの距離(S1)+信号線41の厚さ(T41)÷信号線41と他方の導電線42bとの距離(S2)+信号線41の厚さ(T41)÷一対の信号線(41a、41b)間の距離(S3)×2)}を満たす。

(もっと読む)

EBG構造及び基板

【課題】低周波数帯域のバンドギャップ特性を得ることが可能であり、小型化可能であるEBG構造、及びそれを備える基板を提供する。

【解決手段】本発明の一実施形態に示されるEBG構造は、導体層101と、導体層101とキャパシタンスを形成する導体層102と、導体層102にビア104aを介して接続される導体層103を有し、導体層103は導体板113a、113b、113c、113dから構成され、導体板113a、113b、113c、113dとビア104aとは導体線105a、105b、105c、105dを介してそれぞれ接続されているので、低周波数帯域のバンドギャップ特性を得ることができる。

(もっと読む)

プリント配線板およびその製造方法

【課題】本発明は、キャビティを形成する時の切断時間を短縮することのできるプリント配線板およびその製造方法を提供する。

【解決手段】プリント配線板の製造方法は、まず、開口を有する基板、第1配線層および第2配線層を提供する。開口は、基板を貫通する。基板は、第1表面、および第1表面と向かい合う第2表面を有し、第1配線層と第2配線層は、それぞれ第1表面と第2表面の上に配置される。それから、開口の中に離型層を形成する。第1表面と離型層の上に、第1ビルドアップ配線構造を形成する。第2表面と離型層の上に、第2ビルドアップ配線構造を形成する。続いて、離型層の周囲に沿って、第1ビルドアップ配線構造を切断する。その後、離型層と離型層の上にある既に切断された部分の第1ビルドアップ配線構造を除去して、キャビティを形成する。

(もっと読む)

プリント配線板及びその製造方法

【課題】ビルドアップの流れの中でコンデンサ部を形成することができるプリント配線板を提供する。

【解決手段】プリント配線板10では、上部電極接続部52は、上部電極接続部第1部52aがコンデンサ部40と接触することなくコンデンサ部40を上下方向に貫通し、コンデンサ部40の上方に設けられた上部電極接続部第3部52cを経て上部電極接続部第2部52bから上部電極42に繋がっている。また、下部電極接続部51は、コンデンサ部40の上部電極42とは接触しないが下部電極41とは接触するようにコンデンサ部40を上下方向に貫通している。このため、ビルドアップしていく流れの中で、2枚の金属箔で高誘電体層を挟んだ構造を有し後にコンデンサ部40となる高誘電体キャパシタシートでもって全面を覆ったあとでも、上部電極接続部52や下部電極接続部51を形成することができる。

(もっと読む)

積層回路基板

【課題】 寸法を小型に保ちながら、特性を劣化させることなく、設計自由度の高い積層回路基板を提供する。

【解決手段】誘電体層35の表面には、導体ペーストを印刷してなる加圧部材40が形成されている。積層方向から見て、この加圧部材40はコンデンサ電極38bと重なっている。この加圧部材40によって、積層回路基板30の製造時に、容量C1の容量値を大きくできる。

(もっと読む)

電磁結合構造、多層伝送線路板、電磁結合構造の製造方法、及び多層伝送線路板の製造方法

【課題】高密度に集積できる電磁結合構造、多層伝送線路板、及びそれらの製造方法を提供すること。

【解決手段】マイクロ波帯の周波数帯域で使用される電磁結合構造であって、内側誘電体層23が、複数のグランド層となる内側導体層12、15の間に挟まれて積層された積層体と、積層体を間に挟んで対向する一対の外側誘電体層21、25と、一対の外側誘電体層21、25を間に挟んで対向する一対の外側導体層11、16と、を備える。積層体には、内側誘電体層23及び複数のグランド層となる内側導体層12、15を貫通する孔Sが設けられており、孔Sの内壁に形成された管状の金属膜3を介して、複数のグランド層となる内側導体層12、15が電気的に接続されることにより、一対の外側導体層11、16が電磁結合されることを特徴とする。

(もっと読む)

表面実装素子および埋め込み素子用の放電保護

電圧切り替え型誘電体材料(VSDM)を含むプリント回路ボードが開示される。このVSDMは、プリント回路ボード上に配置されるかあるいはその中に埋め込まれた電子素子を、静電放電のような放電あるいは電気的な過大ストレスに対して保護するために用いられる。過大電圧事象の間、VSDM層は過剰電流をアースに分路し、それによって電子素子の破壊または損傷を防ぐ。 (もっと読む)

電子基板に組み込まれたビア構造

基板に配置されたビア構造のシステム。当該システムは、基板に配置された外側導電層と、内側絶縁層と、内側導電層とを備える第1ビア構造を有する。外側導電層は内側絶縁層と基板とを分離し、内側絶縁層は内側導電層と外側導電層とを分離する。第1相補的対の第1信号が内側導電層を通過し、第1相補的対の第2信号が外側導電層を通過する。別の実施形態では、電子基板にビア構造を形成する方法が提供される。  (もっと読む)

(もっと読む)

積層配線基板とその製造方法

【課題】積層配線基板の配線層をキャパシタ下部電極として利用する場合に、密着強度を上げる微細凹凸の形成がキャパシタ特性や信頼性に不利益を与えないようにする。

【解決手段】積層基板構造内の配線層14の表面に、絶縁基板10に他の絶縁基板19aを貼り合わせるときの密着強度を確保する微細凹凸が形成されている。当該微細凹凸が形成された配線層14面上に導電層16が形成されている。当該導電層16を下部電極とし、下部電極上にキャパシタ誘電体膜17と上部電極18が積層された容量素子が形成されている。

(もっと読む)

多層配線基板

【課題】寄生インダクタンスの影響を抑え、設計の自由度を保ちつつキャパシタ−レジスタ回路を配置できる多層配線基板を提供する。

【解決手段】複数の絶縁性基板が積層された多層配線基板1は、複数の絶縁性基板の少なくとも1つを貫通する第1接続部21Aを有し、電源を供給する電源パターンと、複数の絶縁性基板の少なくとも1つを貫通する第2接続部22Aを有し、基準電圧を形成するグラウンドパターンと、高誘電率材料からなるキャパシタ部31と、高抵抗材料からなるレジスタ部32と、キャパシタ部とレジスタ部との間に形成される電極部33とを備え、電源パターンとグラウンドパターンとを電気的に直列に接続するように配置されるキャパシタ−レジスタ回路部30とを備え、キャパシタ−レジスタ回路部は、キャパシタ部、レジスタ部、及び電極部が複数の絶縁性基板の面方向に積層されて形成されていることを特徴とする。

(もっと読む)

実装基板及びその製造方法並びに電子機器

【課題】静電容量素子を内蔵する実装基板において実装基板の大きさを制限し小型化する。

【解決手段】樹脂基板(10,13,16)に貫通開口部(スルーホールTH)が形成されており、樹脂基板の貫通開口部の内壁を被覆するように下部電極20が形成されており、下部電極の上層に誘電体膜21が形成されており、誘電体膜の上層に上部電極23が形成されており、樹脂基板上に配線(31,32)が形成されている構成とする。

(もっと読む)

容量素子具有配線板、容量素子具有配線板の製造方法

【課題】薄板化することが可能な容量素子具有配線板を提供すること。

【解決手段】第1の方向に厚みを有し、該第1の方向に直交しかつ互いに直交する第2、第3の方向に広がりを有する絶縁層と、絶縁層を貫通して形成された、絶縁層の横断面における形状が線状である第1の電極と、第1の電極に対向するように絶縁層内に埋設された、絶縁層の比誘電率より大きな比誘電率を有する誘電体と、この誘電体の第1の電極に対向する側とは反対の側に対向して位置するように絶縁層を貫通して形成された、絶縁層の横断面における形状が線状である第2の電極と、第1の電極に電気的に導通するように絶縁層上に設けられた第1の金属箔パターンと、第2の電極に電気的に導通するように絶縁層上に設けられた第2の金属箔パターンとを具備する。

(もっと読む)

電子部品及びその製造方法

【課題】電子部品の外部基板への更なる高密度実装が可能であり、また、端子電極の高さを任意にかつ所望に調整でき、これにより、電子部品の検査時における従来の不都合を解消できるとともに、電子部品の実装における歩留まりを改善して生産性をも高めることが可能な電子部品及びその製造方法を提供する。

【解決手段】電子部品の1つであるコンデンサ1は、基板2上に形成される第1の上部電極5aと、その第1の上部電極5aに隣接して形成された第1の台座10及び第2の台座11と、第1の上部電極5a並びに第1の台座10及び第2の台座11を覆う保護層6,8と、それらを貫通するビア導体Va,Vcを介して第1の上部電極5aと接続され、かつ、第1の台座10及び第2の台座11上に形成された端子電極9aとを備える。

(もっと読む)

配線基板及び半導体装置

【課題】キャパシタを内蔵し、半導体素子を実装した際に前記半導体素子と前記キャパシタとの間のインダクタンスを低減することが可能な配線基板、及び前記配線基板に半導体素子を実装した半導体装置を提供する。

【解決手段】無機誘電体を含む絶縁性基材11と、前記絶縁性基材の一方の面から他方の面に貫通する複数の線状導体12と、を備えたコア基板13と、前記コア基板の両面に備えられたグランド配線群21b、23bと、前記コア基板の両面に備えられた電源配線群21c、23cと、を有し、前記グランド配線群と前記電源配線群とは、前記絶縁性基材を介して配置されている。

(もっと読む)

1 - 20 / 211

[ Back to top ]