Fターム[5F003BH99]の内容

バイポーラトランジスタ (11,930) | 電極、配線 (1,046) | 電極材料 (587) | 高融点金属 (93)

Fターム[5F003BH99]に分類される特許

21 - 40 / 93

半導体基板、電子デバイスおよび半導体基板の製造方法

【課題】エピタキシャル成長により形成された結晶膜の成長面内における物性値を均一な値に近づける。

【解決手段】第1化合物半導体および第2化合物半導体を積層した積層半導体を含み、前記第1化合物半導体の所定物性値が第1面内分布を有し、前記第2化合物半導体の前記所定物性値が前記第1面内分布とは異なる第2面内分布を有し、前記積層半導体における前記所定物性値の面内分布の幅が、前記第1面内分布の幅または前記第2面内分布の幅より小さい半導体基板を提供する。

(もっと読む)

バイポーラ半導体素子

【課題】高温や電流密度が高い条件下でも基板へ少数キャリアが到達するのを防いで、順方向電圧の増大を防ぐことができるバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20では、n型SiC基板21とn型バッファ層22との間に形成したn型少数キャリア消滅層31は、n型バッファ層22よりも炭素空孔欠陥の濃度が高く、少数キャリア消滅層31の炭素空孔欠陥はp型のアノード層24,25からの正孔のトラップとして働く。よって、小数キャリア消滅層31に達した正孔(少数キャリア)がトラップされ、小数キャリア消滅層31において正孔密度K2が急激に減衰する。これにより、正孔(少数キャリア)が基板21へ到達することを防いで、基板21から積層欠陥が拡大するのを防いで、順方向電圧の増大を防止できる。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製法

【課題】高い電流増幅率を有し、高周波特性および素子寿命に優れたヘテロ接合バイポーラトランジスタおよびその製法を提供すること。

【解決手段】半絶縁性基板1上に、n型半導体より成る真性エミッタ層16と、p型ドーパントを高濃度でドーピングされ、真性エミッタ層16よりも狭いバンドギャップを有する半導体より成るベース層9と、ベース層9と同じ半導体より成るコレクタ層10とを、この順序で積層して成るへテロ接合バイポーラトランジスタにおいて、真性エミッタ層16の周囲に、高抵抗領域15が設けられ、高抵抗領域15と真性エミッタ層16との間に、真性エミッタ層16の半導体と同じ半導体から成るガードリング領域17が設けられ、真性エミッタ層16とベース層9との接合面が、ガードリング領域17の上面よりも下に位置することを特徴とするヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

ヘテロ接合バイポーラ・トランジスタ及びその製造方法

【課題】 ヘテロ接合バイポーラ・トランジスタ及びその製造方法を提供する。

【解決手段】 ヘテロ接合バイポーラ・トランジスタに関連する、半導体構造体及び半導体の製造方法が提供される。この方法は、同じ配線レベルにある金属導線によって接続される2つのデバイスを形成することを含む。2つのデバイスの第1のものの金属導線は、銅配線構造体上に金属キャップ層を選択的に形成することによって形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

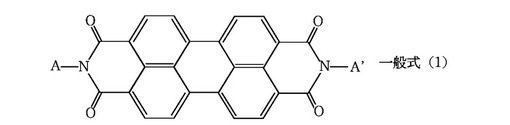

トランジスタ素子

【課題】エミッタ電極−コレクタ電極間において、オフ電流が小さく、かつ、低電圧で大電流変調が可能であるオン/オフ比に優れたトランジスタ素子を提供すること。

【解決手段】エミッタ電極とコレクタ電極との間に、有機半導体層とシート状のベース電極とが設けられているトランジスタ素子において、該有機半導体層が、下記一般式(1)で表される化合物を含んでいるトランジスタ素子。 (もっと読む)

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】エミッタ接地直流増幅率のばらつきを低減し、かつ抵抗の増大を防止できる、信頼性に優れるバイポーラトランジスタを得ること。

【解決手段】本発明は、N−型エピ層3aやP−型シリコン基板1aを含む半導体基板、N+型ポリシリコン層21a、タングステン層25、シリサイド層27a、シリサイド層39a、ベース電極36a、エミッタ電極36b及びコレクタ電極36cを少なくとも備える。半導体基板上に形成されたN+型ポリシリコン層21aはシリサイド層27aに覆われる。シリサイド層27a上の形成されたタングステン層25はシリサイド層39aに覆われる。

(もっと読む)

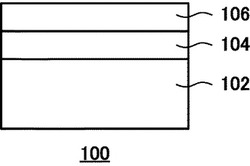

有機縦型トランジスタ

【課題】キャリア移動度が高く、低駆動電圧で大電流変調を可能とする有機縦型トランジスタを提供すること。

【解決手段】有機縦型トランジスタ1は、基板7と、エミッタ電極2と、第1有機半導体層3と、ベース電極4と、第2有機半導体層5と、コレクタ電極6とを備え、第1および第2有機半導体層3,5は、正孔輸送材料で形成され、各層を形成する有機半導体材料は、その分子構造に平面部分を有し、各分子の平面部分が基板7に対して略平行に配列し、その分子の形成するπ軌道が上下の分子のπ軌道と重なりを有し、分子が積層される配列方向に、エネルギー−波数(E−k)の関係を示す所定のバンド分散幅を有したエネルギーバンドを形成する。エミッタ電極2は、正孔を第1および第2有機半導体層3,5に注入する電極であり、エミッタ電極2およびコレクタ電極6は仕事関数が大きい材料、ベース電極4は仕事関数が小さい材料で形成されている。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法

【課題】アスペクト比の高いサブミクロンサイズのエミッタ電極パタンを線幅制御性良く形成することを可能とするヘテロ接合バイポーラトランジスタの製造方法を提供すること。

【解決手段】エミッタコンタクト層6上にTi層(図示せず)、エッチングストッパー用のW層7、Au層8、エッチングマスク用W層9、フォトレジストパタン10を形成し、フォトレジストパタン10をマスクとしてエッチングマスク用W層9を選択的に除去することによってWパタン9とし、Wパタン9をマスクとして、Au層8を、酸素ガスを含有する混合ガスを用いる反応性イオンエッチング法により選択的に除去し、Wパタン9をマスクとして、エッチングストッパー用のW層7、Ti層を選択的に除去することを特徴とするヘテロ接合バイポーラトランジスタの製造方法を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ高製造歩留まりで、BiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】シャロートレンチ3、ディープトレンチ6に囲まれた半導体層2の基板領域17に、p型の単結晶半導体からなるエピタキシャル・ベース層24が島状に形成される。当該島状領域を含む半導体層2上の全面に窒化シリコン膜42、酸化シリコン膜43が形成される。島状領域上の異なる位置の窒化シリコン膜42、酸化シリコン膜43には、少なくとも2つの開口部が形成され、開口部が形成された窒化シリコン膜42、酸化シリコン膜43上に半導体膜44が形成される。当該半導体膜44が選択的に除去され、一方の開口部において島状領域に接続するベース電極と、他方の開口部において島状領域に接続するエミッタ電極とが同時に形成される。

(もっと読む)

ヘテロ接合バイポーラトランジスタ及びその製造方法

【課題】耐破壊性に優れたヘテロ接合バイポーラトランジスタを提供する。

【解決手段】サブコレクタ層と、第1コレクタ層、第2コレクタ層、第3コレクタ層及び第4コレクタ層を有しサブコレクタ層上に形成されたコレクタ層と、コレクタ層上に形成されたベース層と、ベース層上に形成され、ベース層を構成する半導体よりも大きなバンドギャップを有する半導体から構成されるエミッタ層とを備え、第1コレクタ層は、第2コレクタ層、第3コレクタ層及び第4コレクタ層を構成する半導体と異なる半導体から構成されてサブコレクタ層上に形成され、第4コレクタ層は、第2コレクタ層の不純物濃度よりも低い不純物濃度で第1コレクタ層上に形成され、第2コレクタ層は、サブコレクタ層の不純物濃度よりも低く第3コレクタ層の不純物濃度よりも高い不純物濃度で第4コレクタ層上に形成され、第3コレクタ層は、第2コレクタ層とベース層との間に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッドの剥がれを防止し、かつボンディングパッド間におけるリーク電流の発生を防止することができる半導体装置及びその製造方法を提供すること。

【解決手段】HBT(ヘテロ構造バイポーラトランジスタ)が構成要素の1つとして集積された半導体装置110は、半絶縁性InP基板11上に、順次、エッチングストップ層12、コレクタコンタクト層13、コレクタ層14、傾斜コレクタ層15、セットバック層16、ベース層17が形成された構成を有し、ベース層17はInGaAsで構成された薄膜であってPを含まず、このベース層17上にSiN23が形成され、SiN23上にボンディングパッド25が形成された構成を有する。

(もっと読む)

シリコン基板上に形成されるCMOSデバイスおよびIII−V族デバイスのための電気コンタクト

半導体構造体は、基板(12)と、基板を覆うシード層(13)と、シード層上に配置されるシリコン層(22)と、シリコン層中のトランジスタデバイス(27)と、シード層上に配置されるIII−V族デバイスと、複数の電気コンタクトと、を備え、それぞれの電気コンタクトは、TiNまたはTaNの層(32)と、TaNまたはTiNの層上の銅またはアルミニウムの層(34)と、を備え、電気コンタクトの1つは、トランジスタ(27)に電気的に接続され、電気コンタクトの別の1つは、III−V族デバイスに電気的に接続される。 (もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

トランジスタ素子及びその製造方法並びに発光素子及びディスプレイ

【課題】エミッタ電極−コレクタ電極間において、低電圧で大電流変調を可能とするトランジスタ素子を提供する。また、そうしたトランジスタ素子の製造方法、また、そのトランジスタ素子有する発光素子及びディスプレイを提供する。

【解決手段】エミッタ電極3とコレクタ電極2との間に、半導体層5(5A,5B)とシート状のベース電極4が設けられているトランジスタ素子により、上記課題を解決する。半導体層5は、エミッタ電極3とベース電極4との間及びコレクタ電極2とベース電極4との間に設けられて、それぞれ第2半導体層5B及び第1半導体層5Aを構成し、さらに、ベース電極の厚さが80nm以下であることが好ましい。また、少なくともエミッタ電極とベース電極との間又はコレクタ電極とベース電極との間には、暗電流抑制層が設けられていてもよい。

(もっと読む)

n型ベースを有するバイポーラトランジスタ及びその製造方法

【解決手段】ベースコンタクト接続部(12)、エミッタ部(4、5)及びコレクタ部がn層(3)上に配置され、当該n層は、更なるnpnバイポーラトランジスタために用いることができる。当該コレクタ部はエミッタ部に対して側方に配置され、当該エミッタ部及びコレクタ部の少なくとも一方は、当該n層の表面領域上でショットキーコンタクト(14)を備える。 (もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】自己発熱および高電流密度動作下においても劣化を生じにくく、高電流密度まで安定して通電可能な高信頼電極を有し、より高い信頼度を達成可能なヘテロ接合バイポーラトランジスタを提供すること。

【解決手段】半導体基板1上に、サブコレクタ層2、コレクタ層3、ベース層4、エミッタ層5およびエミッタコンタクト層6が順次積層されたヘテロ接合バイポーラトランジスタにおいて、エミッタコンタクト層6とエミッタ電極7との間に、Moの融点以上の融点を有する単体金属または合金からなるバリア金属層13−2(図2に示す)を有するバリア複合層13が介在することを特徴とするヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

半導体装置

【課題】SiGe混晶層を有する半導体装置において、高い高周波特性と安定した低いベースコンタクト抵抗とを得られるようにする。

【解決手段】半導体装置は、N型のコレクタ層1aと、コレクタ層1aの上に形成され、P型SiGe層3bを含む真性ベース層となるSiGeエピ膜3と、SiGeエピ膜3の周囲に形成され、P型の多結晶シリコン層及びP型の多結晶シリコンゲルマニウム層を含むベース引き出し電極4と、SiGeエピ膜3の上部に形成されたN型のエミッタ層8とを有している。真性ベース層の上部には、Si−Cap層3cが形成されており、エミッタ層8は、Si−Cap層3cの上部に形成された上部エミッタ領域8bと、該上部エミッタ領域8bの下側に該上部エミッタ領域8bと接して形成された下部エミッタ領域8aとにより構成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高周波帯域で動作する半導体装置の特性向上と製造コストの低減とを両立した半導体装置およびその製造方法を提供する。

【解決手段】同一の半絶縁性GaAs基板1上に積層された複数の半導体層を用いて複数の半導体素子が形成された半導体装置100であって、FET領域23を用いて形成されたFETと、FET領域23と隣接するHBT領域22を用いて形成されたHBTと、FET領域23とHBT領域22との間である素子分離領域24に設けられ、FET領域23とHBT領域22とを分離する分離溝25とを備え、分離溝25は、内壁面と該内壁面の端部とに接地電位を有する導電性金属層が形成されることにより、素子分離領域24を通過する素子間リーク電流を抑制する。

(もっと読む)

グラフェントランジスタ及び電子機器

【課題】グラフェントランジスタ及び電子機器に関し、グラフェン膜を用いたチャネル層の特性を各場所で最適化することにより、グラフェントランジスタの性能を向上する。

【解決手段】一層以上のグラフェンからなる炭素膜12をキャリアが走行する能動領域とするとともに、前記能動領域を構成する前記炭素膜のキャリアの走行方向に垂直な方向の幅を場所によって変化させる。

(もっと読む)

21 - 40 / 93

[ Back to top ]