Fターム[5F004DB03]の内容

半導体のドライエッチング (64,834) | 被エッチング物 (6,778) | SiO2 (1,308)

Fターム[5F004DB03]の下位に属するFターム

Fターム[5F004DB03]に分類される特許

1,221 - 1,237 / 1,237

改良されたフォーカスリングに対する方法および装置。

【課題】 改良されたフォーカスリングに対する方法および装置を提供することである。

【解決手段】 プラズマ処理システム内で基板ホルダに組み合わせるように構成されたフォーカスリングアセンブリは、フォーカスリングの寿命を決定する1つ以上の消耗インジケータを有するフォーカスリングを具備し、そこにおいて、このフォーカスリングを基板ホルダに組み合わさせることは、プラズマ処理システムのフォーカスリングの自動−センタリングを容易にする。例えば、基板ホルダにマウントされたリングをセンタリングすることは、フォーカスリング上の嵌合形態で組み合わせるように構成されたセンタリング形態を有することができる。

(もっと読む)

基板処理方法

本発明は、有機シランガスを用いたプラズマCVD法により成膜される絶縁膜の低誘電率化と、機械的な強度の維持を可能とすることを目的としている。

そのため、本発明では、被処理基板に有機シランガスを含む第1の処理ガスを供給してプラズマを励起することで、当該被処理基板上に絶縁膜を成膜する成膜工程と、前記成膜工程の後、前記被処理基板にH2ガスを含む第2の処理ガスを供給してプラズマ励起することで、当該絶縁膜の処理を行う後処理工程と、を有する基板処理方法であって、前記後処理工程のプラズマ励起は、マイクロ波プラズマアンテナにより行われることを特徴とする基板処理方法を用いている。

(もっと読む)

電子デバイスの製造方法及び電子デバイス

基板上に基層及び機械層を設けることと、基層と機械層との間に犠牲層を設けることと、犠牲層と基板との間にエッチストップ層を設けることと、ドライ化学エッチングを用いて犠牲層を除去することとを含み、ドライ化学エッチングはフッ素含有プラズマを用いて行われ、エッチストップ層は、HfO2,ZrO2,Al2O3及びTiO2のような実質的に非導電性のフッ素の化学作用を起こさない材料を有するマイクロマシン技術(MEMS)デバイスの製造方法である。  (もっと読む)

(もっと読む)

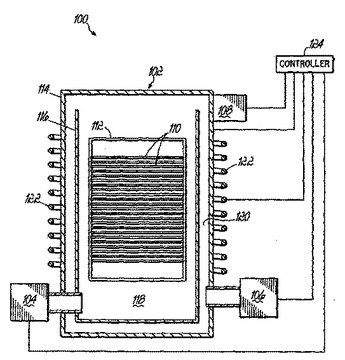

システムコンポーネントの状態をモニタリングするための方法およびそのための処理システム

処理中にコンポーネント(200,300)の状態をモニタリングする方法およびシステム。本方法は、処理中にコンポーネントを反応ガス(エロージョン生成物発生のためコンポーネント材をエッチングできる)に曝露することと、コンポーネントの状態を判定するため処理中にエロージョン生成物の放出をモニタリングすることを含む。モニターできる処理はチャンバークリーニング、同コンディショニング、基板エッチングおよび薄膜形成処理を含む。コンポーネントは、チューブ(25)、シールド、リング、バッフル、インジェクター、基板ホルダー(35,12)、ライナー、ペデスタル、キャップカバー、電極およびヒーター(15,20,65,70,122)等消耗部品でもよく、それらは保護コーティングを有していてもよい。処理システム(1,100)は、処理チャンバー(10,102)内のコンポーネント、ガス噴射システム(94,102)、チャンバー保護システム(92,108)およびコントローラ(90,124)を含む。  (もっと読む)

(もっと読む)

製造方法

【課題】 基板内に導電性構造体を形成する方法を提供すること。

【解決手段】 表面上に多段階層構造体を形成する方法が記載される。この方法は、表面上に硬化可能な液体層を堆積させるステップと、内部に多層パターンを有するスタンプを液体層に圧入し、該パターンによって定められる多段階層構造体を該液体層内に生成するステップと、液体層を硬化させ、内部に多段階層構造体を有する固体層を生成するステップとを含む。機械的位置合わせを用いて、構造体を形成することになる基板上に離間配置された複数の突出部及びスタンプのパターン内の相補的陥凹部を介して、基板に対するスタンプの光学的位置合わせを強化することができる。

(もっと読む)

ランピングによるエッチング

【課題】基板上のマスクを通してエッチングレイヤ中にフィーチャをエッチングする方法を提供する。

【解決手段】基板がプロセスチャンバ内に置かれる。プロセスチャンバにエッチングプラズマが供給され、エッチングプラズマがエッチングを始める。エッチングプラズマでエッチングレイヤ中にフィーチャがエッチングされる。フィーチャのエッチングのあいだに少なくとも1つのエッチングプラズマパラメータがランピングされることによって、プラズマパラメータを変化するエッチング深さに最適化し、フィーチャがフィーチャ深さまでエッチングされるまでランピングされたプラズマでエッチングされる。

(もっと読む)

フィーチャ微小寸法の低減

【課題】レイヤ中にフィーチャを形成する方法を提供する。

【解決手段】レイヤ上にフォトレジストレイヤが形成される。フォトレジストレイヤがパターン付けされることによって、フォトレジスト側壁を持つフォトレジストフィーチャが形成され、フォトレジストフィーチャは第1微小寸法を有する。フォトレジストフィーチャの側壁上にコンフォーマルレイヤが堆積されることによって、フォトレジストフィーチャの前記微小寸法が低減される。レイヤ内でフィーチャがエッチングされ、レイヤフィーチャは、第1微小寸法より小さい第2微小寸法を有する。

(もっと読む)

さまざまな周波数のRF電力の変調を用いた高アスペクト比エッチング

【課題】マスクを通して基板上のエッチングされるべきレイヤ内へ高アスペクト比フィーチャをエッチングする方法を提供する。

【解決手段】RF電力を第1周波数、前記第1周波数とは異なる第2周波数、および前記第1および第2周波数とは異なる第3周波数において与えることができる処理チャンバ内に基板が置かれる(404)。エッチャントガスが処理チャンバに供給される(408)。第1エッチングステップが行われ(412)、ここで第1周波数、第2周波数、および第3周波数は第1エッチングステップとしての電力設定である。第2エッチングステップが行われ(416)、ここで第1周波数、第2周波数、および第3周波数は異なる電力設定である。オプションとして第3エッチングステップも提供されえる(420)。

(もっと読む)

溝配線を有する半導体装置および半導体装置の製造方法

【課題】 多層配線において、ショートやビア抵抗増加のような目合わせずれによる問題を回避し、信頼性の高い多層配線を得る。

【解決手段】 半導体装置は、第1配線層(201)と、層間絶縁層(202〜208)とを具備する。第1配線層(201)は、基板の上面側に設けられ、第1配線を含む。層間絶縁層(202〜208)は、前記第1配線層(201)上に設けられ、一方の端を前記第1配線に接続されたビアと、前記ビアの他方の端に接続された第2配線とを含む。前記層間絶縁層(202〜208)はシリコン酸化膜より低い比誘電率を有する。前記層間絶縁層(202〜208)の上部は、下側から順に、シリコン酸化膜(206)、シリコン窒化膜(207)、シリコン酸化膜(208)を備える。

(もっと読む)

多層配線構造の形成方法

【課題】SOG膜のSi原子と有機基(例えばCH3基)やH基の結合がアッシング時に切れるのを抑制して誘電率を低く抑える。

【解決手段】低誘電率の有機又は無機SOG膜にパターン化レジスト膜をマスクとしてエッチングを行って配線溝を形成し、この後、枚葉式ダウンストリーム型のプラズマアッシング装置を用いて、酸素ガスプラズマによるアッシング処理を例えば1.2Torrの圧力雰囲気下で施してレジスト膜を除去し、この後配線溝にバリヤメタル形成後、Cuを電界メッキ法にて埋設して配線を形成する。

(もっと読む)

積層絶縁膜の加工方法及び配線構造の形成方法

【課題】 積層絶縁膜を良好に加工する方法、並びにその方法を用いた配線構造の形成方法を提供すること。

【解決手段】 互いに異なる複数の絶縁膜4、5(更には3)のそれぞれについて少なくとも反応ガスの種類及び/又はその供給量に対するエッチング速度の関係を求めておき、この関係に基づいて反応ガスの供給量を設定してエッチング速度を選択し、エッチングを行う。各絶縁膜のエッチング速度をそれぞれ適切に選択するので、複数の絶縁膜が積層していても、常に良好な加工形状を得ることができる。膜種ごとに異なるエッチング速度の反応ガスの供給量に対する依存性を、複数の絶縁膜の相互間で差別化し、積層絶縁膜のエッチング選択比を目的にあわせて適切に設定する。

(もっと読む)

プラズマプロセス用装置

【技術課題】 基板に損傷や表面汚染を与えることなく、エッチングや成膜が行え、チャンバや電極等の構造は同一であるにも拘らず、導入するガスやプラズマ励起周波数を変えることにより、エッチングや成膜にも応用可能であり、生産性に優れるとともに、低価格で高性能なプラズマプロセス用装置を提供すること。

【解決手段】 容器内105に対向するように設けられ夫々平板状に形成された第1及び第2電極102,104と、プラズマに対して安定な材料から成り第1電極102上を覆うように設けられる保護部材101と、第2電極104上に被処理物103を取り付けるための保持手段と、第1電極102に接続される第1の高周波電源111と、第2電極104に接続される第2の高周波電源110と、容器105内に所望のガスを導入するためのガス供給手段とを少くとも備え、第1の高周波電源の周波数が前記第2の高周波電源の周波数より高いことを特徴とする。

(もっと読む)

SAWチップ及びこれを利用したSAWデバイスの製造方法

【課題】 SAWチップをベースに組み込む工程においても異常な周波数変動を生じることなく、信頼性の高いSAWチップとこれを利用したSAWデバイスの製造方法を提供すること。

【解決手段】 圧電基板111にドライエッチングにより電極パターンを形成するSAWチップ110の製造方法であって、圧電基板上にアルミニウムまたはアルミニウム合金により電極膜23を形成する電極膜形成工程ST1と、前記電極膜を所定の電極パターンとなるように、圧電基板表面が露出するまでドライエッチングを行うドライエッチング工程ST2と、前記露出された圧電基板表面の残留アルミニウムを除去するための洗浄工程ST3とを含んでいる。

(もっと読む)

マイクロ波供給器及びプラズマ処理装置並びに処理方法

【課題】 マイクロ波の放射特性をより精密に制御することにより、被処理体の半径方向及び周方向における処理の制御性を高める。

【解決手段】 マイクロ波を放射する為の複数のスロット33が設けられた面23を有する環状導波路13を有するマイクロ波供給器及びそれを用いたプラズマ処理装置において、環状導波路13の中心C1に対してスロット3の中心C2、C5が前記面に沿った方向に偏って配置されていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 欠陥のないエピタキシャル膜を形成する

【解決手段】 異物除去処理を有し、ドライエッチング処理を行って形成した開口部5内の単結晶シリコン基板1に、SiGeエピタキシャルベース7を成長させる半導体装置の製造方法である。異物除去処理は、前記ドライエッチング処理後からSiGeエピタキシャルベース7の成長までの間に、被成長基板を酸素雰囲気中において、熱処理を行い、ドライエッチング処理によって、シリコン酸化膜2に堆積した炭素系付着物10を、シリコン酸化膜2から完全に除去し、これによって、欠陥のないエピタキシャル膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 シリル化プロセスを用いて微細なパターンの形成を可能とし、しかもシリル化部表面に形成されるSiOx 層の除去を支障なく行うことのできる、半導体装置の製造方法が提供が望まれている。

【解決手段】 下地基板20上の被パターニング層23上にレジスト層24を形成し、次にレジスト層24の所定箇所を露光し、次いでこの露光工程後のレジスト層24における未露光部分をシリル化する。続いて、露光した箇所のレジスト層24をドライ現像によって除去し、シリル化された部分に対応した積層パターン30を得る。次いで、積層パターン30からその表層部に形成されたSiOx層29を除去してレジストパターン32を形成する。その後、レジストパターン32をマスクにして被パターニング層23をエッチングする。

(もっと読む)

多層配線構造の形成方法

【課題】 SOG膜のSi原子と有機基(例えばCH3基)やH基の結合がアッシング時に切れるのを抑制して誘電率を低く抑える。

【解決手段】 低誘電率の有機又は無機SOG膜にパターン化レジスト膜をマスクとしてエッチングを行って配線溝を形成し、この後、枚葉式ダウンストリーム型のプラズマアッシング装置を用いて、酸素ガスプラズマによるアッシング処理を例えば1.2Torrの圧力雰囲気下で施してレジスト膜を除去し、この後配線溝にバリヤメタル形成後、Cuを電界メッキ法にて埋設して配線を形成する。

(もっと読む)

1,221 - 1,237 / 1,237

[ Back to top ]