Fターム[5F004EA03]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | マスク構成 (1,627) | レジスト以外のエッチングマスク (1,380)

Fターム[5F004EA03]の下位に属するFターム

Fターム[5F004EA03]に分類される特許

421 - 430 / 430

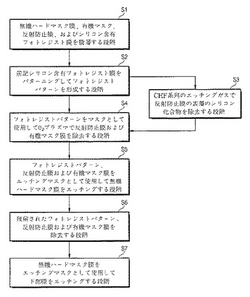

半導体パターン形成方法

【課題】 半導体パターン形成方法を提供する。

【解決手段】 この方法は無機ハードマスク膜、有機マスク膜、反射防止膜及びシリコン含有フォトレジスト膜が積層された多層のマスク層を形成し、O2プラズマで前記反射防止膜及び有機マスク膜を乾式エッチングしてパターンを形成することによって無機ハードマスク膜の損傷を防止することができる。

(もっと読む)

微細構造の作製方法及び作製装置

【課題】 電子線によるガスデポジション法で作製したものと同サイズ(ナノメートルオーダー)の微細構造を、位置とサイズを自由に制御しつつ、任意の材料、結晶性にて作製することができる新規な作製方法及び作製装置を提供する。

【解決手段】 マスクの原料となる元素を含んだガスを材料上に流しながら、電子線を材料上の所望位置に向かって照射してマスクを形成した後、エネルギービームを照射してマスクで被覆された部分以外の材料部分を取り除くことにより、材料に微細加工を行う。

(もっと読む)

改善された二重ダマシン集積構造およびその製造方法

ガスクラスターイオンビーム処理を用いた多孔質超低k値(ULK)絶縁体材料内に二重ダマシン構造を形成する方法に関して開示する。これらの方法においては二重ダマシンULK処理中におけるハードマスク層を最小にし、最終的なULK二重ダマシン構造内には、ハードマスク層が存在しない。ガスクラスターイオンビームのエッチング処理、緻密化処理、孔のシーリング処理、アッシング処理の各方法が記載されており、該方法は、材料の除去と同時にULKインターフェースの緻密化を進行させる。緻密なインターフェースとハードマスクがない新規なULK二重ダマシン構造が含まれている。 (もっと読む)

エッチング特性を改良するためのハードマスクを処理する方法およびシステム。

【課題】 エッチング特性を改良するためにハードマスクを処理する方法およびシステムを提供することである。

【解決手段】 パターンを膜スタックに転写する間、ハードマスク層、例えば調整可能なエッチング耐性反射防止コーティング(TERA)は、下地層をエッチングするときに消費され、エッチング性能を低下させ、下地層のダメージの可能性、例えば形態制御性の喪失に繋がる。基板上の構造を準備する方法およびシステムは、薄膜を含む膜スタックを準備することと、薄膜上に形成されたハードマスクと、ハードマスク上に形成された感光材料の層とを有する膜スタックを準備することと;感光材料の層にパターンを形成することと;ハードマスクにパターンを転写することと;感光材料の層を取り除くことと;表面を改質するためにハードマスクの表面層を処理することと;薄膜にパターンを転写することとを含む事が記載される。

(もっと読む)

プラズマ加工システムによる基板エッチング法

プラズマ加工システムで基板をエッチングする方法を提供する。基板は、半導体層、その半導体層上方に提供された第1バリアー層、その第1バリアー層上方に提供された低k層、その低k層上方に提供された第3ハードマスク層、その第3ハードマスク層上方に提供された第2ハードマスク層、及びその第2ハードマスク層上方に提供された第1ハードマスク層を有する。方法には、第1ハードマスク層の第1ハードマスク材料、第3ハードマスク層の第3ハードマスク材料、及び第1バリアー層の第1バリアー層材料に対して低選択度を有するが、第2ハードマスク層の第2ハードマスク材料に対しては高選択度を有する第1エチャントと、第1ハードマスク層の第1ハードマスク材料、第3ハードマスク層の第3ハードマスク材料、及び第1バリアー層の第1バリアー層材料に対しては高選択度を有する第2エチャントとで基板を交互にエッチングするステップが含まれ、第1エチャントは第2ハードマスク層の第2ハードマスク材料に対して低選択度を有する。  (もっと読む)

(もっと読む)

調整可能な反射防止コーティングを含む構造およびその形成方法。

【課題】 調整可能な反射防止コーティングを含む構造およびその形成方法を提供することである。

【解決手段】 調整可能なエッチング耐性反射防止(TERA)コーティングを含む配線工程(BEOL)アプリケーションにおける配線構造が記載される。TERAコーティングは、例えば、シングルダマシン構造またはデュアルダマシン構造の中で取り入れられることができる。TERAコーティングは、配線構造を形成するリソグラフィマスクの一部として役に立つことができ、または、それは、ハードマスクとして、ケミカルメカニカルポリシング(CMP)のストップ層として、またはCMP中の犠牲層として役立つことになる。

(もっと読む)

集積回路用途の被覆およびハードマスク組成物、これらの製造方法および使用

少なくとも1種の無機化合物、および少なくとも1種の緻密化剤を含有し、前記緻密化剤は、少なくとも1種の無機化合物の密度と比較して、被覆材料の密度を増大させる被覆材料が、ここに記載されている。少なくとも1種の無機化合物を準備するステップと、少なくとも1種の緻密化剤を準備するステップと、少なくとも1種の無機化合物を少なくとも1種の緻密化剤と一緒にして被覆材料を形成するステップとを含み、前記緻密化剤は、少なくとも1種の無機化合物の密度と比較して、被覆材料の密度を増大させる被覆材料を製造する方法が、ここに記載されている。 (もっと読む)

半導体デバイスにおける造形部分のパターン形成技術

【課題】 パターン形成される造形部分の微小寸法を縮小する技術を提供すること。

【解決手段】 半導体の処理のための技術が提供される。1つの態様において、半導体デバイスに1つまたはそれ以上の造形部分をパターン形成するための方法は、以下のステップを含む。反射防止材のエッチング中に、1つまたはそれ以上の造形部分の少なくとも1つの微小寸法が縮小される。リソグラフィ構造もまた提供される。

(もっと読む)

半導体装置における透明無定形炭素構造

透明無定形炭素層が形成される。この透明無定形炭素層は吸収係数が小さく、そのためこの無定形炭素は、可視光範囲において透明である。透明無定形炭素層は、異なる目的のための半導体装置においても使用することができる。透明無定形炭素層は、半導体装置の最終構造に含まれてもよい。また、透明無定形炭素層は、半導体装置の製造中に、エッチング処理のマスクとして使用することもできる。  (もっと読む)

(もっと読む)

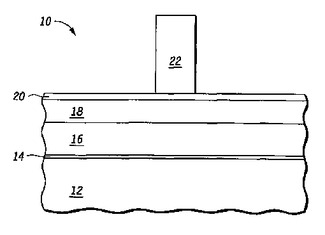

有機反射防止膜(ARC)を有する半導体装置及びその方法

半導体装置(10)の製造において、エッチングされる導電性材料(16)上のパターニング積層部は、下層にあるオルトケイ酸テトラエチル(TEOS)層(20)のパターニングに用いられるパターニングフォトレジスト層(22)を有している。TEOS層(20)は、従来より低い温度で成膜される。低温TEOS層(20)は、有機反射防止膜(ARC)(18)上に設けられ、有機反射防止膜は、導電層(16)上に設けられる。低温TEOS層(20)は、有機ARC(18)とフォトレジスト(22)との間の接着を提供し、低い欠陥性を有し、ハードマスクとして機能し、有機ARC(18)と共に望ましくない反射を低減させる位相シフト層として機能する。  (もっと読む)

(もっと読む)

421 - 430 / 430

[ Back to top ]