Fターム[5F004EA08]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | マスク構成 (1,627) | 矩形外マスク (28)

Fターム[5F004EA08]に分類される特許

1 - 20 / 28

搬送装置及び基板処理システム

コンタクトホールの形成方法および電気光学装置の製造方法

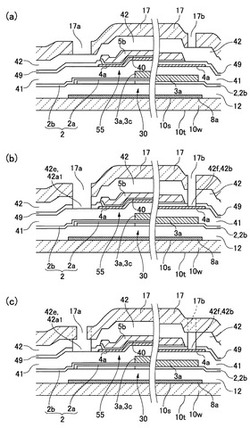

【課題】シュリンク技術を利用して、コンタクトホールとして利用できる複数の凹部を1回のレジストマスク工程で異なる深さ寸法に形成することのできるコンタクトホールの形成方法、および電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置の素子基板10上にコンタクトホールを形成するにあたって、まず、第1開口部17aおよび第2開口部17bを備えたレジストマスク17を層間絶縁膜42の表面に形成した後、第1開口部17aおよび第2開口部17bから層間絶縁膜42および絶縁膜49をエッチングする。その後、シュリンク工程において、レジストマスク17を変形させて第2開口部17bを塞ぐ一方、第1開口部17aの開口面積を狭める。次に、第1開口部17aから層間絶縁膜41およびゲート絶縁層2をエッチングする。

(もっと読む)

発光ダイオード用基板の製造方法、発光ダイオードの製造方法及びモールドの製造方法

【課題】高品質で低コストの発光ダイオード用基板の製造方法、発光ダイオードの製造方法及びモールドの製造方法を提供する。

【解決手段】実施形態に係る発光ダイオード用基板は、基板上に、レジスト材料を配置する工程と、主面に複数の第1の凸部が形成され、少なくとも前記第1の凸部の上面に、その幅及び間隔が前記第1の凸部の幅及び間隔よりも小さい複数の第2の凸部が形成されたモールドを、前記基板に押し付けることにより、前記第1の凸部間及び前記第2の凸部間に前記レジスト材料を進入させる工程と、前記モールドを押し付けた状態で、前記レジスト材料を固化させることにより、前記基板上にレジストパターンを形成する工程と、前記レジストパターンから前記モールドを剥離する工程と、前記レジストパターンをマスクとして、前記基板に対してエッチングを施す工程と、を備える。

(もっと読む)

半導体素子の作製方法

【課題】半導体からのV族原子の脱離を抑制しつつ同一面内でエッチング深さが異なる形状を簡易に加工することができる半導体素子の作製方法を提供する。

【解決手段】酸素プラズマの所定の濃度に対して、開口部幅の異なる領域毎に、半導体表面にて酸素プラズマによりポリマーの生成を抑制しつつ半導体表面のエッチングが進行する状態のみが発現するように前記開口部幅1905が設定された開口部1901を有するマスク1900を半導体表面に形成する第1の工程と、マスク1900が形成された前記半導体表面に前記炭化水素系プラズマおよび前記酸素プラズマを照射し、前記酸素プラズマを前記マスクの開口部幅方向にて前記開口部に拡散させることによりポリマーの生成を抑制するとともにエッチングに寄与する炭化水素系プラズマの濃度を制御する第2の工程を有するようにした。

(もっと読む)

半導体素子の作製方法

【課題】エッチング面積を変えずにマスク面積を小さくする、同一面内でエッチング深さが異なる形状を容易に加工することができる半導体素子の作製方法を提供すること。

【解決手段】エッチングされる領域のマスク端からの距離は、マスク幅が1μm以上でほぼ一定の値を示す。このことは、マスク上のマスク端から1μmまでの領域に存在する水素プラズマが開口部に拡散してエッチングに寄与することを示す。このとき、マスク上のマスク端から1μm以上の領域に存在する水素プラズマはエッチングに寄与することなくマスク上から脱離するものと考えられる。そのため、本発明の選択エッチングにおいてはマスクの幅は1μm以上あればエッチング領域のマスク端からの距離を十分に得られる。また、半導体素子の高密度集積における素子間隔が10μm程度であることを考慮すると、マスク幅は1μm以上10μm以下で有効である。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】単結晶半導体層のテーパー形状を有する端部の特性を良好にすることを課題とする。

【解決手段】加速されたイオンを単結晶半導体基板に照射することによって、単結晶半導体基板中に脆化領域を形成し、単結晶半導体基板とベース基板とを、絶縁膜を介して貼り合わせ、脆化領域において単結晶半導体基板を分離して、ベース基板上に絶縁膜を介して第1の単結晶半導体層を形成し、第1の単結晶半導体層に対してドライエッチングを行って、端部の形状がテーパー形状である第2の単結晶半導体層を形成し、第2の単結晶半導体層の端部に対して、ベース基板側の電位を接地電位としたエッチングを行う。

(もっと読む)

微細凹凸表面を有したエピタキシャル基板とその製造方法

【課題】エピタキシャル基板と製造方法を提供する。

【解決手段】本発明のエピタキシャル基板は結晶性基板を備える。結晶性基板は微細な凹凸を備えるとともにパターニング不要のエピタキシャル表面を有する。本発明によるエピタキシャル基板は化合物半導体材料から、良好な品質のエピタキシャル層の成長を得るという利点を有する。さらに、本発明によるエピタキシャル基板の製造方法は低コストかつ製造時間短縮といった利点を有する。

(もっと読む)

半導体装置

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

窒化物電子デバイス、窒化物電子デバイスを作製する方法

【課題】チャネル層のキャリア濃度が増大することを避けてリークを低減できる構造を有する、窒化物電子デバイスを提供する。

【解決手段】半導体積層15の斜面15a及び主面15cは、それぞれ、第1及び第2の基準面R1、R2に対して延在する。半導体積層15の主面15cは六方晶系III族窒化物のc軸方向を示す基準軸Cxに対して5度以上40度以下の範囲内の角度で傾斜すると共に、第1の基準面R1の法線と基準軸Cxとの成す角度は第2の基準面R2の法線と基準軸Cxとの成す角度より小さいので、チャネル層19の酸素濃度を1×1017cm−3未満にすることができる。これ故に、チャネル層19において、酸素添加によりキャリア濃度が増加することを避けることができ、チャネル層を介したトランジスタのリーク電流を低減できる。

(もっと読む)

ナノ/微小球リソグラフィによって製造されるナノ/マイクロワイヤ太陽電池

【課題】 ナノ/微小球リソグラフィによって製造されるナノ/マイクロワイヤ太陽電池を提供する。

【解決手段】 ナノワイヤ/マイクロワイヤ・ベースの太陽電池を製造する技術が提供される。一実施形態において、太陽電池を製造する方法が提供される。本方法は、以下のステップを含む。ドープ基板を準備する。基板の上に球の単層を堆積させる。球は、ナノ球、微小球、又はそれらの組み合わせを含む。球をトリミングして単層内の個々の球の間に空間を設ける。トリミングされた球をマスクとして用いて、基板内にワイヤをパターン形成する。ワイヤは、ナノワイヤ、マイクロワイヤ、又はそれらの組み合わせを含む。ドープ・エミッタ層をパターン形成されたワイヤ上に形成する。上部コンタクト電極をエミッタ層の上に堆積させる。底部コンタクト電極を基板のワイヤとは反対の側に堆積させる。

(もっと読む)

半導体装置の製造方法ならびに半導体装置

【課題】400℃程度の耐熱性を有するNd添加量2at%のAlNd層をプラズマエッチングにおいてフェンスと呼ばれる反応生成物の堆積を抑制できるエッチング方法を提供する。

【解決手段】プラズマエッチングを行うエッチングガスとして塩素ガスを用い、エッチング速度を250nm/分以下のエッチング速度でエッチングが行われるよう塩素ガスを供給する。ネオジム塩化物は蒸気圧がアルミニウム塩化物に比べて低いが、250nm/分以下のエッチング速度となるようプラズマエッチングすることで、アルミニウム塩化物と同時に蒸発させることができるため、フェンスの発生を抑えることが可能となる。

(もっと読む)

半導体発光素子

【課題】 光の取り出し効率を向上させることが可能な半導体発光素子を提供する。

【解決手段】 本発明による半導体発光素子1は、光(L9〜L11)を透過可能な基板2と、基板2の主面上に形成された、傾斜した側面10bを有する発光層を含む半導体層10と、半導体層10の表面を覆うように形成された反射層20とを備え、半導体層10の側面10bは、基板2の主面の水平方向に対して45〜75°の傾斜角θを有しており、反射層20は、複数の誘電体層(11〜13)を含み、各誘電体層(11〜13)は半導体層10の上部端面10a側の平均厚さがm(λ/nr)、半導体層10の側面10b側の平均厚さがm(λ/nr)cosθ、ただし、λ:発光層の発光波長、nr:各誘電体層(11〜13)の屈折率、m:1以上の任意の整数、で表される。

(もっと読む)

半導体装置の製造方法

【課題】より微細な配線が形成された半導体装置を容易に製造する方法を提供する。

【解決手段】半導体基板上に導電性膜を形成する工程と、前記導電性膜上に犠牲膜を形成する工程と、前記犠牲膜をパターニングする工程と、パターニングされた前記犠牲膜の側面に、サイドウォールを形成する工程と、パターニングされた前記犠牲膜を除去する工程と、前記サイドウォールをマスクとして用いて前記導電性膜をパターニングして、配線を形成する工程とを有する方法により、半導体装置を製造する。

(もっと読む)

プラズマエッチング方法及びフォトニック結晶製造方法

【課題】大面積に亘って大きなエッチング角で斜方向プラズマエッチングを行う方法を提供する。

【解決手段】基材21の表面に、それに対して傾斜した形状の縁23を持つ電界制御板22を前記表面に対して平行に載置し、プラズマ中のイオンにバイアス電圧を印加することによりイオンを基材21の表面に入射させる。電界制御板22の縁23がオーバーハングしているため、一見すると縁23の直下の領域26にはイオンが到達しないようにも思われるが、実際には縁23に沿って電界制御板22の下面側に等電位面が引き込まれるように変形することにより、領域26にイオンが回り込んで入射する。これにより、大面積に亘って、基材21の表面の法線に対して40°〜50°という大きなエッチング角で斜方向エッチングを行うことができ、それにより3次元フォトニック結晶を好適に作製することができる。

(もっと読む)

半導体装置のパターン形成方法

【課題】リソグラフィによらないでウィグル形状パターンを形成する半導体装置のパターン形成方法を提供することである。

【解決手段】本発明の1態様による半導体装置のパターン形成方法は、半導体基板の上方に被加工膜を堆積する工程と、前記被加工膜上に不純物を添加することによりエッチング特性が変化するマスク膜を堆積する工程と、前記マスク膜にラインパターンを形成する工程と、前記ラインパターンを形成したマスク膜の所望の領域にエッチング速度を変化させる不純物を選択的に添加する工程と、前記マスク膜からなる前記ラインパターンを選択的にエッチングして部分的に線幅の異なるウィグル形状を含むマスクパターンを形成する工程と、前記マスクパターンをマスクとして前記被加工膜をエッチングしてウィグル形状パターンを形成する工程とを具備する。

(もっと読む)

薄膜パターンの形成方法、磁気抵抗効果素子の製造方法および薄膜磁気ヘッドの製造方法

【課題】露光装置の解像限界に依存せずに、微小なパターン幅を有する薄膜パターンを高精度に形成することが可能な薄膜パターンの形成方法を提供する。

【解決手段】アンダーカット部を有するマスクパターンを使用して薄膜を選択的にエッチングすることによりプレ薄膜パターン(上面2A,側面2B)を形成し、引き続きプレ薄膜パターンの上面2Aおよび側面2Bを覆うようにエッチング保護膜を形成したのち、そのエッチング保護膜をマスクとしてプレ薄膜パターンを選択的にエッチングすることにより薄膜パターン7(側面2C)を形成する。2段階のエッチング工程を経て形成される2つの側面2B,2Cに基づいて薄膜パターン7のパターン幅が決定される。しかも、上面2Aの幅および側面2B,2Cの傾斜角度に基づいて薄膜パターン7のパターン幅が高精度に制御される。

(もっと読む)

アライメントマーク付き半導体基板及びアライメントマークの製造方法

【課題】 半導体基板の加工時における位置決めの際に、透明な基板に対しても良好な位

置情報の検出を実現することのできるアライメントマークを設けたアライメントマーク付

き半導体基板及びアライメントマークの製造方法を得る。

【解決手段】 彫りこみ形のアライメントマーク4及び5を構成するそれぞれの彫りこみ

6を、第一段目の彫りこみの底面61にさらに第二段目の彫りこみ62を設けた、二段の

階段状に形成し、アライメント光源等を照射したときに散乱による反射を起こしやすくし

て、透明な半導体基板に対しても十分な安定した反射光を得る。

(もっと読む)

半導体発光素子の製造方法

【課題】良好かつ安定したオーミック特性および接触抵抗を得ることができ、かつレジストマスク除去時における電極の酸化を防止した半導体発光素子の製造方法を提供する。

【解決手段】本実施形態に係る半導体発光素子の製造方法では、n型半導体層3と、発光層4と、p型半導体層5の積層構造からなるIII−V族窒化物系半導体層10を相対的に遅い第1速度でドライエッチングした後に、最終的に第1速度よりも速い第2速度でIII−V族窒化物系半導体層10をエッチングする。

(もっと読む)

被処理層の処理方法

【課題】 工程数の増加を可及的に抑制し、サイドエッチの進行を防止して、複数の被処理層を所望の形状に形成することができる被処理層の処理方法を提供する。

【解決手段】 第1エッチング処理工程の後に、被覆処理工程を行うことによって、サイドエッチによって形成される被処理層A3の側面をレジスト層1によって被覆することができる。これによって、第2エッチング処理工程において、被処理層A3が前記側面からエッチングされることを防止することができる。第1エッチング処理工程と第2エッチング処理工程との間に、被覆処理工程を設けることによって、エッチング処理工程を複数回行わなくても、サイドエッチを防止することができ、少ない工数で、複数の被処理層を所望の形状に形成することができる。

(もっと読む)

フェロキャパシタの組立プロセス

フェロキャパシタの形成のための方法であり、基板、底部の電極層1、フェロ電気層3およびトップの電極5を含む構造に対して第1のハードマスク要素7を堆積することを備える。RIEエッチングは、トップの電極5およびフェロ電気層3の部分を除去するために実行される。次に、第2のハードマスク要素9は、第1のハードマスク要素上に堆積される。第2のハードマスク要素は、エッチバックプロセスにより丸くされ、そのテーパー角は、75から87°の範囲に制御される。第2のRIEエッチングプロセスは、底部の電極1の部分を除去するために実行される。第2のハードマスク要素9の丸みにより、エッチングされた底部の電極1の側部に低い残存が形成される。  (もっと読む)

(もっと読む)

1 - 20 / 28

[ Back to top ]