Fターム[5F004EA09]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | アンダーエッチング、サイドエッチング (32)

Fターム[5F004EA09]に分類される特許

1 - 20 / 32

表面にリセスを形成する方法

【課題】基板の表面に微細形状のリセスを形成する。

【解決手段】表面上に、第1の寸法と形状を備えた第1のフューチャを有するパターン形成層を形成し、該パターン形成層をエッチングして、前記第1の寸法とは異なる第2の寸法を有する第2のフューチャを形成し、該第2のフューチャを順応層で覆うとともに、該順応層の上方を除去して前記第2のフューチャの頂部を露出させた後に、

該第2のフューチャを、前記順応層と相互作用してin-situ硬化マスクを生成する酸素ベースの化学作用を伴うプラズマエッチングにより除去して、前記第1の寸法とは異なる第2の寸法を有する、前記形状の反転形状を作成して、該反転形状を前記表面に転写する。

(もっと読む)

半導体装置の製造方法

【目的】マスクの厚さを所定の値にし、後退量とエッチング量の比を所定の値にしてトレンチの開口部の端部を丸めることで、ゲート酸化膜形成温度を950℃未満の低い処理温度にした場合でもゲート酸化膜の良好な耐圧特性と長期信頼性が得られる半導体装置の製造方法を提供すること。

【解決手段】マスクであるシリコン酸化膜2の端部10をトレンチ8の開口部9の端部Aから後退させる量Xと、等方性ドライエッチングによるエッチング量Yとの比(X/Y)を2以上5以下に設定することで、Qbdの値を高くすることができて、良好なトレンチ8の開口部9の端部Aと段差12の端部Bの形状を丸めることができる。その結果、その後形成するゲート酸化膜14の熱処理温度を、950℃未満、あるいは、900℃以下で行った場合でも、ゲート酸化14の良好な耐圧特性と長期信頼性を得ることが可能となる。

(もっと読む)

パターン形成方法

【課題】

本発明は、ナノインプリントリソグラフィにおいて、微細なパターンを形成可能なパターン形成方法を提供する。

【解決手段】

本発明の一態様であるパターン形成方法は、(a)被エッチング層10上方に多孔質層11を形成する工程と、(b)前記多孔質層11上に被転写パターンを有する有機材13を形成する工程と、(c)前記被転写パターンを用いて、前記多孔質11よりエッチング耐性が高い転写酸化膜16に加工パターンを形成する工程と、(d)前記転写酸化膜16をマスクとして、前記被エッチング層10に前記加工パターンを形成する工程とを備えることを特徴とする。

(もっと読む)

シリコンエッチング方法及び装置並びにエッチングシリコン体

【課題】所望のテーパ角度を容易に達成すると共に、テーパ表面の平滑化を実現でき、またオーバーハング形状が生じないシリコンエッチング方法及び装置並びにそれによって作製したエッチングシリコン体を提供する。

【解決手段】反応器1内を減圧し、ガス導入管4からプロセスガス(SF6 ,C4 F8 及びO2 の混合ガス)をプラズマ発生室2a内に導入する。コイル3に交流電圧を印加してプラズマ発生室2a内にてプロセスガスのプラズマを発生させ、同時に基板電極11に交流電圧を印加して、発生させたプラズマを反応室2b内に引き込み、引き込んだプラズマにより、プラテン6に載置した試料20(エッチングマスクが形成されたシリコン材)をテーパ状にエッチングする。エッチング後のシリコン材のエッチングマスクに接する面積が、エッチングマスクより狭い。

(もっと読む)

ミストエッチング装置及びミストエッチング方法

【課題】 エッチング処理が困難な材料に対しても適用可能であり、サイドエッチングを抑制し、且つエッチング処理面が平滑である良好なパターン形状を得ることができるミストエッチング装置及びミストエッチング方法を提供すること。

【解決手段】 エッチング液をミスト化するミスト生成部と、エッチング対象物をエッチングするエッチング部とを備えており、前記ミスト生成部は、エッチング液が収容され且つミスト化されるミスト生成容器と、前記エッチング液をミスト化するミスト生成機構と、生成された前記ミストを前記ミスト生成容器外へ排出するミスト排出口とからなり、前記エッチング部には、前記ミストが導入されるミスト導入口と前記エッチング対象物とが備えられ、該エッチング部で前記ミストが蒸気化されることを特徴とするミストエッチング装置とする。

(もっと読む)

半導体装置の製造方法

【課題】レジスト膜のスリミング時にその膜厚の消費を抑制する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基体11上に複数の絶縁層25と複数の導電層WLとを交互に積層して積層体を形成する工程と、積層体上にレジスト膜50を形成する工程と、レジスト膜50をマスクにして絶縁層25及び導電層WLをプラズマエッチングする工程と、ホウ素、リン及びヒ素の少なくとも1つを含むガスを用いたプラズマ処理により、レジスト膜50の上面に、ホウ素、リン及びヒ素の少なくとも1つを含む硬化層51を形成する工程と、レジスト膜50の上面に硬化層51が形成された状態で、酸素を含むガスを用いたプラズマ処理によりレジスト膜50の平面サイズをスリミングする工程と、を備えた。

(もっと読む)

マスクの製造方法、及び半導体装置の製造方法

【課題】開孔径が均一で開孔径の制御が容易な、微細化に適した開孔パターンを有するマスクを製造する。

【解決手段】第1及び第2のマスク層内に開孔を設ける。この後、第1のマスク層内の開孔の径よりも第2のマスク層内の開孔の径を、Xの量だけ大きくする。この後、第2のマスク層内の開孔内にマスク材料を形成することによって第2のマスク層内の開孔内に、Xの径の空洞部を形成する。この空洞部を開孔として有する第2のマスク層及びマスク材料を、マスクとして形成する。

(もっと読む)

実質的にアンダカットのないシリコンを絶縁体構造上に作製するエッチング工程

【課題】シリコン・オン・インシュレータ界面のアンダカットを実質的に抑制する方法を提供する。

【解決手段】垂直方向に一様なエッチングを行うように様々なサイズの凹部内のイオン充電を制限するためにイオン密度が低減される反応性イオン・エッチング工程を仕上げエッチング段階として使用することによってアンダカットが実質的になくなる、シリコン・オン・インシュレータ基板に異方性プラズマ・エッチングを施す方法を開示する。

(もっと読む)

ビア構造とそれを形成するビアエッチングプロセス

【課題】ビア構造とそれを形成するビアエッチングプロセスを提供する。

【解決手段】ビアエッチングプロセスは、丸角とテーパ型側壁プロファイルを有するスルーサブストレートビアを形成する。その方法は、半導体基板を提供するステップと、半導体基板上に、ハードマスク層とパターン化フォトレジスト層を形成するステップと、ハードマスク中に開口を形成して、半導体基板の一部を露出するステップと、パターン化されたフォトレジスト層とハードマスク層をマスキング要素として、半導体基板の少なくとも一部を通過するビアを形成するステップと、トリミングプロセスを実行して、ビアの頂角を丸くするステップと、フォトレジスト層を除去するステップと、からなる。

(もっと読む)

フォトマスク、フォトマスクの製造方法、及びプラズマエッチングチャンバシステム

【課題】極紫外線フォトマスク、フォトマスクの製造方法、及びプラズマエッチングチャンバシステムを提供する。

【解決手段】極紫外線フォトマスク、フォトマスクの製造方法、及びプラズマエッチングチャンバシステム装置が提供される。極紫外線フォトマスクの製造方法は、フォトマスク基板10上に上部膜を形成した後、上部膜をパターニングして傾いた側壁を有する上部パターン45を形成する段階を含む。上部膜をパターニングする段階は、上部膜の上部面に傾いた第1方向に平行に運動する荷電された粒子を使用して、上部膜を異方性エッチングする段階を含む。

(もっと読む)

半導体装置とその製造方法

【課題】キャパシタを備えた半導体装置とその製造方法において、キャパシタの品質を向上させること。

【解決手段】第1の導電膜19、誘電体膜20、及び第2の導電膜21をこの順に形成する工程と、第2の導電膜21をパターニングして、複数の上部電極21aを形成する工程と、レジストパターン27の側面27bが後退するエッチング条件を用いて、該レジストパターン27をマスクにしながら誘電体膜20をエッチングし、キャパシタ誘電体膜20aを形成する工程と、第1の導電膜19をパターニングして下部電極19aを形成する工程と、上部電極19aの上の層間絶縁膜33にホール33aを形成する工程と、ホール33aに導体プラグ37を埋め込む工程とを有し、端部の上部電極21a上のホール37の形成予定領域が、側面27bが後退した後のレジストパターン27により覆われる半導体装置の製造方法による。

(もっと読む)

電極形成方法および半導体素子

【課題】電極パタンを精度よく形成する。

【解決手段】半導体基板の一方面(コンタクト層10)上に、SiO2膜12−1、SiN膜14−1、SiO2膜12−2、およびSiN膜14−2を順に積層した4層の絶縁膜を形成する工程と、それら4層の絶縁膜にコンタクト層10の表面まで貫通するコンタクトホールを形成する工程と、SiO2膜12に対するエッチングレートがSiN膜14に対するエッチングレートより高い薬液(たとえばフッ酸)を用いて、コンタクトホールに露出したSiO2膜12−2の側面をコンタクトホールに露出したSiN膜14−2の側面より所定長だけ後退させる工程と、コンタクトホールに露出したコンタクト層10上に、SiN膜14−2に当接しない厚さを有する電極層20−1を蒸着により形成する工程と、上記薬液を用いて、SiN膜14−2をSiO2膜12−2とともに除去する工程と、を含む。

(もっと読む)

薄膜トランジスタの作製方法及び表示装置の作製方法

【課題】マスク数の少ない薄膜トランジスタ及び表示装置の作製方法を提供する。

【解決手段】第1の導電膜102と、絶縁膜104と、半導体膜106と、不純物半導体膜108と、第2の導電膜110とを積層し、この上に多階調マスクを用いて凹部を有するレジストマスク112を形成し、第1のエッチングを行って薄膜積層体を形成し、該薄膜積層体に対してサイドエッチングを伴う第2のエッチングを行ってゲート電極層116Aを形成し、その後ソース電極及びドレイン電極等を形成することで、薄膜トランジスタを作製する。

(もっと読む)

半導体素子及びその製造方法

【課題】チャネルが上下方向に形成されるトランジスタアレイ内における各トランジスタの駆動電圧の伝達効率を増大させるための半導体素子及びその製造方法を提供すること。

【解決手段】本発明の半導体素子は、複数の柱パターンと、各々の前記柱パターンを囲むゲート絶縁膜と、各々の前記ゲート絶縁膜を囲み、かつ、隣接する前記ゲート絶縁膜間を連接する導電膜とを備え、該導電膜は、ゲート電極及び配線として機能することを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】歪み発生層に緩和が生じにくい半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたゲート電極15と、ゲート電極15の両側面上に形成され、断面L字状の内側サイドウォール17Bと、半導体基板11におけるゲート電極15の両側方の領域に埋め込まれた歪み発生層19とを備えている。内側サイドウォール17Bは、5×1019/cm3以上の炭素を含む炭素含有シリコン酸化膜からなる。歪み発生層19は、1%以上の炭素を含む炭素含有シリコンエピタキシャル層を有する。

(もっと読む)

基板処理方法

【課題】半導体デバイスの小型化要求を満たす寸法の開口部をエッチング対象の膜に形成することができる基板処理方法を提供する。

【解決手段】シリコン基材上にTEOS膜51、TiN膜52、反射防止膜53及びフォトレジスト膜54が順に積層され、フォトレジスト膜54は反射防止膜53の一部を露出させる開口部55を有するウエハWにおいて、CF系デポ性ガスであるCHF3ガス及びハロゲン系ガスであるHBrガスの混合ガスから生成されたプラズマによって露出する反射防止膜53をエッチングしてTiN膜52の一部を露出させた後に、開口部55の側面にデポ56を堆積させることにより開口部55の幅(CD値)を調整し、その後、Cl2ガス及びN2ガスの混合ガスから生成されたプラズマによって露出したTiN膜52をエッチングする。

(もっと読む)

半導体基板の製造方法及び薄膜トランジスタの製造方法

【課題】寸法制御性を向上させ、生産性の低下を抑制することができる半導体基板の製造方法を提供すること。

【解決手段】本発明に係る半導体基板の製造方法は、第1の半導体膜及び前記第1の半導体膜上に形成される第2の半導体膜を含む積層膜を有する半導体基板の製造方法であって、積層膜上にレジストパターンを形成するレジストパターン形成工程と、フッ素原子を含むガス及び塩素原子を含むガスを含む混合ガスを用いたドライエッチングにより、レジストパターンを介して第1の半導体膜の端部をテーパ形状にエッチングするエッチング工程とを有し、エッチング工程では、第1の半導体膜の端部のテーパ形状の表面は、庇状のレジストパターンに覆われてエッチングされ、第2の半導体膜の縦方向のエッチングレートが、第1の半導体膜の縦方向のエッチングレートより大きい。

(もっと読む)

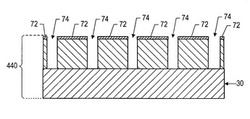

半導体装置のリセスゲート製造方法

【課題】リセスゲート工程中にリセス領域のエッチング工程で尖状のホーン(Horn)が発生することを抑制できる半導体装置のリセスゲート製造方法を提供すること。

【解決手段】シリコン基板21をエッチングし、活性領域を画定するトレンチ22を形成するステップと、該トレンチをギャップフィルする素子分離膜23を形成するステップと、前記活性領域のチャネル予定領域を開口させ、酸化膜と非晶質カーボン膜とが積層されたハードマスク膜を前記シリコン基板上に形成するステップと、前記ハードマスク膜をエッチング障壁(エッチングマスク)として前記チャネル予定領域を1次エッチングおよび2次エッチング(前記2次エッチングは前記非晶質カーボン膜を取除いた後に行う)の順序でエッチングし、デュアルプロファイルを有するリセス領域100を形成するステップとを含む。

(もっと読む)

半導体素子の製造方法

【課題】製造コストを低減することが可能な半導体素子の製造方法を提供する。

【解決手段】この発明に従った半導体素子の製造方法は、以下の工程:GaN系半導体層形成工程(S10)、GaN系半導体層上にAl膜を形成する工程(S20)、エッチング速度が、Al膜を構成する材料より小さい材料からなるマスク層を形成する工程(S30、S40)、マスク層をマスクとして用いて、Al膜およびGaN系半導体層を部分的に除去することにより、リッジ部を形成する工程(S50)、Al膜の端面の側壁の位置をマスク層の側壁の位置より後退させる工程(S60)、エッチング速度が、Al膜を構成する材料より小さい材料からなる保護膜を、リッジ部の側面およびマスク層の上部表面上に形成する工程(S70)、Al膜を除去することにより、マスク層および当該マスク層の上部表面上に形成された保護膜の部分を除去する工程(S80)、を備える。

(もっと読む)

磁気抵抗素子の製造方法及び磁気抵抗素子

【課題】磁気特性の劣化が抑制された磁気抵抗素子を提供する。

【解決手段】磁気抵抗素子は、シリコン基板1の上面全体に磁性膜3が形成され、磁性膜3の所定パターンを形成させるための所定パターンの第1絶縁膜4が等方性エッチングにより磁性膜3の上面に形成される第1工程と、異方性エッチングにより第1絶縁膜4の所定パターンに基づいて磁性膜3が所定パターンに形成される第2工程とによって製造される。

(もっと読む)

1 - 20 / 32

[ Back to top ]