Fターム[5F004EA11]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | サイドウォール (408)

Fターム[5F004EA11]の下位に属するFターム

Fターム[5F004EA11]に分類される特許

21 - 40 / 45

基板作製方法

本発明の基板作製方法は、基板上に隔置された第1のフィーチャー及び隔置された第2のフィーチャーを形成する工程を含む。隔置された第1のフィーチャー及び隔置された第2のフィーチャーは互いに交互になるとともに、互いに間隔があけられる。隔置された第2のフィーチャーの水平幅トリミングを行う間に、隔置された第2のフィーチャーの幅は、隔置された第1のフィーチャーのどの水平幅よりも大きく水平方向にトリミングされる。第2のフィーチャーを水平方向にトリミングした後に、スペーサーが、隔置された第1のフィーチャーの側壁上及び第2のフィーチャーの側壁上に形成される。スペーサーは、隔置された第1のフィーチャーの組成とも、隔置された第2のフィーチャーの組成とも異なる組成からなる。スペーサーを形成した後に、隔置された第1のフィーチャー及び隔置された第2のフィーチャーが基板から除去される。基板はスペーサーから構成されるマスクパターンを通して処理される。他の実施形態が開示されている。 (もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】微細化に伴うコントロールゲートの非対称性や素子の形状バラツキを解消する

【解決手段】(a)ウェハ基板(15、2)の上に形成されたゲート絶縁膜(6)の上に、ワードゲート(4)を形成する工程と、(b)ウェハ基板(15、2)の表面と、ワードゲート(4)の側面と、ワードゲート(4)の上面とを覆う電荷蓄積膜(13、7)を形成する工程と、(c)電荷蓄積膜(13、7)の表面を覆う導電体膜(14)を形成する工程と、(d)導電体膜をエッチングしてコントロールゲート(5)を形成する工程とを具備する製造方法で不揮発性半導体装置を製造する。ここにおいて、コントロールゲート(5)を形成する(d)工程は、ウェハ基板(15、2)が配置されたウェハステージ(22)をカソード電極とし、カソード電極のバイアスパワーを100W以上1500W以下から選択されるエッチング条件に設定して異方性ドライエッチングを行う。

(もっと読む)

半導体素子の製造方法

【課題】パターニングされた被エッチング膜のシリサイド化を簡便に行うことのできる半導体素子の製造方法を提供する。

【解決手段】本発明の半導体素子の製造方法は、ポリシリコン膜21上にSiO2 膜22をパターンニングし、SiO2 膜22を覆うようにポリシリコン膜23を堆積した後、SiO2 膜22の側壁部分にポリシリコン電極23aを形成する。次いで、SiO2 膜22を除去した後、堆積したSiO2 膜24をエッチバックして電極23aの側壁部にSiO2 からなるサイドウォール24aを形成する。次いで、サイドウォール24aの間にポリシリコンを埋め込むことによってポリシリコン電極23bを形成し、サイドウォール24aを除去して、ポリシリコン膜21およびポリシリコン電極23a,23bをエッチバックすることでポリシリコン膜21をパターンニングする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置に含まれる半導体基板と当該半導体基板に形成される貫通孔(TSV)を含む配線との間の絶縁性を良好に保つことができる半導体装置の製造方法を提供する。

【解決手段】

貫通孔の内壁に形成された絶縁膜の開口底部に対応する部分を除く部分をエッチングレジストで被膜し、当該エッチングレジストをマスクとしたエッチングにより当該絶縁膜を除去して電極パッドを露出させた後、導電層を形成して配線する。

(もっと読む)

マスクパターンの形成方法および半導体装置の製造方法

【課題】形成された被加工材のパターンの形成履歴を判別することが可能なマスクパターンの形成方法および半導体装置の製造方法を提供すること。

【解決手段】下地領域上の第1のラインアンドスペースパターンのライン部の長側壁に側壁パターンを形成し、第1のラインアンドスペースパターンのライン部の一部を覆って保護する保護パターンを第1のラインアンドスペースパターン上に形成し、保護パターンをマスクに用いて第1のラインアンドスペースパターンのライン部をウェットエッチング除去して、第1のラインアンドスペースパターンのライン部を残存させた残存パターン部と、第1のラインアンドスペースパターンのライン部が除去された領域である第1のスペース部と、第1のラインアンドスペースパターンのスペース部を介して隣接する側壁パターン間の領域である第2のスペース部と、により構成される第2のラインアンドスペースパターンを形成する。

(もっと読む)

半導体素子の微細パターン形成方法

【課題】半導体素子の微細パターン形成方法を提供する。

【解決手段】被エッチング膜を備える基板上のセルブロック340内に第1方向に延びる第1部分542と、第1部分542と一体に形成されて第1方向とは異なる第2方向に延びる第2部分544と、をそれぞれ備える複数のモールドマスクパターン540を相互平行に配列されるように形成して、モールドマスクパターンブロック540Aを形成するステップと、基板上に複数のモールドマスクパターン540それぞれの両側壁及び上面を覆う第1マスク層を形成するステップと、第1マスク層のうち相互隣接する2個のモールドマスクパターン540間で、モールドマスクパターン540の側壁を覆っている第1マスク層の第1領域は残り、第1マスク層を一部除去して第1マスクパターンを形成するステップと、を含む半導体素子の微細パターン形成方法。

(もっと読む)

パターン形成方法、半導体製造装置及び記憶媒体

【課題】基板上の膜にプラズマエッチングにより平行なライン状のパターンを形成するエッチング方法において、露光解像度以上に微細化したパターンの製造方法を提供する。

【解決手段】基板上の酸化膜21上に、窒化膜22、酸化膜23、窒化膜の3層からなるマスク層を形成する。幅と間隔の等しく形成した窒化膜のマスクパターンの側壁にアモルファスシリコン層を堆積し、異方性エッチングにより側壁膜を形成する。これをマスクとして酸化膜23をエッチングする。この上にアモルファスシリコン38を堆積し、異方性エッチングにより側壁膜を形成する。これをマスクとして窒化膜22をエッチングし、窒化膜22からなる微細なマスクとする。

(もっと読む)

開口部側壁に形成した高分子の処理により高アスペクト比の開口部におけるエッチプロファイルの屈曲と湾曲を防止する方法

【課題】誘電体層に高アスペクト比のコンタクト開口部を形成するエッチング方法を提供する。

【解決手段】各コンタクト開口部の側壁上に導電性の高い薄膜を形成することでエッチプロファイルの湾曲又は屈曲を防止しながら高アスペクト比のコンタクト開口部をエッチングする。側壁上の薄膜の導電性はエッチ処理中に周期的に行うイオン衝突により増強される。

(もっと読む)

酸化物スペーサを使用したピッチ低減

【解決手段】基板の上側と反射防止膜(ARC)層、及びマスク特徴を伴うパターン化有機マスクの下側との間に配置されるエッチング層をエッチングするための方法が提供される。基板は、プロセスチャンバの中に載置される。ARC層は、開口される。酸化物スペーサ成長層が形成される。有機マスクの上の酸化物スペーサ成長層は、部分的に除去され、ここでは、少なくとも酸化物スペーサ成長層の上部が除去される。有機マスク及びARC層は、エッチングによって除去される。エッチング層は、酸化物スペーサ成長層の側壁を通してエッチングされる。基板は、プロセスチャンバから取り出される。 (もっと読む)

プラズマエッチング方法、プラズマエッチング装置、および記憶媒体

【課題】フォトレジストパターンを小径化しつつエッチングする際に、高レートで小径化することができ、その際のフォトレジスト膜の表面状態を良好にし、亀裂を修復することができるプラズマエッチング方法を提供すること。

【解決手段】エッチング対象膜とエッチングパターンとして開口が形成されたフォトレジスト膜とを有するウエハWをチャンバ10内のサセプタ16に配置し、チャンバ10内にCF4ガス、CH2F2ガス、C5F8ガスを含む処理ガスを導入し、上部電極34に高周波電力を印加してプラズマを生成させるとともに、 上部電極34に直流電圧を印加し、生成されたプラズマにより、フォトレジスト膜に形成された開口を小径化させつつフォトレジスト膜に形成された開口を介してエッチング対象膜をエッチングする。

(もっと読む)

パターン形成方法

【課題】幅の異なるパターンを同時に容易に形成することができるパターン形成方法を提供する。

【解決手段】被加工膜1上に複数のライン状のパターンを形成する工程と、複数のライン状のパターンの各側壁に側壁膜を形成する工程と、被加工膜1上、及び複数のライン状のパターンの各側壁に形成された側壁膜間に、複数のライン状のパターンと主元素が同一の材料である材料膜を堆積する工程と、材料膜をエッチングし、側壁膜間でライン状のパターンとして孤立させると共に、被加工膜1上でライン状のパターンより幅の広いパターンを形成する工程と、材料膜をエッチングした後、側壁膜を除去する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】上部層を除去する工程が不要な半導体装置の製造方法を提供すること

【解決手段】本発明は、半導体基板10上にシリコンからなる被エッチング層17を形成する工程と、被エッチング層17上に、酸化シリコン膜からなる中間層22と多結晶シリコンからなる上部層24とからなりパターンを有するマスク層20を形成する工程と、マスク層20をマスクに被エッチング層17をエッチングし、かつ上部層24を除去する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法に関し、ゲート電極のトリミングを良好に実施できるように、また、レジストトリミングを行ってもレジスト倒れやレジスト変形が発生しないように、更に、従来のトリミングがプラズマエッチングで実施されていることに起因する問題を解消し、更にまた、ゲート電極のトリミングに関連してサイドウォールの形成時にSTI部が過剰に損傷されないようにしようとする。

【解決手段】金属を含む材料である金属シリサイド或いは金属単体から成るゲート電極をもつ半導体装置を作製する工程に於いて、ゲート電極14Gのエッチング後にゲート部の表面を酸化させ、ゲート部を有機酸を含むガス状物質に曝露すると共に加熱して金属と有機酸との反応生成物を揮発させてゲート電極14Gのトリミングを行う。

(もっと読む)

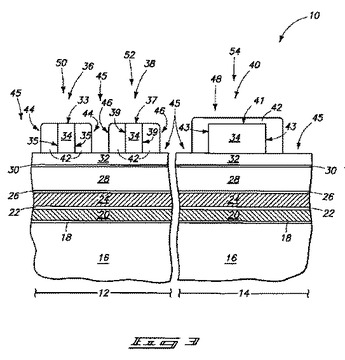

半導体構造、複数のラインを形成する方法、および高密度構造と低密度構造を単一フォトマスクで形成する方法

いくつかの実施形態は、犠牲材料に沿ったポリマースペーサーの形成、犠牲材料の除去、および集積回路の製造中におけるマスクとしてのポリマースペーサーの利用、を含む。ポリマースペーサーマスクは、例えばフラッシュメモリアレイのフラッシュゲートをパターン化するために利用されてもよい。いくつかの実施形態では、ポリマーは大きな犠牲構造と小さな犠牲構造にわたって同時に形成される。ポリマーは、小さな犠牲構造にわたってよりも、大きな犠牲構造にわたっての方が厚く、こうした厚さの差を利用して、高密度構造と低密度構造を単一フォトマスクで製造する。  (もっと読む)

(もっと読む)

半導体デバイスのクリティカルディメンジョンを縮小する方法、及び、部分的に作製される縮小クリティカルディメンジョンを有する半導体デバイス

ターゲット層上に加工を形成する方法。加工は、マスクとして使用されるレジスト層の部分のクリティカルディメンジョンと比較して、3倍或いは4倍縮小されたクリティカルディメンジョンを有する。中間層は、ターゲット層上に堆積され、レジスト層は中間層上に形成される。レジスト層をパターン化した後、第一のスペーサは、レジスト層の残っている部分のサイドウォール上に形成され、中間層の一部をマスキングする。第二のスペーサは、中間層の一部のサイドウォール上に形成される。中間層の一部を除去した後、第二のスペーサは、ターゲット層上に加工を形成するため、マスクとして使用される。部分的に作製される集積回路デバイスもまた開示される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】パターン幅が均一でないパターンを形成できるSWT(Side wall transfer)プロセスを用いたSRAM等の半導体装置の製造方法を提供する。

【解決手段】半導体基板上に、切り込み部16Aを持つダミーパターン16を形成し、半導体基板及びダミーパターン16上に側壁材17となるアモルファスシリコン等の膜を形成する。側壁材17となる膜に対して異方性エッチングを行い、ダミーパターン16の側壁に側壁材17を残す。さらに、側壁材17をマスク材としてエッチングを行い、切り込み部以外で得られた側壁材17の幅に切り込み部16Aを加えた幅を持つ部分と側壁材17の幅を持つ部分とを有するパターンを形成する。

(もっと読む)

パターン補正装置、パターン補正プログラム、パターン補正方法および半導体装置の製造方法

【課題】単独のモデルベースOPCによる二次元補正計算によって、光近接効果の補正とプロセス近接効果の補正とを、同時かつ高精度に行えるようにする。

【解決手段】設計パターンを構成するパターンエッジ上に設定される各サンプリング地点について二次元モデルベース光近接効果補正による補正計算を行う補正計算手段1bを備えて、前記サンプリング地点の周辺におけるパターンエッジの二次元分布を考慮した重み付けを導入した補正計算を行うとともに、その重み付けを、前記サンプリング地点に対して反応生成物が影響を及ぼし得る領域への重み付けを大きく、それ以外の領域への重み付けが小さくなるように行うことで、前記設計パターンに対し光近接効果補正とプロセス近接効果補正とを併せて行うようにする。

(もっと読む)

エッチング方法およびエッチング装置

【課題】 エッチング部に形成される保護膜における欠陥の発生を抑制するとともに、高いエッチングレートを実現する。

【解決手段】 エッチング方法は、処理室5内にエッチングガス1を供給して該処理室内に配置された被処理物12のプラズマエッチングを行う第1の工程と、該処理室内にパッシベーションガス2を供給して被処理物のエッチング部にパッシベーション層を生成する第2の工程と、エッチングガスおよびパッシベーションガスの両方を遮断する第3の工程を設ける。第1の工程、第2の工程および第3の工程を通じてパージガスを供給する。これら第1〜第3の工程を交互に繰り返す。

(もっと読む)

クリティカルディメンション低減およびピッチ低減のためのシステムおよび方法

【解決手段】形状を形成する方法は、下層の上に第1の材料のマスクを形成する工程を備え、マスクは、不適切なプロファイルを有する。マスクのプロファイルは補正され、形状が下層に形成される。形状を形成するためのシステムも開示されている。 (もっと読む)

エッチングマスクスタックを用いたマルチマスクプロセス

【解決手段】基板の上のエッチング層内にエッチング特徴を形成するための方法が提供される。エッチングマスクスタックが、エッチング層の上に形成される。第1のマスクが、エッチングマスクスタックの上に形成される。第1のマスクによって定められる間隔の幅を低減させる側壁層が、第1のマスクの上に形成される。側壁層を通して、第1組の特徴が、エッチングマスクスタック内へとエッチングされる。マスクおよび側壁層は、除去される。追加の特徴のステップが実施される。該ステップは、追加のマスクをエッチングマスクスタックの上に形成することと、側壁層を追加のマスクの上に形成することと、第2組の特徴を少なくとも部分的にエッチングマスクスタック内へとエッチングすることと、を含む。エッチングマスクスタック内の第1組の特徴および第2組の特徴を通して、複数の特徴がエッチング層内にエッチングされる。 (もっと読む)

21 - 40 / 45

[ Back to top ]