Fターム[5F004EA27]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | エッチバック (120)

Fターム[5F004EA27]に分類される特許

41 - 60 / 120

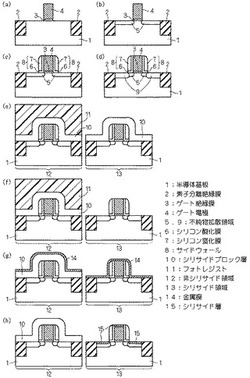

半導体装置の製造方法

【課題】シリサイドブロック層の除去方法を工夫することで、良好な抵抗値を持つシリサイド層を形成することができる半導体装置の製造方法を得る。

【解決手段】シリサイドブロック層10を反応性イオンエッチングで除去する際、反応性イオンエッチングの終点検出前よりも反応性イオンエッチングの終点検出後のほうが、イオン引き込み用のバイアス高周波電力の電圧振幅値であるVppが高くなるように設定する。

(もっと読む)

半導体デバイスの製造方法、製造装置、コンピュータプログラム、及びコンピュータ可読記憶媒体

【課題】寸法を制御すべき部位の寸法調整を可能とする半導体デバイスの製造方法、この方法に好適な半導体デバイスの製造装置を提供する。

【解決手段】開示される半導体デバイスの製造方法は、寸法を制御すべき部位の寸法を測定する寸法測定工程S8;寸法測定工程S8において得られた測定値が基準値よりも大きいか否かを判定する判定工程S9、S11;および判定工程S9、S11において測定値が基準値よりも大きいと判定された場合に部位を縮小する第1の工程と、判定工程において測定値が基準値よりも小さいと判定された場合に部位を増大する第2の工程とのいずれかを行う寸法調整工程;を含む。

(もっと読む)

半導体素子の微細パターン形成方法

【課題】半導体素子の微細パターン形成方法を提供する。

【解決手段】被エッチング膜を備える基板上のセルブロック340内に第1方向に延びる第1部分542と、第1部分542と一体に形成されて第1方向とは異なる第2方向に延びる第2部分544と、をそれぞれ備える複数のモールドマスクパターン540を相互平行に配列されるように形成して、モールドマスクパターンブロック540Aを形成するステップと、基板上に複数のモールドマスクパターン540それぞれの両側壁及び上面を覆う第1マスク層を形成するステップと、第1マスク層のうち相互隣接する2個のモールドマスクパターン540間で、モールドマスクパターン540の側壁を覆っている第1マスク層の第1領域は残り、第1マスク層を一部除去して第1マスクパターンを形成するステップと、を含む半導体素子の微細パターン形成方法。

(もっと読む)

窒化物半導体ウエハ−加工方法

【課題】 窒化物半導体結晶から裏面研削、外周研削(チャンファー)、表面研削・研磨してミラーウエハーとする際に、反りが少なく、クラックが発生せず、基板作製プロセス歩留まりが高く、デバイス面内歩留まりが高い加工方法を提案する。

【解決手段】 窒化物半導体ウエハー外周部を0〜40重量%の酸化物砥粒を含むゴム砥石或いは発泡レジンボンド砥石でチャンファーし、外周部に加工変質層を0.5μm〜10μmの厚さで残すようにする。

(もっと読む)

マスクパターン形成方法

【課題】隣接するマスクパターンが揃った状態に形成できるマスクパターンを提供する。

【解決手段】下地層のシリコン酸化膜7上にマスク用の多結晶シリコン膜8を形成する。その上にシリコン酸化膜9を成膜し、リソグラフィ処理でラインパターン9aに加工し、シリコン窒化膜を膜厚dで形成しスペーサ加工する。スペース領域にシリコン酸化膜12aを埋め込み、シリコン窒化膜を除去して間隔dの空隙部を形成する。ラインパターン9a、12aを利用してRIE加工して多結晶シリコン膜8をエッチングし、さらにCDE加工で横方向にwだけエッチングする。ラインパターン9a、12aを除去すると幅寸法Aのラインパターン8aを間隔Bを存したパターンを得ることができる。

(もっと読む)

光学素子アレイの製造方法、光学素子アレイ、及び光学系

【課題】高低差の小さい光学素子を高精度に形成し易い光学素子アレイの製造方法を提供する。

【解決手段】光学基材11上にフォトレジスト層15を設け、フォトレジスト層15を露光及び現像してフォトレジスト層15表面に凹凸形状部21を形成し、フォトレジスト層15及び光学基材11をエッチングすることで、光学基材11表面に凹凸形状部21に応じた形状を有する光学素子13を形成して光学素子アレイ10を製造する方法であり、フォトレジスト層15と光学基材10との選択比を1未満に調整してエッチングすることにより、凹凸形状部21の高低差より小さい高低差を有する光学素子13を形成する。

(もっと読む)

パターン形成方法、半導体装置の製造方法及び半導体装置の製造装置

【課題】2回目の露光工程を必要とせずに、微細なパターンを高精度で形成することができ、従来に比べて工程の簡略化と半導体装置の製造コストの低減を図ることのできるパターン形成方法、半導体装置の製造方法及び半導体装置の製造装置を提供する。

【解決手段】エッチングするマスクとなるパターンを形成するパターン形成方法であって、フォトレジストからなる第1パターン105を形成する工程と、境界層106を第1パターン105の側壁部及び頂部に形成する工程と、第2マスク材層107を、境界層106の表面を覆うように形成する工程と、境界層106の頂部が露出するように第2マスク材層107の一部を除去する工程と、境界層106をエッチングして除去して第2マスク材層107からなる第2パターンを形成する工程と、第1パターン105及び第2パターンの幅を減少させて所定幅とするトリミング工程とを具備している。

(もっと読む)

パターン形成方法、半導体製造装置及び記憶媒体

【課題】基板上の膜にプラズマエッチングにより平行なライン状のパターンを形成するエッチング方法において、前記パターンの微細化を図ること。

【解決手段】基板上のラインと溝とからなるパターンが形成されたレジストマスクに対して、薄膜の成膜、当該薄膜の異方性エッチングによるラインの両側壁への堆積物の形成、ラインの除去及び堆積物をマスクとした堆積物の下方膜のエッチングからなるダブルパターン形成工程を行って当該下方膜にラインと溝とからなるパターンを形成し、次いで堆積物を除去して更に上記ダブルパターン形成工程を行う。この時、当初のラインの幅と溝の開口幅との比を3:5に設定し、また溝に対応する薄膜の開口幅と、ラインの側壁を覆うように成膜された傾斜部分の幅と、の比がダブルパターン形成工程の1回目においては3:1、2回目においては1:1となるように薄膜を成膜する。

(もっと読む)

被覆パターン形成方法およびパターン形成方法

【課題】CVDを使用することなく、被覆されたパターンを形成することが可能な被覆パターン形成方法およびこれを利用してより高密度なパターンを形成するパターン形成方法を提供する。

【解決手段】パターン2を有する熱伝導性基板1に熱重合性組成物を塗布して塗膜3を形成したのち、ベークおよび現像をして被覆パターン7を形成する。このようにして形成された被覆パターン上に無機性組成物膜を形成したのち、エッチングすることによって、より高密度なパターンを形成することができる。

(もっと読む)

パターン形成方法、半導体製造装置及び記憶媒体

【課題】基板上の膜にプラズマエッチングにより平行なライン状のパターンを形成するエッチング方法において、露光解像度以上に微細化したパターンの製造方法を提供する。

【解決手段】基板上の酸化膜21上に、窒化膜22、酸化膜23、窒化膜の3層からなるマスク層を形成する。幅と間隔の等しく形成した窒化膜のマスクパターンの側壁にアモルファスシリコン層を堆積し、異方性エッチングにより側壁膜を形成する。これをマスクとして酸化膜23をエッチングする。この上にアモルファスシリコン38を堆積し、異方性エッチングにより側壁膜を形成する。これをマスクとして窒化膜22をエッチングし、窒化膜22からなる微細なマスクとする。

(もっと読む)

半導体メモリ素子の素子分離膜形成方法

【課題】 本発明は、トレンチの底面に流動性の第1の絶縁膜を満たし、第2の絶縁膜を形成した後に乾式エッチング工程及び湿式エッチング工程を行ってトレンチの上部の幅を広げながら第2の絶縁膜に含まれるフッ素(F;fluorine;フローリン)の量を減少させることができる半導体メモリ素子の素子分離膜形成方法を提供することを可能にすることを目的としている。

【解決手段】 トレンチが形成された半導体基板が提供される段階と、トレンチを含む半導体基板上に第1の絶縁膜を形成する段階と、第1の絶縁膜の一部を除去する第1のエッチング工程を行ってトレンチの開口部の幅を広げる段階と、第2のエッチング工程を行って第1の絶縁膜内に含まれた不純物を除去する段階と、第1の絶縁膜を含む半導体基板上に第2の絶縁膜を形成する段階とを含む構成としたことを特徴とする。

(もっと読む)

半導体素子の金属配線形成方法

【課題】フォトレジストパターンの側壁にスペーサ膜を形成し、スペーサをエッチングマスクとして用いて微細金属パターンを形成すると同時に、金属配線の断線部分は前記フォトレジストパターン間の間隔を狭めて前記スペーサが接し合うようにし、微細金属パターンが形成されることを防止する半導体素子の金属配線方法の提供。

【解決手段】半導体基板上に絶縁膜を形成する段階と、前記絶縁膜を含んだ全体構造上に複数(多数)の平行なフォトレジストパターンを形成する段階と、前記フォトレジストパターンの側壁にスペーサを形成する段階と、前記フォトレジストパターンを除去して前記絶縁膜を露出させる段階と、前記露出する絶縁膜をエッチングしてダマシンパターンを形成する段階と、前記スペーサを除去する段階と、前記ダマシンパターンを含んだ全体構造上に金属物質を形成した後、平坦化して金属配線を形成する段階とを含む、半導体素子の金属配線形成方法を提供する。

(もっと読む)

半導体素子の形成方法

【課題】ネガティブトーンSPT方法を適用するとき、スペーサ蒸着物質の間に形成されたギャップフィルポリ(gap fill poly)の最終プロファイルがラインで形成される基本原理を利用して、相互接続(interconnection)領域の具現が困難なパッドレイアウトを具現することができ、さらに、オーバレイマージンを増大させることができる半導体素子の形成方法を提供することに目的がある。

【解決手段】半導体素子の形成方法は、下部構造物が形成された半導体基板の上部に被食刻層を形成するステップと、被食刻層の上部に第1マスクパターンを形成するステップと、第1マスクパターンを含む被食刻層の上部にスペーサ物質層を均一の厚さに形成するステップと、スペーサ物質層の屈曲した領域上に第2マスクパターンを形成するステップと、第1マスクパターン及び第2マスクパターンを食刻マスクに利用して前記被食刻層を食刻し、微細パターンを形成するステップとを含む。

(もっと読む)

少なくとも1つの誘電体層を形成するための方法およびシステム

【課題】エッチングされた所望のアスペクト比の提供。

【解決手段】構造を形成するための方法が、基板の表面にわたって少なくとも1つの特徴部を形成するステップを含む。少なくとも1つの特徴部の上には窒素含有誘電体層を形成する。少なくとも1つの特徴部の少なくとも1つの側壁上の窒素含有層の第1の部分を、第1の速度で取り除き、少なくとも1つの特徴部の底部領域に隣接する基板の上の窒素含有層の第2の部分を、第2の速度で取り除く。第1の速度は第2の速度よりも大きい。窒素含有誘電体層の上に誘電体層を形成する。

(もっと読む)

半導体素子及びその製造方法

【課題】チャネルが上下方向に形成されるトランジスタアレイ内における各トランジスタの駆動電圧の伝達効率を増大させるための半導体素子及びその製造方法を提供すること。

【解決手段】本発明の半導体素子は、複数の柱パターンと、各々の前記柱パターンを囲むゲート絶縁膜と、各々の前記ゲート絶縁膜を囲み、かつ、隣接する前記ゲート絶縁膜間を連接する導電膜とを備え、該導電膜は、ゲート電極及び配線として機能することを含む。

(もっと読む)

半導体装置の製造方法

【課題】幅広のパターンと露光技術の解像度の限界以上の超微細パターンとを同時に形成する。

【解決手段】基板W上に第1のシリコン含有膜3と有機材料膜4と第2のシリコン含有膜5と、細幅と太幅のパターンを有する第1のマスク6a、6bとを順次形成し、第1のマスク6a、6bを用いて第2のシリコン含有膜5を細幅と太幅にパターニングし、第1のマスク6a、6bを除去するとともに有機材料膜4を細幅と太幅にパターニングし、第2のシリコン含有膜5と有機材料膜4と被覆して第3のシリコン含有膜7を形成し、第3のシリコン含有膜7を加工して第2のシリコン含有膜5及び有機材料膜4の側面に側壁を形成し、第2のシリコン含有膜5と該側壁を選択的に被覆する有機材料の第2のマスク8を形成し、第2のマスク8を用いて細幅にパターニングされた第2のシリコン含有膜5を除去し、細幅にパターニングされた有機材料膜4と第2のマスク8を除去する。

(もっと読む)

使用済み半導体ウエハ又は基板の再生方法

【課題】使用済みの半導体ウエハを、より少ない損失量で使用済み半導体ウエハや基板を再生する技術を提供すること。

【解決手段】(a)表面に機能層を有する使用済みの半導体ウエハ1を粗削りし、機能層を除去する工程と、(b)粗削りした半導体ウエハ1の表面に、ドライエッチングにより除去可能な保護層2を形成する工程と、(c)保護層2を形成した半導体ウエハ1をドライエッチングし、保護層2と、ウエハ1表面のうち保護層2により被覆されずに露出する部分とを除去する工程と、(d)ドライエッチングした半導体ウエハ1の平坦度を計測する工程と、を含み、(d)工程において所望の平坦度が得られない場合、所望の平坦度が得られるまで(b)から(d)までの工程を繰り返す。

(もっと読む)

半導体素子のハードマスクパターン形成方法

【課題】マトリックス状に配列された露光装備の解像度限界以下の活性領域を定義するためのハードマスクパターンの形成方法を提供する。

【解決手段】半導体基板101上に、ハードマスク膜103と第1のマスクパターン105を形成する。第1のマスクパターンと交差する第1のパターンと、第1のマスクパターン間に位置する第2のパターンを含む第2のマスクパターン107を形成する。第1のパターン間に第3のマスクパターンを形成する。第1のパターンと第1のマスクパターンが交差する領域に第1のマスクパターンが残留し、第1のパターンと第2のパターンが交差する領域に第2のパターンが残留するようにエッチングを行う。残留する第1のマスクパターン及び第2のマスクパターンをエッチングマスクとして用い、ハードマスクパターンを形成する。

(もっと読む)

半導体素子のハードマスクパターン及びその形成方法

【課題】平面上で垂直方向と水平方向にライン状のパターニング工程のみを行って露光装備の解像度以下に稠密に配列されたハードマスクパターンを形成すること。

【解決手段】半導体基板上に第2のハードマスクパターン107aを形成する段階と、第2のハードマスクパターン107aと交差する第1のパターン115aと第2のハードマスクパターン107a間に位置する第2のパターン115bを含む第3のハードマスクパターンを形成する段階と、第1のパターン115a間に第4のハードマスクパターン123aを形成する段階と、を含む半導体素子のハードマスクパターン形成方法。

(もっと読む)

半導体装置の製造方法、半導体装置の製造装置、制御プログラム及びプログラム記憶媒体

【課題】従来に比べて工程の簡略化と製造コストの低減を図ることができ、生産性の向上を図ることのできる半導体装置の製造方法、半導体装置の製造装置、制御プログラム及びプログラム記憶媒体を提供する。

【解決手段】フォトレジスト103のパターンの上にSiO2膜104を成膜する成膜工程と、SiO2膜104をフォトレジスト103のパターンの側壁部にのみ残るようにエッチングするエッチング工程と、フォトレジスト103のパターンを除去してSiO2膜104のパターンを形成する工程とを具備している。

(もっと読む)

41 - 60 / 120

[ Back to top ]