Fターム[5F004EA27]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | エッチバック (120)

Fターム[5F004EA27]に分類される特許

101 - 120 / 120

基板の処理方法、固体撮像素子の製造方法、薄膜デバイスの製造方法及びプログラム

【課題】 電子デバイスに損傷を与えることなく絶縁膜の除去量の制御を正確に行うことができる基板の処理方法を提供する。

【解決手段】 CCDセンサを製造すべく、光電変換素子210がマトリックス状に形成されたウエハW上に絶縁膜251を成膜し、導電性膜を成膜してフォトレジスト層を用いてエッチングにより転送電極221を形成する。絶縁膜及び導電性金属膜を成膜してフォトレジスト層を用いてエッチングにより層間絶縁膜222及び遮光膜223をそれぞれ形成する。次いで、シリコン窒化膜252を形成し、所望の厚さの平坦化膜253を形成するためにSiO2からなる所定の厚さの絶縁膜261を形成する。そして、絶縁膜261が形成されたウエハWをアンモニアガス及び弗化水素ガスの混合気体に所定の圧力下において暴露し、絶縁膜261を形成するSiO2から変質した生成物を所定の温度に加熱する。

(もっと読む)

微細パターン形成方法

【課題】

微細加工が可能な微細パターン形成方法を提供する。

【解決手段】

パターニングされたマスク層76の側壁にプラズマ反応生成物を堆積させてマスク層76のパターン幅を広げる第1工程と,パターン幅が広げられたマスク層76をマスクとして,第1の被エッチング層74をエッチングする第2工程と,エッチングされた第1の被エッチング層74に生じたスペース80にマスク材81を埋め込む第3工程と,スペース80に埋め込まれたマスク材を残して,第1の被エッチング層74をエッチングする第4工程と,残されたマスク材81をマスクとして,第2の被エッチング層72をエッチングする第5工程とを有することを特徴とする,微細パターン形成方法である。

(もっと読む)

エッチングプロセスのための安定化したフォトレジスト構成

【課題】エッチレイヤに特徴を形成する方法を提供する。

【解決手段】第1のマスクが前記エッチレイヤ上に形成され、前記第1のマスクは、幅を有する複数のスペースを定義する。第1のマスクは縦方向にエッチングされ、エッチングされた第1のマスクは、前記第1のマスクの前記スペースの前記幅より大きい幅を有する複数のスペースを定義する。前記エッチングされた第1のマスク上に側壁レイヤが形成され、前記側壁レイヤは、前記エッチングされた第1のマスクによって定義される前記スペースの前記幅よりも小さい幅を有する複数のスペースを定義する。前記エッチレイヤ中に前記側壁レイヤを通して特徴がエッチングされ、前記特徴は前記エッチングされた第1のマスクによって定義される前記スペースの前記幅よりも小さい幅を有する。前記マスク及び前記側壁レイヤは取り除かれる。

(もっと読む)

半導体素子のランディングプラグコンタクト形成方法

【課題】 ランディングプラグコンタクト形成のためのCMP工程時、ポリシリコン膜とゲートハードマスク窒化膜との間の段差を防止できる半導体素子のランディングプラグコンタクト形成方法を提供すること。

【解決手段】 本発明では、ランディングプラグコンタクト(LPC)の分離のためのポリシリコンリセス(Recess)のために、既存のCMP工程を用いず、2ステップのエッチバック工程を用いる。すなわち、第1エッチバック工程では、等方性ドライエッチング(部分エッチング)を通してゲート電極パターンの間の空間(コンタクトホール上部)に発生したポリシリコン膜のシーム(Seam)を除去し、第2エッチバック工程では、ポリシリコン膜とハードマスク窒化膜とのエッチング速度が類似したレシピ(Recipe)を適用して、非等方性ドライエッチングを行う。

(もっと読む)

半導体装置の製造方法

【課題】有機金属気相成長法により形成された強誘電体膜の表面モホロジーを改善することができる半導体装置の製造方法を提供する。

【解決手段】MOCVDにより形成した強誘電体膜32上に設計値よりも厚い導電膜36を形成し、次いで、導電膜36の全面を異方性エッチングによりエッチバックしたので、導電膜36の表面モホロジーを改善することができる。導電膜36の表面モホロジーが改善され平坦化されているので、フォトリソグラフィーにより導電膜36をパターニングする際に、露光入射光が色々な方向に反射することなく、設計通りの所望のパターンを形成することができる。

(もっと読む)

半導体装置の製造方法

【課題】有機金属気相成長法により形成された強誘電体膜の表面モホロジーを改善することができる半導体装置の製造方法を提供する。

【解決手段】MOCVDにより形成した強誘電体膜32上に、低粘度の材料を塗布して埋め込み層34を形成し、次いで、全面を異方性エッチングして強誘電体膜32表面の凸部頂上を除去し、次いで、強誘電体膜32表面に残存する埋め込み層34を除去する。強誘電体膜32の表面モホロジーが改善され平坦化される。フォトリソグラフィーにより導電膜36や強誘電体膜32をパターニングする際に、露光入射光が色々な方向に反射することなく、設計通りの所望のパターンを形成することができる。

(もっと読む)

半導体ウェーハの分割方法、研削装置および半導体ウェーハ分割システム

【課題】 個々の半導体チップの仕上がり厚み寸法のばらつきを低減することができる半導体ウェーハの分割方法、研削装置および半導体ウェーハ分割システムを提供する。

【解決手段】 半導体ウェーハの分割方法は、半導体ウェーハ表面3にマトリックス状に配置された半導体回路18を区画するダイシングライン17に沿って切削溝1を形成し、この半導体ウェーハ表面3にバックグラインド保護テープ19を貼付け、裏面2を僅かに球面状に湾曲させて半導体ウェーハ4を保持した状態で切削溝1が表出する直前まで裏面2を研削し、この半導体ウェーハ裏面2をプラズマエッチングすることにより切削溝1を表出させて個々の半導体チップ20に分割する。

(もっと読む)

半導体装置の製造方法

【課題】 エッジラフネスを解消してパターンを形成する。

【解決手段】 基板上に、被加工膜を形成形成し、第1マスクの材料膜である第1材料膜を形成する。そして、第1材料膜をエッチングして、第1マスクを形成する。更に、第1マスク表面を含む基板全面に、第2マスクの材料膜である第2材料膜を形成した後、第1マスクの側面に第2材料膜を残すようにして、第2材料膜をエッチングして、第2マスクを形成する。その後、第1マスク及び第2マスクをマスクとして、被加工膜をエッチングしてパターンを形成する。

(もっと読む)

Ge微結晶核付き基板の作製方法及びGe微結晶核付き基板

【課題】 基板上に、成長の核となる微結晶を作製し、その粒径と密度を制御し、大粒径多結晶Si薄膜を作製できるGe微結晶核付き基板の作製方法及びGe微結晶核付き基板を提供する。

【解決手段】 電子工業用ガラス基板、石英ガラス基板、熱酸化したSiウェーハ又はSiO2膜付き基板の上に固相成長法により島状に独立したGe微結晶を形成し、次いで酸素エッチングによってGe微結晶の粒径と密度とを、300〜600℃の範囲のエッチング温度とエッチング時間とで制御する。前記基板の上に粒径が1〜40nmのGe微結晶を、密度が1×105〜1×107個/cm2となるように分散配置した。

(もっと読む)

エッチバック方法、それを用いた無機偏光子製造方法及びそれらの方法を実現するエッチング停止制御装置、並びに製造される無機偏光子

【課題】

微細な凹部パターンに金属が埋め込まれ堆積されたパターン表面の平坦化と、パターン高さを精度よくエッチバックにより制御する。

【解決手段】

表面に微細な格子パターン12が形成されている基板10の表面上に格子パターン12を被ってアルミニウム膜14を堆積し、その上にレジスト層16を塗布し、レジスト層16には格子パターン12が形成されている領域以外の領域に開口18を設ける。レジスト層16とアルミニウム膜14をエッチバックし、SiFから発生するプラズマ強度の微分値が所定の値を越えた時点から所定の設定時間(制御時間)後にエッチングを停止する。

(もっと読む)

キャップ層を有する半導体相互接続構造上に金属層を堆積させる方法

【課題】

【解決手段】半導体ウェハの相互接続構造上に金属層を堆積させる方法を開示する。この方法では、金属導体を、キャップ層および誘電体層で被覆する。キャップ層を露出させるように、誘電体層をパターン形成する。次いで、キャップ層をスパッタ・エッチングして除去し、金属導体を露出させる。スパッタ・エッチング・プロセス中に、キャップ層がパターンの側壁に再堆積する。最後に、パターンの中に少なくとも1つの層を堆積させ、再堆積したキャップ層を被覆する。  (もっと読む)

(もっと読む)

成膜方法、成膜装置及び記憶媒体

【課題】エッチング処理を組み合わせることにより、半球状の結晶粒のサイズを小さく制御することが可能な成膜方法を提供する。

【解決手段】被処理体Wの表面に薄膜を形成する成膜方法において、成膜ガスにより前記被処理体の表面に結晶核92を形成して該結晶核92を成長させることにより半球状の結晶粒6が表面に形成された結晶粒薄膜94を形成する結晶粒薄膜形成工程と、前記結晶粒薄膜94の表面を酸化することにより酸化膜96を形成する酸化膜形成工程と、前記酸化膜96をエッチングにより除去するエッチング工程と、を有する。このように、エッチング処理を組み合わせることにより、HSGシリコン結晶粒における半球状の結晶粒6のサイズを小さく制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】厚み均一で且つ低抵抗のシリサイド層をゲート電極に有する半導体装置およびその製造方法を提供する。

【解決手段】シリサイド化する高融点金属の堆積前に、ゲート電極上面に角が発生しないように端部丸めを実施した後にシリサイド化を行ことで、熱処理時に発生する膜応力の集中を緩和し、均一でかつ十分な厚さのシリサイド層を形成する。

(もっと読む)

パターン形成方法を含む半導体装置の製造方法

【課題】 本発明は半導体装置の製造工程において、レジストなどのマスクパターンを用いる際に発生する反応生成物等のレジスト等への不均一な付着によるパターン形状等の不良を生じさせず、また、寸法精度が良好な微細パターンの形成方法を提供することを目的とする。

【解決手段】 パターン形成方法を含む半導体装置の製造方法として、第1の薄膜の側壁に第2の薄膜を形成し、その側壁に形成された第2の薄膜の先端部が不均一にならないように、平坦化法により、精度良くエッチバックして揃える。

(もっと読む)

近接場露光によるレジストパターンの形成方法、及び該レジストパターンの形成方法を用いた基板の加工方法、デバイスの作製方法

【課題】高アスペクトなパターンの形成が可能となる近接場露光によるレジストパターンの形成方法、及び該レジストパターンの形成方法を用いた基板の加工方法、デバイスの作製方法を提供する。

【解決手段】近接場露光用マスクを基板上に形成したレジスト層に近接させ、該マスクの面側に光を照射した際に該マスクの微小開口から滲み出る近接場光を用いて露光し、前記レジスト層にマスクパターンを転写する近接場露光によるレジストパターンの形成方法において、前記基板上に、近接場光のしみ出し深さ以上の厚さのネガ型レジスト層を形成する工程と、前記ネガ型レジスト層を、前記近接場光を用いて露光する露光工程と、前記露光されたネガ型レジスト層を現像液で現像し、該ネガ型レジスト層の厚さよりも浅い領域にパターンを形成する現像工程と、を少なくとも有する構成とする。

(もっと読む)

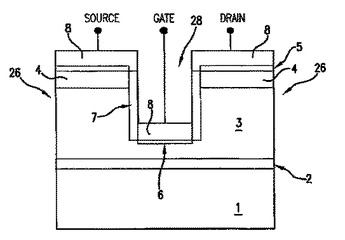

自己整列型炭化ケイ素半導体デバイスおよびそのデバイスの作成方法

電流安定性の改善された自己整列型炭化ケイ素パワーMESFETおよびそのデバイスの作成方法を記載する。このデバイスは、ゲート凹部により分離されたレイズドソースおよびドレイン領域を含み、低ゲートバイアスにおいてでさえ表面トラップ効果が低減されるため、電流安定性が改善される。このデバイスは自己整列型プロセスを用いて作成され得る。このプロセスでは、金属エッチマスクを用いて、nドープのSiCチャネル層上のn+ドープのSiC層を備えた基板がエッチングされてレイズドソースおよびドレイン領域が規定される。この金属エッチマスクがアニールされ、ソースおよびドレイン・オームコンタクトが形成される。単層または多層の誘電性フィルムが成長または堆積され異方性エッチングされる。蒸着または別の異方性堆積技術を用いて、ショットキーコンタクト層および最終金属層が堆積され、オプションとして、誘電性層の等方エッチングされる。  (もっと読む)

(もっと読む)

動的な液体メニスカスを用いたストレスフリーのエッチング処理

【課題】動的な液体メニスカスを用いたストレスフリーのエッチング処理

【解決手段】パターン形成された半導体基板上の不均一性を平坦化および制御するためのシステムおよび方法は、パターン形成された半導体基板を受け取る工程を備える。パターン形成された半導体基板はパターン内の複数の特徴を導電性配線材料で満たされ、導電性配線材料は過剰部分を有する。過剰部分のバルクは除去され、過剰部分の残りの部分は不均一性を有する。不均一性はマッピングされ、不均一性を補正するために、最適の液体が決定され、動的液体メニスカスエッチング処理レシピが作成される。そして、不均一性を補正して、過剰部分の残りの部分をほぼ平坦化するために、動的液体メニスカスエッチング処理レシピを使用した動的液体メニスカスエッチング処理が実施される。

(もっと読む)

基板処理方法、プラズマ室および半導体デバイス

【課題】

【解決手段】基板処理のシステムおよび方法には、プラズマ室に基板を装填しプラズマ室の圧力を所定の圧力設定値に設定することが含まれる。プラズマ領域を構成するいくつかの内面が約200℃以上の処理温度に加熱される。プラズマを形成するために処理ガスがプラズマ領域に注入され、基板が処理される。

(もっと読む)

半導体装置の製造方法

【課題】残渣を生じることなく、精度良くエッチング可能な半導体装置の製造方法の提供。

【解決手段】ゲート酸化膜により段差を持つポリシリコン膜7を積層後、フォトレジスト6を全面に塗布し、パターン形成せず段差が見えるまでフォトレジストをアッシングする。そのあとRIEにより段差部のエッチングを行い、段差を緩和する。この後、フォトレジストをパターンしSiO2に対する選択比の高いHBrでエッチングを行うことにより、残渣を生じないエッチングができる。

(もっと読む)

多結晶シリコン薄膜の平坦化方法

【課題】 多結晶シリコン薄膜の表面に形成された突起を容易且つ確実に除去することができる多結晶シリコン薄膜の平坦化方法を提供することを目的とする。

【解決手段】 多結晶シリコン薄膜を炭素(C)とフッ素(F)と水素(H)とを少なくとも含有するガスのプラズマに曝すことにより突起を除去して多結晶シリコン薄膜の表面を容易且つ確実に平坦化することができる。

(もっと読む)

101 - 120 / 120

[ Back to top ]