Fターム[5F004EA27]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | エッチバック (120)

Fターム[5F004EA27]に分類される特許

21 - 40 / 120

マスクの製造方法、及び半導体装置の製造方法

【課題】開孔径が均一で開孔径の制御が容易な、微細化に適した開孔パターンを有するマスクを製造する。

【解決手段】第1及び第2のマスク層内に開孔を設ける。この後、第1のマスク層内の開孔の径よりも第2のマスク層内の開孔の径を、Xの量だけ大きくする。この後、第2のマスク層内の開孔内にマスク材料を形成することによって第2のマスク層内の開孔内に、Xの径の空洞部を形成する。この空洞部を開孔として有する第2のマスク層及びマスク材料を、マスクとして形成する。

(もっと読む)

マスクパターンの形成方法及び半導体装置の製造方法

【課題】SWPにおいて、側壁部の形状の対称性を高め、被エッチング膜をエッチングするときの加工精度を向上させることができるマスクパターンの形成方法を提供する。

【解決手段】基板上の被エッチング膜の上に形成されたシリコン膜よりなる第1のライン部が配列したシリコン膜パターンの表面を等方的に被覆するように、カーボン膜を成膜する成膜工程S18と、カーボン膜を第1のライン部の上部から除去すると共に、第1のライン部の側壁部として残存するように、カーボン膜をエッチバックするエッチバック工程S19と、第1のライン部を除去し、側壁部が配列したマスクパターンを形成するシリコン膜除去工程S20とを有する。

(もっと読む)

マスクパターンの形成方法及び半導体装置の製造方法

【課題】SWPによりマスクパターンを形成する場合に、反射防止膜のエッチング工程を省略し、マスクパターンのパターン倒れを防止することができるマスクパターンの形成方法を提供する。

【解決手段】レジストパターン列の表面を等方的に酸化シリコン膜で被覆するステップS14と、レジストパターン列の間をカーボン膜で埋め込むと共に、上部をカーボン膜で被覆するステップS15と、カーボン膜を、レジストパターン列の上部から除去すると共に、レジストパターン列の間に残存するようにエッチバック処理するステップS16と、残存するカーボン膜を除去すると共に、レジストパターン列の上部を被覆する酸化シリコン膜をエッチバック処理するステップS17と、レジストパターン列をアッシング処理し、中央部と、中央部を両側から挟む膜側壁部とを有する、酸化シリコン膜よりなる第1のマスクパターン列を形成するステップS18とを有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体ウェハ単位でAPCを行う場合の運用性を向上可能な半導体装置の製造方法を提供する。

【解決手段】例えば、今回ロット(#1)を対象として露光処理後にレジストパターン寸法の計測が行われ、この計測値を反映して次回ロット(#2)における各半導体ウェハ単位の露光条件が算出される際に、今回ロット(#1)の露光着工枚数が足りないような状況や、今回ロット(#1)内の計測枚数が不足するような状況が生じる。そこで、露光着工枚数が足りない状況(例えば、スロット1〜12内の11,12が存在しない状況)では、近似式による外挿計算を利用して12枚分の計測値を導出し、計測枚数が不足する状況(例えば、スロット1〜12内の1,6,12の分しか得られない状況)では、近似式による内挿計算を用いて12枚分の計測値を導出する。

(もっと読む)

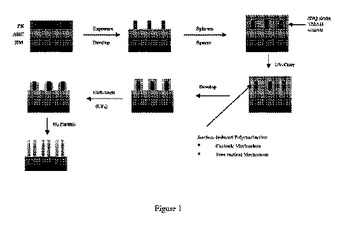

ダブルパターニング方法及び材料

シルセスキオキサン樹脂をパターン形成フォトレジストの上に塗布し、硬化して、パターン表面上に硬化シルセスキオキサン樹脂を生成する。次に未硬化シルセスキオキサン樹脂を除去し、パターン表面上に硬化シルセスキオキサン樹脂を残す。水平表面上の硬化シルセスキオキサン樹脂を除去し、下にあるフォトレジストを露光する。このフォトレジストを除去し、硬化シルセスキオキサンのパターンを残す。任意で、新規パターンを下層へ転写することができる。  (もっと読む)

(もっと読む)

基板処理方法

【課題】処理対象膜において形状の乱れが少ない開口部を形成することができる基板処理方法を提供する。

【解決手段】被処理膜37と、被処理膜37の上に形成された複数の小幅のライン38aからなるフォトレジスト膜と、各ライン38aの間において露出する被処理膜37及びライン38aを覆うSi酸化膜40とを有するウエハにおいて、Si酸化膜40にエッチングを施してフォトレジスト膜の各ライン38aと被処理膜37を露出させ、露出したフォトレジスト膜を選択的に除去し、さらに、残存するSi酸化膜40(一対のライン42a,42b)にエッチングを施す。

(もっと読む)

微細構造の製造方法

【課題】高精細な微細構造を低コストで効率よく製造する。

【解決手段】頂部15の周縁部を残して頂部17をエッチングし、周縁部からなる壁部21aを含んだ微細構造を形成する形成工程と、を有する。形成工程は、頂部15と側部16とを連続して被覆する被覆膜を形成する被覆処理と、頂部15が露出するまで被覆膜33をエッチングするとともにエッチングにより形成されるエッチング凹部の底面15aよりも側部17を覆う部分の被覆膜33を突出させて突出部34にするエッチング処理と、底面15aと突出部34とを連続して被覆する第2被覆膜35を形成する第2被覆処理と、底面15aが露出するまで第2被覆膜35をエッチングして突出部34を被覆する部分の第2被覆膜35を保持して膜パターン36とし、膜パターン36をマスクとして底面15aをエッチングする第2エッチング処理とを含む。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上とホール内に形成したカーボンナノチューブを絶縁膜に損傷を与えることなく絶縁膜上から除去すること。

【解決手段】配線15a上方に絶縁膜17、18を形成し、絶縁膜17、18をパターニングして配線15aに達するホール17aを形成し、ホール17a内と絶縁膜17、18上面にカーボンナノチューブ22を形成し、カーボンナノチューブ22の層の上に第2絶縁膜23を形成し、第2絶縁膜23をエッチングすることによりカーボンナノチューブ22を露出するとともに、カーボンナノチューブ22の層の凹部に第2絶縁膜23を残し、カーボンナノチューブ22をエッチングしてカーボンナノチューブ22の上端の位置を揃え、さらにカーボンナノチューブ22上の第2絶縁膜23をエッチングし、カーボンナノチューブ22をエッチングして絶縁膜17上面から除去するとともにホール17a内に残す工程を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチ開口部に傾斜面を形成し、耐圧低下を防止できる半導体装置及びその製造方法を提供することができる。

【解決手段】本発明にかかる製造方法は、半導体基板10にトレンチ21を形成する工程と、絶縁膜23をトレンチ21に堆積させる工程と、プラズマエッチングによりトレンチ21底部の絶縁膜23をエッチングするとともに、トレンチ開口部21aに半導体基板主面10aに対して傾斜角αをなす傾斜面25を同時に形成する工程と、半導体基板10の上面からトレンチ21底部の絶縁膜23に亘って半導体基板10及びトレンチ21を被覆するゲート絶縁膜24を形成する工程と、ゲート絶縁膜24上にゲート電極22を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】第1領域におけるライナー膜の膜厚と、第2領域におけるライナー膜の膜厚とが互いに異なる半導体装置において、コンタクトホールの形成時に、活性領域及び素子分離領域に削れが形成されることを防止する。

【解決手段】ゲート構造体Gbが密に配置された第1領域におけるライナー膜22b及び層間絶縁膜23に、互いに隣接するゲート構造体同士の間の領域を開口して、底部に第1の膜厚を有するライナー膜が残存する第1のコンタクトホール28rを形成する。次に、ゲート構造体が疎に配置された第2領域におけるライナー膜及び層間絶縁膜に、互いに隣接するゲート構造体同士の間の領域を開口して、底部に第2の膜厚を有するライナー膜が残存する第2のコンタクトホール34rを形成する。次に、第1のコンタクトホールの底部に残存するライナー膜、及び第2のコンタクトホールの底部に残存するライナー膜を除去する。第1の膜厚と第2の膜厚とは、同等である。

(もっと読む)

空隙を充填するべく低抵抗率のタングステン膜を堆積させる方法

【課題】抵抗率が低く、表面粗度が低く反射率が高いタングステンを、CVD法により基板上の間隙または凹状特徴部分に充填する方法を提供する。

【解決手段】基板に設けられた凹状部分を部分的に充填するタングステンバルクを堆積した後で、堆積されたタングステンの上部分を除去する。上部分の除去は、活性化されたフッ素種に基板を暴露することによって行われる。堆積されたタングステン粒子のうち急峻で突出している突起の頂点を選択的に除去することによって、除去処理は、凹状部分の側壁に沿ってタングステンを研磨することになる。堆積−除去のサイクルを複数回実行して、凹状部分を埋める。このようにして凹状部分が充填されると、CMPにおいてコアリング(coring)が発生しにくくなる。

(もっと読む)

半導体装置の製造方法

【課題】トレンチゲート型MOSFETのゲートを有する半導体素子の、歩留まりおよび信頼性を高める。

【解決手段】ゲート電極9aの加工時のエッチングガスとして、フッ素系のガスであるSF6を使用することでエッチングの等方性を強め、ゲート電極9aの表面を滑らかに加工することができ、製品の歩留まりおよび信頼性を向上することができる。また、ゲート電極9aの加工時のn+型単結晶シリコン基板1の温度を5℃とすることで、エッチング残渣が加工表面へ再付着するのを防ぎ、加工表面を滑らかな形状にすることにより、トレンチゲート型MOSFETの歩留まりおよび信頼性を高めることができる。

(もっと読む)

半導体装置の製造方法

【課題】芯材パターンの側壁に形成するマスク材を利用したパターン形成において工程数を削減できる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、露光により酸を発生する酸発生剤を含む芯材パターン15を下地膜上に形成する工程と、芯材パターン15における長手方向の端部15aを除く部分を選択的に露光する工程と、芯材パターン15から酸の供給を受けて架橋可能なマスク材16を芯材パターン15を覆うように下地膜上に供給する工程と、マスク材16をエッチバックして、芯材パターン15の上面を露出させると共に、マスク材16における芯材パターン15の端部15aに形成された部分を除去し、芯材パターン15の側壁に形成されたマスク材側壁部16aを残す工程と、芯材パターン15を除去し、下地膜上に残されたマスク材側壁部16aをマスクにして下地膜を加工する工程と、を備えた。

(もっと読む)

半導体素子の製造方法

【課題】パターニングされた被エッチング膜のシリサイド化を簡便に行うことのできる半導体素子の製造方法を提供する。

【解決手段】本発明の半導体素子の製造方法は、ポリシリコン膜21上にSiO2 膜22をパターンニングし、SiO2 膜22を覆うようにポリシリコン膜23を堆積した後、SiO2 膜22の側壁部分にポリシリコン電極23aを形成する。次いで、SiO2 膜22を除去した後、堆積したSiO2 膜24をエッチバックして電極23aの側壁部にSiO2 からなるサイドウォール24aを形成する。次いで、サイドウォール24aの間にポリシリコンを埋め込むことによってポリシリコン電極23bを形成し、サイドウォール24aを除去して、ポリシリコン膜21およびポリシリコン電極23a,23bをエッチバックすることでポリシリコン膜21をパターンニングする。

(もっと読む)

パターン形成方法、半導体装置の製造方法及び半導体装置の製造装置

【課題】2回目の露光工程を必要とせずに、露光限界よりも細い微細なパターンを高精度で形成することができ、従来に比べて工程の簡略化と半導体装置の製造コストの低減を図ることのできるパターン形成方法、半導体装置の製造方法及び製造装置を提供する。

【解決手段】マスクとなるパターンを形成する方法であって、第1パターン105を形成する工程と、第1パターン105の幅をトリミングする工程と、境界層106を第1パターン105の表面に成膜する工程と、境界層106の表面に第2マスク材層107を形成する工程と、境界層106の頂部が露出するように第2マスク材層107の一部を除去する工程と、境界層106をエッチングして第1パターン105を露出させるとともに、第2マスク材層107を上部に有する第2パターンを形成する工程とを具備している。

(もっと読む)

表面処理方法、表面処理用マスク、及び光学デバイス

【課題】被処理物が大面積であっても品質にバラツキが生じ難く、且つ高速に凹凸加工を施すことができ、量産性及び低コスト化に優れた表面処理方法、及びそれに用いる表面処理用マスクを提供すること。また、当該表面処理方法により処理された基板を有する光学デバイスを提供すること。

【解決手段】被処理物の表面に凹凸を形成するための表面処理方法であって、第1粒子と第1粒子よりもエッチング耐性が低い第2粒子とを有する粒子群を含んで構成される表面処理用マスクを、被処理物表面に配置する工程と、表面処理用マスクが配置された被処理物の表面に対し、エッチング処理を施し、被処理物の表面に凹凸を形成するエッチング工程と、を有することを特徴とする表面処理方法である。また、当該表面処理方法に用いる表面処理用マスク、及び当該表面処理方法により得られる基板を有する光デバイスである。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写プロセスにおいて側壁パターンの曲がりを抑制する。

【解決手段】側壁パターンをマスクとする下地絶縁膜の加工を、フルオロカーボン系のガスを用いたドライエッチングにより行い、その際に、側壁をなすシリコン膜の膜厚をxnmとすると、Vdc<46x−890の関係式を満たす自己バイアス電圧Vdcを基板に印加する。

(もっと読む)

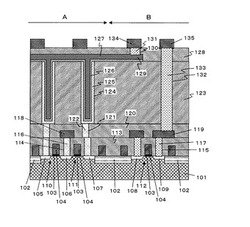

半導体装置及びその製造方法

【課題】Cuを主体とする配線について、配線抵抗を低く維持するとともに、ストレスマイグレーション耐性及びエレクトロマイグレーション耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上方に形成された層間絶縁膜28、30と、層間絶縁膜28、30に形成されたビアホール34及び配線溝36内に形成され、Ta膜より成るバリアメタル膜38と、バリアメタル膜38上に形成されたTi膜40と、バリアメタル膜38及びTi膜40が形成されたビアホール34及び配線溝36内にそれぞれ埋め込まれ、Cuより成る導体プラグ44及び配線46とを有し、Ti膜40の膜厚が、配線溝36の底部において4nm以下になっている。

(もっと読む)

半導体装置の製造方法

【課題】膜パターンが倒れないように半導体装置を製造する方法を提供する。

【解決手段】半導体装置の製造方法は、基板上にSiO2膜の膜パターンを形成する工程と、SiO2膜の膜パターンを両側面から挟むように複数のSi膜の膜パターンを形成する工程と、SiO2膜の膜パターンの上面と、複数のSi膜の膜パターンの上面と露出した側面とを被覆するようにレジスト膜を形成する工程と、SiO2膜の膜パターンの上面が露出するまでレジスト膜の一部を除去する工程と、レジスト膜が除去された後に、露出したSiO2膜の膜パターンをウェット処理により除去する工程と、SiO2膜の膜パターンが除去された後に、レジスト膜の残部をドライ処理により除去する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】研磨粒子によるパターン形成不良を抑制して、高い歩留まりでデュアルダマシン配線を形成可能な半導体装置の製造方法を得ることを目的とする。

【解決手段】本発明における半導体装置の製造方法は、半導体基板1の上面上に絶縁膜6、配線溝パターン8を形成したハードマスク7を形成する。次に、配線溝パターン8を埋め込むように第1のレジスト膜9を形成し、ハードマスク7上の第1のレジスト膜9を除去して平坦化する。次に、第1のレジスト膜9の表面を除去し、第1のレジスト膜9の表面を洗浄する。次に、接続孔パターン14を形成した第2のレジスト膜13を形成し、第1のレジスト膜9および絶縁膜6の表層に接続孔パターン14を転写する。次に、ハードマスク7の配線溝パターン8をマスクとして、絶縁膜6をエッチングして配線溝8および接続孔14を形成する。次に、絶縁膜6に形成された配線溝8および接続孔14に金属を埋め込む。

(もっと読む)

21 - 40 / 120

[ Back to top ]