Fターム[5F032AC01]の内容

Fターム[5F032AC01]に分類される特許

1 - 20 / 141

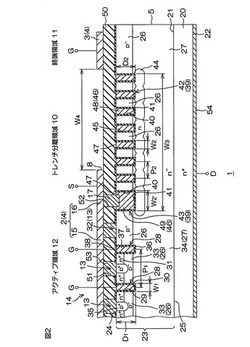

半導体装置およびその製造方法

【課題】素子特性を悪化させず、アクティブ領域を終端領域に対して、簡単な方法により電気的に独立させることができ、さらには素子サイズの小型化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】エピタキシャル層23のアクティブ領域12と終端領域11との間に、エピタキシャル層23の表面24を形成するように、当該表面24に沿って全体にわたって形成されたチャネル層26を、ゲートトレンチ28の深さD1と同じ深さD2を有するアイソレーショントレンチ39で分断する。互いに同じ深さのゲートトレンチ28およびアイソレーショントレンチ39は、同一のエッチング工程で形成される。

(もっと読む)

半導体装置の製造方法およびCMOSイメージセンサーの製造方法

【課題】 半導体装置に発生するノイズを低減する

【解決手段】 シリコン基板100の第1部分110を覆い、シリコン基板100の第1部分110に隣接する第2部分120を覆わない窒化シリコン膜200をマスクとしてシリコン基板100を熱酸化することにより、酸化シリコン膜300を形成する。窒化シリコン膜200をマスクとして酸化シリコン膜300のバーズビーク部310の下へ斜めイオン注入を行うことにより、不純物領域121を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ワードライン間の素子分離を行い、メモリセルの微細化が可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10内に形成されたビットライン14と、ビットライン14上にビットライン14の長手方向に連続して設けられた絶縁膜ライン18と、ビットライン14間の半導体基板10上に設けられたゲート電極16と、ゲート電極16上に接して設けられ、ビットライン14の幅方向に延在したワードライン20と、ビットライン14間でありワードライン20間の半導体基板に形成されたトレンチ部22と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】 JFET等のような低ノイズ特性が要求される半導体装置において、発生するノイズを低減すると共に、半導体装置を小さい寸法で製造する。

【解決手段】 半導体装置は、半導体層(101)に形成された素子分離(102)、第1導電型の不純物層(104)、第1導電型のソース領域(106)、第1導電型のドレイン領域(107)、第2導電型のゲート領域(105)、絶縁膜(108)を介して形成された制御電極(109)を備える。制御電極(109)に電圧を印加すると、半導体装置の動作中に制御電極(109)の下の不純物層(104)に空乏層を発生させることができ、キャリアは絶縁膜(108)と不純物層(104)の界面から離れて流れる。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とボディ領域とを接続したトランジスタを有する半導体装置に関し、動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の素子分離絶縁膜と、第1の素子分離絶縁膜により画定され、第1の素子分離絶縁膜よりも浅いウェルと、ウェル内に形成され、ウェルよりも浅く、ウェルの第1の部分とウェルの第2の部分とを画定する第2の素子分離絶縁膜と、第1の部分上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、第2の部分においてウェルに電気的に接続され、ゲート電極とウェルとを電気的に接続する配線層とを有し、第2の素子分離絶縁膜下の領域のウェルの電気抵抗が、ウェルの他の領域の同じ深さにおける電気抵抗よりも低くなっている。

(もっと読む)

半導体装置

【課題】正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置を提供する。

【解決手段】メインセルとセンスセルとをトレンチ分離構造1dによって絶縁分離する。これにより、メインセルのコレクタに対して100V以上の高電圧が印加されても、それに起因するノイズが電流検出用の出力端子に誘起されないようにできる。また、センスセルのエミッタ電位がセンス抵抗Rsに流れる電流によって上昇しても、メインセルのエミッタと電気的に完全に分離されているため、寄生トランジスタが動作することもない。勿論、抵抗層14から発生させられたノイズが電流検出用の出力端子に誘起されることも抑制できる。したがって、正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置とすることが可能となる。

(もっと読む)

半導体装置

【課題】半導体基板に向かって流れ込む回生電流又は寄生バイポーラトランジスタのオン電流を、チップサイズを増大させることなく低減できるLDMOSトランジスタの実現が課題となる。

【解決手段】N+型ドレイン層13等が形成されたN型エピタキシャル層5からなるN型層5aを、N型エピタキシャル層5の表面からN+型埋め込み層2まで延在するP型ドレイン分離層6で取り囲む。P型ドレイン分離層6とP型素子分離層3に囲まれたN型エピタキシャル層5からなるN型層5bにその表面から内部に延在するP型コレクタ層7を形成する。これにより第1導電型のドレイン分離層6をエミッタ、前記第2導電型の分離層5bをベース、前記コレクタ層7をコレクタとする寄生バイポーラトランジスタを形成しサージ電流を接地ラインに流す。

(もっと読む)

半導体装置の製造方法

【課題】500keV〜3000keVのエネルギーイオン注入を行っても、目的とする領域に精度良く、不純物拡散領域を形成することができる半導体装置の製造方法を提供すること。

【解決手段】半導体基板10の表面に、イオン注入を行うための開口部42Aを持つレジストパターン42を形成する工程であって、開口部42Aの縁部42Bがイオン注入予定領域50の外縁部50Aよりも内側に位置するようにして、レジストパターン42を形成する工程と、レジストパターン42から露出した半導体基板10の表面の少なくとも一部に対して、ウエットエッチングを施す工程と、レジストパターン42をマスクとし、500keV〜3000keVのエネルギーイオン注入により、半導体基板10の深部に不純物拡散領域(例えばN−型不純物拡散領域12)を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】IGBT形成領域とその制御回路等形成領域とをPN接合分離法で分離し、且つIGBTからの漏れ電流が発生せず、制御回路等のCMOSトランジスタがラッチアップ等することのない高品質の半導体装置を実現する。

【解決手段】P型半導体基板1上に多層からなるN型エピタキシャル層3等を形成する。該N型エピタキシャル層3等をP+型分離層13等によりIGBT形成領域50と制御回路等形成領域40に分離する。該IGBT形成領域50の最下層の前記N型エピタキシャル層3と前記P型半導体基板1の双方に延在するN+型埋め込みガード層2を形成する。また該N+型埋め込みガード層2の端部と接続し前記エピタキシャル層3等の表面まで延在するN+型ガードリング9等を形成する。前記N+型埋め込みガード層2と該N+型ガードリング9等に囲まれた前記エピタキシャル層3等にIGBTを形成する。

(もっと読む)

固体撮像装置及びその製造方法

【課題】素子を分離するための素子分離部による不具合の発生確率を低減する。

【解決手段】フォトダイオード310が内部に形成された半導体基板500と、素子分離部420とを備える。素子分離部420は、該素子分離部420の少なくとも一部が、半導体基板500に形成された溝410の内部に充填されるように形成される。素子分離部420は、溝410の内部の下方に形成されたシリコン酸化膜421と、溝410の内部の上方に形成されたシリコン酸化膜422とから構成される。シリコン酸化膜421の密度は、シリコン酸化膜422の密度より小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】素子分離領域が低濃度拡散領域におけるゲート電極近傍の部分より浅い場合に半導体装置の平面寸法の大型化を抑制しつつ素子分離をより確実に行う。

【解決手段】半導体装置100は、第1導電型の不純物領域(N型ウェル領域51)と、第2導電型の低濃度拡散領域(P型オフセット拡散領域3)を有する複数のMOSトランジスタ(高圧PチャネルMOSトランジスタ11)と、素子分離領域6を有する。低濃度拡散領域は、素子分離領域6に接する第1部分3aは素子分離領域6と同じ深さであるか又はそれよりも浅く、第1部分3aよりもゲート電極1側の第2部分3bは素子分離領域6よりも深い。更に、第1導電型であり、不純物領域よりも不純物濃度が高く、素子分離領域6の底面と、素子分離領域6に隣接する低濃度拡散領域の各々とに接しているチャネルストッパー領域(N型チャネルストッパー領域9)を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子面積が小さくしかも素子の耐圧の高い半導体装置およびその製造方法を提供する。

【解決手段】基板11と、基板上に設けられた一導電型の第1の半導体層13と、第1の半導体層上に設けられた一導電型で低不純物濃度の第2の半導体層15と、アイソレーション領域50によって分離された素子領域71内に形成されたMOSトランジスタ75と、素子領域内に一主面から第1の半導体層に達して設けられた一導電型で高不純物濃度の領域17と、領域17とMOSトランジスタのドレイン領域35との間に設けられた絶縁領域60であって、一主面10から第1の半導体層13に達し、基板11に達していない絶縁領域60とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コスト削減、サイズ縮小ができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法であって、P型Si基板21の主面にトレンチ22を形成することによって、エンハンスメント型FET形成用の幅狭部分とでプレション型FET形成用の幅広部分とを含むアクティブ領域25を形成する工程と、主面の法線に対して30度〜45度の範囲内の注入角で、且つ、注入方向が法線を中心に相対的に回転するように、Si基板21に対してP型不純物を注入して、幅広部分にP型のチャンネルストッパー領域25aを形成すると共に、幅狭部分にP型チャンネル拡散領域25bを形成する工程と、トレンチ22をトレンチ素子分離絶縁層26で埋める工程と、ゲート絶縁膜27を形成する工程と、Si基板21上にN型不純物を注入して第2の部分にN型チャンネル拡散領域28を形成する工程と、ゲート電極29を形成する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物の拡散によるナローチャネル効果の発生を抑制することを可能にする半導体装置を提供する。

【解決手段】半導体基体1と、半導体基体1に少なくとも一部が埋め込まれた、素子分離のための絶縁層2と、半導体基体1内に形成された不純物領域を含んで成る能動素子と、絶縁層2と半導体基体1との間に形成された、負の固定電荷を有する膜11とを含んで半導体装置を構成する。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】耐放射線性を有する絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】一部がチャネル領域をなすp型の半導体層11と、半導体層11の上部に活性領域21Bを定義する素子分離絶縁膜21と、チャネル領域にキャリア注入口を介してキャリアを注入するn型の第1主電極領域12と、チャネル領域から、キャリアを排出するキャリア排出口を有するn型の第2主電極領域13と、活性領域21Bの上に設けられたゲート絶縁膜22と、ゲート絶縁膜22の上に設けられ、第1主電極領域12と第2主電極領域13との間を流れるキャリアの流路に直交する主制御部、主制御部に交わる2本のガード部241,242を有してπ字型をなすゲート電極24と、第2主電極領域13のゲート幅方向の両端側に設けられたp型のリーク阻止領域61,62とを備える。

(もっと読む)

半導体装置

【課題】高電源電圧回路部に十分なラッチアップ耐性を持たせつつ、低電源電圧回路部においても高電源電圧回路部と同じトレンチ分離を使用しながら高い素子集積度を持った半導体装置を提供する。

【解決手段】トレンチ分離構造を有する半導体装置において、高電源電圧回路部には少なくとも一つのウエル領域とMOS型トランジスタが形成されて成り、ウエル領域の端部近傍のトレンチ分離領域下面にラッチアップを防止するための一対のキャリア捕獲領域を形成し配置する。

(もっと読む)

半導体装置およびその製造方法

【課題】形成する素子に要求される素子間耐圧や素子内部耐圧に応じたディープトレンチ膜を有する半導体装置を提供する。

【解決手段】P型のシリコン基板11上に、N+型埋め込み層12と、N型半導体層13と、が積層された基板10と、基板10にN+型埋め込み層12の形成位置よりも深く形成され、基板10内の素子形成領域内を区画するディープトレンチ20と、ディープトレンチ20の内壁に沿って形成される側壁酸化膜23,24と、ディープトレンチ20内を埋めるTEOS膜を含むディープトレンチ膜26と、ディープトレンチ膜26で区画される素子形成領域に形成されるLDMOSと、を備え、ディープトレンチ20は、N+型埋め込み層12の上面よりも浅い位置の境界深さまでの第1のディープトレンチ21と、境界深さから底部までの第1のディープトレンチ21よりも小さい開口径を有する第2のディープトレンチ22によって構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置およびその製造方法の提供。

【解決手段】相対的に薄いゲート絶縁膜25を有するMOSトランジスタが形成される領域のフィールド絶縁膜端23を相対的に厚いゲート絶縁膜24で覆うことにより、フィールド絶縁膜下部に形成された反転防止拡散層31から相対的に薄いゲート絶縁膜25を有するMOSトランジスタのチャネル領域33をオフセットさせることによって、フィールド絶縁膜の膜厚ばらつきや相対的に厚い第一のゲート絶縁膜24のエッチングばらつき、および反転防止拡散層によるチャネル端の濃度変動の影響を受けず、MOSトランジスタのチャネル幅を短く設計した際に生じる狭チャネル効果の影響を抑制することが可能となり、素子特性が安定した半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】寄生MOSの形成を抑制し、且つ狭チャネル化を低減した半導体装置の製造方法を提供する。

【解決手段】支持基板2と絶縁層3と半導体層4とを含むSOI基板1に、ソース領域及びドレイン領域が第1導電型であるトランジスターを形成する半導体装置の製造方法であって、半導体層4上に、第1の耐酸化性膜6a’を形成する工程と、第1の耐酸化性膜6a’をマスクにして、第1導電型とは導電性の異なる、第2導電型の不純物7を半導体層4に注入する工程と、第2導電型の不純物7を半導体層4に注入する工程の後、第1の耐酸化性膜6a’の側面に第2の耐酸化性膜6b’を形成する工程と、第1の耐酸化性膜6a’及び第2の耐酸化性膜6b’をマスクにして、素子分離層8を形成する工程と、素子分離層8を形成する工程の後、第1の耐酸化性膜6a’及び第2の耐酸化性膜6b’を半導体層4上から除去する工程とを有することを特徴とする半導体装置100の製造方法。

(もっと読む)

1 - 20 / 141

[ Back to top ]