Fターム[5F032BB08]の内容

Fターム[5F032BB08]に分類される特許

1 - 20 / 103

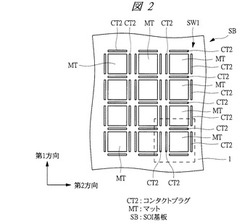

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。

【解決手段】SOI基板SB上に形成されたマットMT内に複数のMOSFETを有する半導体装置において、BOX膜を貫き支持基板に達するコンタクトプラグCT2を形成することで、マットMTの周囲を、SOI基板SBの主面に沿う第1方向または第1方向に直交する第2方向に延在する複数のコンタクトプラグCT2により囲む。これにより、コンタクトプラグCT2をガードリングとして用い、マットMTの外部に流れる高周波信号に起因してマットMT内にノイズが発生することを防ぐ。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、2つの埋め込みゲート用の溝部8a,8bによって分断された3つの活性領域6a,6b,6cのうち、中央部に位置する活性領域6bを分断するビットコンタクト用の溝部11の両側面に、埋め込みゲート用の溝部8a,8bの底面と同程度の深さで不純物を拡散させることによって形成された第1の不純物拡散層13a,13bと、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

バッファ付きフィンFETデバイス

【課題】フィンFETデバイスのロバストネスを向上させる。

【解決手段】トランジスタデバイスであって、半導体基板と、半導体基板に形成されたバッファ付き垂直フィン状構造であって、垂直フィン状構造は、ドレーン領域とソース領域512との間にチャンネル領域514を含む上位の半導体層と、上位の半導体層の下のバッファ領域304であって、第1のドーピング極性を有するバッファ領域と、第1のドーピング極性と反対である第2のドーピング極性を有するウェル領域302の少なくとも一部分と、バッファ領域とウェル領域との間の少なくとも1つのp−n接合であって、該垂直フィン状構造の水平断面を少なくとも部分的にカバーする少なくとも1つのp−n接合とを含むバッファ付き垂直フィン状構造と、上位の半導体層のチャンネル領域をおおい形成されたゲートスタックとを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】 対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和する。

【解決手段】 半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板を貫通する貫通電極の周囲に形成される環状の絶縁分離部において、絶縁分離部を構成する酸化膜の応力により絶縁分離部周囲の半導体基板が変形する。

【解決手段】絶縁分離部の基板側に深さ方向に圧縮応力を与える第1の膜4を形成し、第1の膜4上に深さ方向に引張応力を与える第2の膜6膜を形成し、その際、第1及び第2の膜の膜厚を圧縮応力と引張応力とがほぼ釣り合うように調整する。

(もっと読む)

半導体装置

【課題】基板を介したクロストークを抑制でき、放熱性が高い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置1は、半導体基板10を備える。前記半導体基板の内部には空洞11が形成されている。また、前記半導体基板の内部には、前記空洞を前記半導体基板の上面に連通させる連通孔12も形成されている。前記半導体装置は、さらに、前記空洞及び前記連通孔の内面上に設けられた絶縁膜13と、前記空洞及び前記連通孔の内部に埋め込まれ、熱伝導率が前記絶縁膜の熱伝導率よりも高い伝熱部材14と、前記半導体基板における前記空洞の直上域に形成された素子21,22と、を備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】隣接セル間干渉を抑制した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1メモリストリングと、ソースコンタクトと、第2メモリストリングと、シールド導電層と、を備えた不揮発性半導体記憶装置を提供する。第1メモリストリングは、第1軸に沿って並ぶ第1メモリセル及び第2メモリセルを含む。ソースコンタクトは、第1メモリストリングのソース側の端に設けられる。第2メモリストリングは、第1軸に対して直交する第2軸に沿って第1メモリセルと並ぶ第3メモリセルを含み、第1軸に沿って延在する。シールド導電層は、第1メモリストリングと第2メモリストリングとの間において第1軸に沿って延在し、ソースコンタクトと電気的に接続される。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とボディ領域とを接続したトランジスタを有する半導体装置に関し、動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の素子分離絶縁膜と、第1の素子分離絶縁膜により画定され、第1の素子分離絶縁膜よりも浅いウェルと、ウェル内に形成され、ウェルよりも浅く、ウェルの第1の部分とウェルの第2の部分とを画定する第2の素子分離絶縁膜と、第1の部分上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、第2の部分においてウェルに電気的に接続され、ゲート電極とウェルとを電気的に接続する配線層とを有し、第2の素子分離絶縁膜下の領域のウェルの電気抵抗が、ウェルの他の領域の同じ深さにおける電気抵抗よりも低くなっている。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域をライン上に形成することで、コンタクト領域のばらつきを抑制し、リセスゲート電極を用いて隣接するトランジスタ間の分離を行う構造を提供する。

【解決手段】半導体基板中に第1の方向に延在して形成される素子分離領域で分離された活性領域と、第1の方向と交差する第2の方向に延在し、素子分離領域及び活性領域に連通する溝内に形成されたリセスゲート電極と。リセスゲート電極で分断された活性領域であって、リセスゲート電極の底面より浅い領域に形成されるMOSトランジスタのソース/ドレイン領域とを備えた半導体装置であって、リセスゲート電極は、MOSトランジスタのゲート電極を構成する制御ゲート電極162tと、第1の方向に隣接するMOSトランジスタを素子分離する補助ゲート電極162iで構成される。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】基板上で第1方向に延在するラインパターンと、ラインパターンの端部から、第1方向と異なる方向に延在する分岐ラインパターンとをそれぞれ含む第1導電ライン;第2導電ライン;第3導電ラインとを含む半導体素子であり、中間に位置する導電ラインの分岐ラインパターンは、他の導電ラインの分岐ラインパターン間に位置し、長さもさらに短い。これにより、コンタクト・パッドが、導電ラインの分岐ラインパターンと一体に形成されうる。

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】基板の内部であって、活性領域と素子分離領域との境界領域にコンタクトホールが形成された場合に、基板に流れるリーク電流を抑制できるようにする。

【解決手段】半導体基板10の上部に形成された素子分離領域10a及び活性領域10bと、半導体基板10の上に形成された絶縁膜12と、絶縁膜12に少なくとも活性領域10bを露出するように形成され、且つ、素子分離領域10aにおける活性領域10bとの境界領域を含む領域に形成されたコンタクトホール13と、コンタクトホール13における、活性領域10bの上に位置する第1の底面の上に形成された第1のバリアメタル膜14と、コンタクトホール13における、最下端に位置する第2の底面と第1の底面とをつなぐ壁面上に形成された第2のバリアメタル膜17とを備える。第2のバリアメタル膜17は、第1のバリアメタル膜14よりも比抵抗が高いことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタ素子の電気的特性の変動と、放熱性の低下とが抑制された半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の一面側表層に、トランジスタ素子のPN接合部が形成され、半導体基板の一面上に位置するトランジスタ素子の電極の一部が、貫通電極を介して、半導体基板の裏面に配置された対応するワイヤボンディング用パッドと電気的に接続されている。そして、半導体基板の一面全面を覆うように、一面上に配置されたリードと、トランジスタ素子の電極の一部が電気的に接続されている。

(もっと読む)

半導体記憶装置

【課題】記憶素子間の干渉が少ない半導体記憶装置を提供する。

【解決手段】半導体記憶装置1において、シリコン基板11の上層部分の一部にSTI16を設け、シリコン基板11の上層部分をY方向に延びる複数本のアクティブエリアAAに区画する。そして、上下方向(Z方向)におけるアクティブエリアAAの中間部分27の幅Wmを、上部26の幅Wu及び下部28の幅Wlよりも細くする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】素子分離層の幅を狭くしつつ、素子分離層の底部を介した電流のリークを抑制する。

【解決手段】基板111と、ゲート絶縁膜121と、第1のゲート電極層122と、トランジスタ間の第1のゲート電極層122及びゲート絶縁膜121を貫通し、基板111とゲート絶縁膜121との界面S1よりも深い位置に底面を有する素子分離溝Tと、素子分離溝Tに埋め込まれた素子分離層131と、ゲート間絶縁膜123と、選択トランジスタ102を構成するゲート間絶縁膜123を貫通する第1の穴H1と、周辺トランジスタ103を構成するゲート間絶縁膜123を貫通する第2の穴H2と、素子分離層131上のゲート間絶縁膜123を貫通し、素子分離層131とゲート間絶縁膜123との界面S2よりも深い位置に底面を有する第3の穴H3と、第1から第3の穴H3に埋め込まれた部分を有する第2のゲート電極層124とを備える。

(もっと読む)

誘電体分離型半導体集積装置、及び半導体集積装置の製造方法

【課題】微細なMOS素子と共存する。

【解決手段】支持基板5と、埋込シリコン酸化膜6と、第1高濃度不純物層9及び低不純物濃度層とからなる活性層15、とで構成されるSOI基板を適用した誘電体分離型半導体集積装置10において、高耐圧半導体素子形成領域を囲んで形成される素子分離領域は、多重溝100と、多重溝の側壁に設けた第1酸化膜105と、第1酸化膜と隣接して多重溝側壁に沿って形成された第2高濃度不純物層110と、第2高濃度不純物層の略上部にLOCOS酸化膜50を介して配設された低抵抗層P2と、前記低抵抗層に積層された第2酸化膜70,75,80と、を備えて構成され、低抵抗層は、第2高濃度不純物層、あるいはドレイン電極と略同電位であり、第2酸化膜の表面でエミッタ電極が前記高耐圧半導体素子形成領域から隣接領域へ引き出されている。

(もっと読む)

半導体装置

【課題】ダイカット時に回路素子領域に近い箇所でクラックが発生することを防止する。

【解決手段】半導体基板100上に形成された回路素子領域と、前記回路素子領域を囲むように形成されたダイカット領域と、前記回路素子領域とダイカット領域との間の少なくとも一部に形成された保護パターンと、を備え、前記保護パターンは、前記半導体基板の表面部に形成された素子分離領域102と、素子分離領域102よりダイカット領域側に形成され、素子分離領域102より幅の狭い素子分離領域103と、素子分離領域102と素子分離領域103との間に形成された素子領域150と、素子分離領域102上に形成されたゲート層106と、ゲート層106上に層間絶縁膜111を介して形成された配線層113と、前記配線層113上に形成されたパッシベーション層120と、素子分離領域103のダイカット領域側に隣接して形成されたゲート層107と、を有する。

(もっと読む)

固体撮像装置とその製造方法、および撮像装置

【課題】本発明は、画素サイズの縮小化に伴う光電変換部の占有面積の縮小化を抑え、感度の向上を可能にする。

【解決手段】半導体基板11に、入射光を光電変換して信号電荷を得る光電変換部12と、光電変換部12で生成された信号電荷を出力する画素トランジスタ部13と、光電変換部12と画素トランジスタ部13を有する画素部の周辺に形成された周辺回路部14と、光電変換部12と画素トランジスタ部13と周辺回路部14を電気的に分離する素子分離領域15を有し、画素トランジスタ部13の周囲の素子分離領域15は、半導体基板11表面より高く形成された絶縁体部16を有し、画素トランジスタ部13のトランジスタの第1ゲート電極22は半導体基板11上にゲート絶縁膜21を介して絶縁体部16間に形成されている。

(もっと読む)

1 - 20 / 103

[ Back to top ]