Fターム[5F032CA10]の内容

素子分離 (28,488) | 関連技術 (4,816) | 基板の材質(単結晶シリコンは不要) (383) | 砒化ガリウム (103)

Fターム[5F032CA10]に分類される特許

1 - 20 / 103

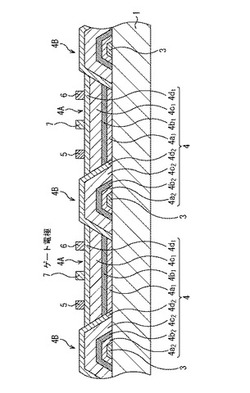

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】空隙AG1の埋め込み絶縁膜4が除去される前に側壁保護膜3´にてトンネル絶縁膜5の側壁を覆うことにより、埋め込み絶縁膜4とトンネル絶縁膜5との間でウェット処理のエッチング選択比が確保できない場合においても、トンネル絶縁膜5を保護できるようにする。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】電極間絶縁膜7下において、埋め込み絶縁膜9が上下に分離されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、空隙AG1にて分離された上側の埋め込み絶縁膜9は電極間絶縁膜7下に積層し、下側の埋め込み絶縁膜9はトレンチ2内に配置する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】レンチ2内に埋め込まれた埋め込み絶縁膜3の一部を除去することで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1を形成し、空隙AG1は、制御ゲート電極8下に潜るようにしてトレンチ2に沿って連続して形成する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】トレンチ2内に埋め込まれた第2の埋め込み絶縁膜4の一部が除去されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、浮遊ゲート電極6間が完全に埋め込まれないようにして制御ゲート電極8間にカバー絶縁膜10が掛け渡されることで、ビット線方向にDBに隣接する浮遊ゲート電極6間に空隙AG2が形成されている。

(もっと読む)

空洞半導体基板、ならびに空洞半導体基板および半導体素子の製造方法

【課題】 生産性に優れる空洞半導体基板、ならびに空洞半導体基板および半導体素子の製造方法を提供する。

【解決手段】 空洞半導体基板1は、支持基板10と、半導体基板20と、を有する。この半導体基板20は、下主面21bの上に一体的に形成され且つ当該下主面21bから突出している脚部22を介して支持基板10の上に張り合わされている。この半導体基板20は、下主面21bが支持基板10から離隔している。

(もっと読む)

シングルゲートフィンFET及びその製造方法

【課題】新規なFinFET構造及びその製造方法を提供する。

【解決手段】シングルゲートフィンFET構造100は、2つの拡大された頭部、及び当該拡大された頭部と下層の超薄型ボディとを連結する2つの徐々に細くなる首部を有するアクティブフィン構造を含む。2つのソース/ドレイン領域102,104が、2つの拡大された頭部にそれぞれドープされる。絶縁領域26が、2つのソース/ドレイン領域の間に挿入される。溝分離構造24が、音叉形状のフィン構造の一方の側に配置される。片面サイドウォールゲート電極12bが、アクティブフィン構造における、溝分離構造とは反対側の垂直なサイドウォールに配置される。

(もっと読む)

フィン型電界効果トランジスタ

【課題】フィン型電界効果トランジスタを提供する。

【解決手段】本発明は、フィン型電界効果トランジスタの分離構造に関する。フィン型電界効果トランジスタの例は、主表面からなる基板と、基板の主表面から突出する複数のフィン構造と、フィン構造の間に位置する複数の分離構造と、からなる。各フィン構造は、変化位置により分けられる上部分と下部分からなり、この変化位置は、フィン構造の側壁と基板の主表面の角度85度のところにあり、上部分は、この基板の主表面と実質上、垂直な側壁、及び、第一幅を有する頂面を有し、下部分は、上部分の両側のテーパ型側壁、及び、第一幅より大きい第二幅を有する底部を有する。複数の分離構造は、それぞれ、基板の主表面から、変化位置上の点に延伸する。

(もっと読む)

電界効果トランジスタの製造方法

【課題】高集積度化でき、電気射特性を維持しながら、低コスト化できる電界効果トランジスタの製造方法を実現する。

【解決手段】誘電性絶縁部層2’によって被覆されているバルクシリコンウエハ基板1’上に島状の各活性エリア10を互いに隣り合うようにそれぞれ設定する。バルクシリコンウエハ基板1’の表面上において、各活性エリア10を電界効果トランジスタの本体領域をフィン部3、5の形状で突出するように露出させて形成するために、誘電性絶縁部層2’を厚さ方向にエッチバックして絶縁体層2を形成する。上記本体領域に、チャネル領域部、上記チャネル領域部上のゲート誘電体8、ゲート誘電体8上のゲート電極4、および、ゲート電極4の自己整合マスクにより、チャネル領域部とは反対の伝導性型である不純物原子のドープによりソース領域部5およびドレイン領域部3を形成する。

(もっと読む)

シャロートレンチアイソレーションプロセス

【課題】トレンチ構造の歪み導入要素によりに歪み導入されたチャネルを持つMOSトランジスタのリーク電流を改善する。

【解決手段】MOSトランジスタ106のチャネル領域108に、第1トレンチ構造55a、第2トレンチ構造55bによる歪み導入要素だけでなく、別の歪み導入要素として、MOSトランジスタ106表面上にコンフォーマルに設けられた窒化シリコンキャップ層130を設ける。別の態様では、チャネル領域108内の歪みは、ガス種、例えば水素、酸素、ヘリウムまたは別の希ガスをゲート110またはチャネル領域108の下の領域内に注入することによって導入される。

(もっと読む)

半導体構造、半導体構造を形成する方法、および半導体デバイスを操作する方法(信号忠実度および電気的分離が強化されたSOI無線周波スイッチ)

【課題】SOI(セミコンダクタ・オン・インシュレータ)基板内の底部半導体層からの半導体デバイスについて強化された信号分離を可能とする半導体構造、これを製造する方法、およびこれを操作する方法を提供する。

【解決手段】底部半導体層10と反対の導電性タイプを有するドープ接点領域18は底部半導体層10内の埋め込み絶縁体層20の下に設ける。少なくとも1つの導電ビア構造47,77は、相互接続レベル金属ライン94から、中間工程(MOL)誘電体層80、最上部半導体層30内の浅いトレンチ分離構造33、および埋め込み絶縁体層20を通り、ドープ接点領域18まで延びる構造とする。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】基板と当該基板に形成される化合物半導体とを電気的に絶縁しつつ、結晶性に優れた化合物半導体を備えた半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に設けられたシード結晶と、シード結晶の上方に設けられた化合物半導体と、シード結晶と化合物半導体との間に設けられ、シード結晶よりも大きな抵抗率を有する高抵抗層とを備え、シード結晶と化合物半導体とが格子整合または擬格子整合している半導体基板を提供する。

(もっと読む)

半導体装置、半導体製造装置および半導体装置の製造方法

【課題】半導体基板上の凹部が逆テーパ形状やオーバーハング形状を有する場合においても、埋め込み性や膜質の劣化を抑制しつつ、埋め込み絶縁膜の応力を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上にトレンチ5を形成し、熱CVD法を用いることで、トレンチ5内の一部を埋め込む埋め込み絶縁膜6を半導体基板1上に成膜し、埋め込み絶縁膜6の成膜時よりも高い温度にて埋め込み絶縁膜6を熱処理した後、熱CVD法を用いることで、トレンチ5内の一部を埋め込む埋め込み絶縁膜7を埋め込み絶縁膜6上に成膜し、埋め込み絶縁膜7の成膜時よりも高い温度にて埋め込み絶縁膜7を熱処理した後、熱CVD法を用いることで、トレンチ5内を完全に埋め込む埋め込み絶縁膜を埋め込み絶縁膜7上に成膜し、埋め込み絶縁膜の成膜時よりも高い温度にて埋め込み絶縁膜を熱処理する。

(もっと読む)

拡幅活性領域を有する半導体素子

半導体素子(10)を半導体層内に、そして半導体層の上に形成する方法が実現される。トレンチ(18,20,22)は、第1活性領域(24,26,28,30)に隣接して形成される。前記トレンチには、絶縁材料(32,34,36)が充填される。マスクパターン(48,50,52)を前記トレンチの中央部分の上に形成して、前記トレンチのうち、前記マスクパターンの第1側部と前記第1活性領域との間に位置する第1側部を露出させる。前記トレンチの前記第1側部を掘り込むエッチングを行なう工程によって、第1窪み(54,56,58,60)が前記トレンチに残る。第1エピタキシャル領域(62,66)を前記第1窪みに成長させて、前記第1活性領域を延長して前記第1窪みを包含することにより、第1拡幅活性領域を形成する。  (もっと読む)

(もっと読む)

自然酸化物の成長を低減するためのプラズマクリーンプロセスによるパッシベーション層の形成

本明細書に記載される実施形態は、基板上の自然酸化表面を取り除くと同時に、下層の基板表面をパッシベートするための方法を提供する。一実施形態において、プロセスチャンバ内に、酸化物層を有する基板の位置決めを行い、基板の第1の温度を約80℃未満に調整し、プロセスチャンバ内において、約10以上のNH3/NF3モル比を有するアンモニア及び三フッ化窒素を含むガス混合物からクリーニングプラズマを生成し、基板上にクリーニングプラズマを凝縮することを含む方法が提供される。ヘキサフルオロ酸アンモニウムを含む薄膜が、プラズマクリーニングプロセスの間に、自然酸化物から部分的に形成される。本方法は、さらに、プロセスチャンバ内において、約100℃以上の第2の温度まで基板を加熱しつつ、基板から薄膜を取り除き、その上にパッシベーション表面を形成することを含む。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】電荷蓄積層及び制御ゲートを有する半導体記憶装置のバックバイアス効果による影響を低減させることにより集積度を向上させ、占有面積を増加させずに浮遊ゲートと制御ゲートとの容量の比をより一層増大させるとともに、製造プロセスに起因するセル特性のばらつきが抑制された半導体記憶装置を提供する。

【解決手段】半導体基板100と、少なくとも1つの島状半導体層110、該島状半導体層の側壁の周囲の全部又は一部に形成された電荷蓄積層及び制御ゲートから構成される少なくとも1つのメモリセルとを有する半導体記憶装置であって、前記メモリセルの島状半導体層が不純物拡散層により前記半導体基板から電気的に絶縁されてなることを特徴とする半導体記憶装置。

(もっと読む)

半導体装置及び電子機器

【課題】耐熱性の低い基板をベース基板とするSOI基板を用いて高性能な半導体装置を提供することを課題とする。また、機械的な研磨を行わずに高性能な半導体装置を提供することを課題とする。また、該半導体装置を用いた電子機器を提供することを課題とする。

【解決手段】絶縁基板上の絶縁層と、絶縁層上の接合層と、接合層上の単結晶半導体層と有し、単結晶半導体層は、その上部表面における凹凸形状の算術平均粗さが1nm以上7nm以下とする。または、凹凸形状の二乗平均平方根粗さが1nm以上10nm以下であっても良い。または、凹凸形状の最大高低差が5nm以上250nm以下であっても良い。

(もっと読む)

半導体装置の作製方法

【課題】生産コストを削減することができる半導体装置の作製方法の提案を課題とする。

【解決手段】ボンド基板の下に容器を配置した後、ボンド基板を劈開させることでボンド基板から形成される複数の第1の半導体膜を、容器に載置し、複数の第1の半導体膜を容器から拾い上げて、複数の第1の半導体膜どうしが離隔するようにベース基板に貼り、複数の第1の半導体膜をエッチングすることで、複数の第2の半導体膜を形成する半導体装置の作製方法。

(もっと読む)

半導体装置の作製方法及び製造装置

【課題】生産コストを削減することができる半導体装置の作製方法、及び該作製方法を用いる製造装置の提案を課題とする。

【解決手段】ボンド基板(半導体基板)をベース基板(支持基板)に貼り合わせた後に、該ボンド基板を劈開させて半導体膜を形成するのではなく、先にボンド基板を複数箇所において劈開することで複数の第1の半導体膜(マザーアイランド)を形成してから、該複数の第1の半導体膜をベース基板に貼り合わせる。そして、上記複数の第1の半導体膜をそれぞれ部分的にエッチングすることで、1つの第1の半導体膜から単数または複数の第2の半導体膜(アイランド)を形成し、該第2の半導体膜を用いて半導体素子を作製する。複数の第1の半導体膜は、半導体素子が有する第2の半導体膜がレイアウトされるべき領域を少なくともカバーするように、上記レイアウトに合わせてベース基板に貼り合わせる。

(もっと読む)

高電圧素子及びその製造方法

【課題】高集積化を実現することができる高電圧素子及びその製造方法を提供すること。

【解決手段】本発明の高電圧素子は、基板内に形成されたドリフト領域と、前記基板内に前記ドリフト領域よりも深く形成された素子分離膜と、前記基板の上に形成されたゲート電極と、該ゲート電極の両側の前記ドリフト領域内に形成されたソース領域及びドレイン領域とを備える。

(もっと読む)

1 - 20 / 103

[ Back to top ]