Fターム[5F033GG03]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930) | 絶縁性基板 (1,777)

Fターム[5F033GG03]の下位に属するFターム

透光性基板 (1,019)

Fターム[5F033GG03]に分類される特許

741 - 758 / 758

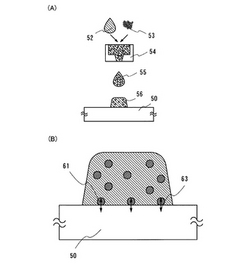

可撓性基板上に作られた電子回路に関する新規な伝導体構造

可撓性基板(21)上に形成された可撓性伝導体。ある実施形態では、かかる基板は半導体基板である。デバイスは、周期的構造のアイランド(14)、及び、前記周期的構造のアイランドに添付した直列の繰り返し構造特性(18)を有する少なくとも1つの伝導体(10)を有する。伝導体の構造特性は、基板が曲がったとき、伝導体を破壊するのではなく伝導体を伸縮させるように適合される。  (もっと読む)

(もっと読む)

薄膜トランジスタの作製方法

【課題】 しかし、薄膜トランジスタを有する表示装置では、同一対象物、例えば同一絶縁膜のエッチング条件を最適化することが難しかった。これは、同一絶縁膜において、エッチングする絶縁膜の膜厚や面積が異なるためである。特に面積の小さなコンタクトホールは、エッチングする量がその他の開口部と異なる。

【解決手段】 上記課題を鑑み本発明は、第1のマスクを用いて、第1の領域の対象物をエッチングして広面積な開口部を形成し、第2のマスクを用いて、第2の領域の前記対象物をエッチングして微細な開口部、つまりコンタクトホールを形成することを特徴とする。

(もっと読む)

導電性電子部品およびその製造方法

導電構造(100)のある実施態様は、第1の導電層(110)および第2の導電層(120)を有する。第2の導電層は、第1の導電層のほぼ全長にわたり、第1の導電層に接触している。第2の導電層は第1の導電層の上方にある。非導電層(130)は、第1の導電層および第2の導電層に接触している。電流は第1の導電層および第2の導電層を通じて伝搬する。  (もっと読む)

(もっと読む)

薄膜トランジスタ、表示装置及びそれらの作製方法、並びにテレビジョン装置

【課題】 本発明は、材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。また、それらの表示装置を構成する配線等の構成物を、密着性よく形成できる技術を提供することも目的とする。

【解決手段】 本発明は、薄膜トランジスタ又は表示装置などを構成する構成物を、それらの被形成物表面を形成する物質のうち、少なくとも一つと同じ物質を添加(混入)して形成することによって、構成物と被形成物との密着性を向上させる。また、構成物上に形成される絶縁層において、構成物表面に生じる凹凸形状を十分に被覆し、かつ絶縁層として信頼性に足るように緻密化できるように、絶縁層を有機材料を含む第1の絶縁層と、無機材料を含む第2の絶縁層とを積層して形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 半導体素子の搭載されたで導電性基板に、導電性基板の表裏面の導通をとる高アスペクト比、小径の貫通孔を、高温プロセスを使用する事なく形成する。

【解決手段】 あらかじめその表面に半導体素子及び該半導体素子と繋がる電気接続部が作りこまれている、半導体基板またはガラス基板からなる導電性基板の所定位置に、少なくとも1つの貫通孔をレーザ等で形成し、該貫通孔の内側表面に蒸着重合法により絶縁層を形成し、該絶縁層の内側表面およびそれと連なる該貫通孔の開孔部周辺部に、無電解メッキ等により導電層を該電気接続部と繋がるように形成する事で、該電気接続部と基板の裏面あるいは側面との導通をとる。

(もっと読む)

半導体装置の作製方法

【課題】 より高精細なパターンの形成が可能な、液滴吐出法を用いた半導体装置の作製方法の提供を課題とする。

【解決手段】 パターンが形成されたモールドを絶縁膜に押し付けた状態で絶縁膜の硬化を行なった後、モールドを取り外すことで、絶縁膜に凹部を形成し、導電材料を有する液滴を吐出することにより、凹部に導電膜を形成し、導電膜を覆うようにゲート絶縁膜を形成し、ゲート絶縁膜上に島状の半導体膜を形成することを特徴とする半導体装置の作製方法。

(もっと読む)

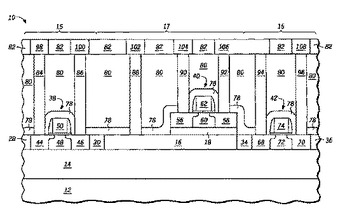

複数の半導体層を備えた半導体デバイス

半導体デバイス構造(10)では、N及びPチャネルトランジスタキャリア移動度を別々に最適化するため、二つの半導体層(16、20)が使用される。これを決定する導電特性は、半導体の材料の種類、結晶面、配向性及び歪みの組み合わせである。シリコンゲルマニウムの半導体材料、圧縮性歪み、(100)の結晶面及び<100>の配向性を特徴とする導電特性の場合、Pチャネルトランジスタ(38)においてホール移動度が向上する。また、結晶面は(111)であってもよく、この場合、配向性は重要ではない。N型伝導に適した基板は、P型伝導に適した(又は最適)基板とは異なる。Nチャネルトランジスタ(40)は、好ましくは、引っ張り歪み、シリコン半導体材料及び(100)面を有する。別の半導体層(16、20)では、N及びPチャネルトランジスタ(38、40)はいずれもキャリア移動度に対し最適化される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置、例えばSRAMのメモリセルのα線によるソフトエラーを低減する。

【解決手段】基板1aをエッチングして第1配線溝HM1を形成し、第1配線溝HM1下の素子分離2(または素子分離溝2および絶縁層1c)をエッチングして第2配線溝HM2を形成し、第1配線溝HM1および第2配線溝HM2の内壁に沿って局所配線16a,16bを形成し、一方の局所配線16aを下部電極ELとして、その下部電極EL上に容量絶縁膜となる窒化シリコン膜17、さらに上部電極EUを形成することにより、容量CA1の面積を増加させて、メモリセルの記憶ノードに相対的に大きな静電容量を付加する。

(もっと読む)

相異なるチャネル領域に相異なるよう調整された内在応力を有するエッチストップ層を形成することによって、相異なる機械的応力を生成するための技術

コンタクトエッチストップ層(116)を設けることによって、異なるトランジスタ型(100N),(100P)のチャネル領域内の応力を効果的に制御することができる。その際、コンタクトエッチストップ層(116)の引張応力部分と圧縮応力部分は、ウェット化学エッチング、プラズマエッチング、イオン注入、プラズマ処理などの十分に確立されたプロセスによって得ることができる。このため、プロセスを著しく複雑にすることなく、トランジスタ(100N),(100P)の性能を大きく改善することができる。  (もっと読む)

(もっと読む)

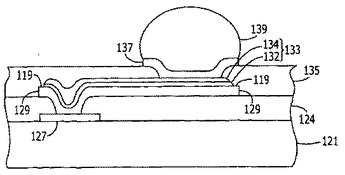

電気コンタクトを対向する両側に有する半導体素子及びその形成方法

半導体(10)はトランジスタのような能動素子を有し、この能動素子はキャパシタ(75,77,79)のような受動素子の直下に位置し、能動素子及び受動素子はビアまたは導電領域(52)及び配線(68,99)によって接続される。ビアまたは導電領域(52)はトランジスタの拡散領域またはソース領域(22)の底面にコンタクトし、更にキャパシタ電極の内の第1電極(75)にコンタクトする。横方向に位置する縦型ビア(32,54,68)及び配線(99)はキャパシタ電極の内の第2電極(79)にコンタクトする。金属配線または導電材料(68)は電源プレーンとして使用することができ、この電源プレーンは、電源プレーンをトランジスタに隣接させるのではなくトランジスタの下に位置するように用いることによって回路面積を節約するように作用する。  (もっと読む)

(もっと読む)

サブミクロンスケールのパターニングの方法およびシステム

ナノパターンの複製方法を開示する。この方法は、基板を特定すること(110)と;基板の表面を液体層で被覆すること(120)と;ナノパターンのネガを規定する複数の凹部を有する成形型を被覆液体層に十分に近接して位置決めして成形型の複数の凹部の少なくとも一部分を液体層で自己充填させること(130)と;液体層を化学変換させて変換膜がナノパターンを実質的に保持しうるようにすること(140)と;成形型を分離すること(150)と;を含む。 (もっと読む)

チタン・タングステンのベース層および関連構造体を含む導電構造体を形成する方法

基板、基板上の導電パッド、および基板上の絶縁層を含む電子デバイスを形成する方法であって、上記絶縁層は導電パッドの一部を露出するバイアホールを有する。詳細には、絶縁層上であり導電パッドの露出部分上に導電構造体を形成できる。導電構造体は、チタン・タングステン(TiW)のベース層と、アルミニウムおよび/または銅のうちの少なくとも1つの導電層とを含みうる。さらに、導電構造体のベース層を、導電層と絶縁層との間に形成できる。関連デバイスについても説明する。

(もっと読む)

(もっと読む)

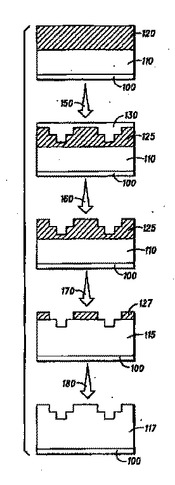

インプリント・リソグラフィによる単一デュアルダマシン製法

インプリント・リソグラフィと共に多段構造を有するテンプレートを用いるデュアルダマシン構造の製造方法の一例は、多段構造を有するリソグラフィ用テンプレート(130)をレジスト層(120)と接触するように配置するステップ(ステップ150)と、テンプレート(130)に圧力を加えることによりレジスト材料(120)がテンプレート(130)のレリーフパターン内に流れ込み、パターン化されたレジスト層(125)が形成されるステップと、そのパターン化されたレジスト層(125)を必要に応じて硬化するステップと、テンプレート(130)をパターン化されたレジスト層(125)から取り外すステップ(ステップ160)と、及びパターニング層(117)にビアやトレンチを作製するためパターン化されたレジスト層(125)をエッチングするステップ(ステップ170,180)とからなる。開示された特徴や仕様は、デュアルダマシン構造や他の多段構造の作製を改良したり、他の方法で最適化したりするため、様々に制御したり、設定したり、適合させたり、他の方法で部分的に変更したりしてもよい。  (もっと読む)

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】半導体素子の発熱に起因する半導体集積回路装置の温度上昇を低減する。

【解決手段】多層配線構造を備えた半導体集積回路装置において、多層配線構造を構成する接続孔及び金属配線層と同じ導電材料からなり、信号伝送用の接続孔及び金属配線層(領域C参照)とは異なる経路で上層側に延びる熱伝導部33,35,37を備えている(領域A,E,F参照)。領域Aにおいて、完全空乏型SOIトランジスタのゲート動作により発生した熱は、コンタクト層19、メタル配線層M1、ビア層21、メタル配線層M2に伝導され、さらに熱伝導部33を介して最上層のメタル配線層M6まで伝導され、絶縁層17の上面側から放熱される。これにより、半導体集積回路装置の温度上昇を低減することができる。

(もっと読む)

配線構造、表示装置および能動素子基板

【課題】 パターニングフリーの能動素子基板の提供。

【解決手段】 能動素子基板は、基板上に形成された能動素子1と、能動素子1上に形成された導電膜2とを有する。導電膜2は、能動素子1から出力された電気信号を有限範囲内に伝達する。

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッドの下層におけるクラックの発生を抑制しつつ、ボンディングパッドの下層を有効活用して装置の小型化を図る。

【解決手段】半導体装置10は、半導体基板11と、外部との電気的接続をとるための接続領域12aを有するボンディングパッド12と、半導体基板11とボンディングパッド12との間に介在する第1層間絶縁層13と、第1層間絶縁層13に埋設されたメタル配線層14とを備える。メタル配線層14は第1層間絶縁層13より硬度の小さい材質からなる。メタル配線層14の少なくとも一部は、積層方向において接続領域12aと重なり、接続領域12aと重なるメタル配線層14の領域には、積層方向に貫通し、メタル配線層14をその層方向において分離している切欠部30a〜30eが形成されているとともに、この切欠部30a〜30eに第1層間絶縁層13の一部が埋め込まれている。

(もっと読む)

多層配線構造部及びその製造方法

【課題】配線容量を低減した多層配線構造部。

【解決手段】下地11と、下地11上に設けられている第1の配線層12と、下地11上に第1の配線層12を被覆するように設けられていて、互いに隣接する第1の配線層12間に凹部22bを有するライナー絶縁膜22と、凹部22bに設けられている埋込み絶縁膜24と、埋込み絶縁膜24を被覆しているキャップ絶縁膜26と、キャップ絶縁膜26上に設けられている第2の配線層14とを具えていて、埋込み絶縁膜24は、ライナー絶縁膜22及びキャップ絶縁膜26よりも低い誘電率を有する絶縁性材料から構成されている。

(もっと読む)

絶縁層及び接続孔の形成方法、配線構造及びその形成方法

【課題】 絶縁層及びヴィア形成において、形成された絶縁層の表面が非常に平滑となり、薄膜素子等を信頼性及び歩留り良く、高い自由度を以って形成でき、さらには微小なヴィア形成が可能である絶縁層及びヴィア(接続孔)の形成方法、及びそれを用いた多層配線基板並びにモジュール基板等の配線構造及びその形成方法を提供する。

【解決手段】 台座20を介してマスク基板21を配置し、この基板21とコア基板1との間に感光性エポキシ樹脂などの感光性絶縁材料3Aを介在させ、これをパターン露光して現像してヴィアホール7を形成する。この現像により、微小なヴィアホール7を形成できると同時に、マスク基板21のコア基板対向面21aによって絶縁材料(従って、絶縁層3)を平坦かつ滑らかな表面に、しかも常に設定された厚みに形成することができる。

(もっと読む)

741 - 758 / 758

[ Back to top ]