Fターム[5F033HH18]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | Ti (2,592)

Fターム[5F033HH18]に分類される特許

2,101 - 2,120 / 2,592

半導体装置及びその作製方法

【課題】 本発明は、シロキサン結合を含む絶縁層を選択的にエッチングする技術について提供することを課題とする。また、本発明は、エッチングの際に生じる不具合に起因した動作不良等の低減された半導体装置を提供することを課題とする。

【解決手段】 本発明の一は、半導体層と導電層との上に設けられ、シロキサン結合を含む絶縁層を、絶縁層の上に設けられた感光性樹脂をマスクとし、臭化水素ガスと酸素ガスとを含む処理用ガスを用いて絶縁層をエッチングする工程を含むことを特徴とする半導体装置の作製方法である。

(もっと読む)

半導体集積回路装置の製造方法

【課題】ダマシン法を用いて形成された銅配線の絶縁破壊耐性(信頼性)を向上する。

【解決手段】シリコン酸化膜39の配線溝40に埋め込むCu配線46a〜46eをCMPを用いた研磨で形成する。それから、CMP後の洗浄工程を経た後に、シリコン酸化膜39およびCu配線46a〜46eの表面を還元性プラズマ(アンモニアプラズマ)で処理する。その後、真空破壊することなく、連続的にキャップ膜(シリコン窒化膜47)を形成する。

(もっと読む)

半導体装置

【課題】クラックの発生等を防止することができ、複数の層間絶縁膜内において、素子として機能する配線等を配設できる領域を広くとることができ、製造コストの削減を図ることができる、半導体装置を提供することを目的とする。

【解決手段】本発明に係わる半導体装置では、誘電率kが2.7未満である低誘電率膜4等を有している。そして、当該低誘電率膜4等において、パッド部47の下方部分には、低誘電率膜4等よりも硬度の硬い材料(たとえば、第一のダミーパターン10等,第二のダミーパターン12等)が形成されている。

(もっと読む)

線路デバイスの製造方法

【課題】ストレスリリーフと接触窓構造の間隔距離の微小化を可能にする線路デバイス構造の製作過程及びその構造を提供する。

【解決手段】基板と、第一金属柱体68と、第二金属柱体と、を備え、第一金属柱体68は、基板上に位置し、第一金属柱体68の最大横寸法Hwを第一金属柱体68の高度Htで割ると4より小さく、かつ第一金属柱体68の高度が20μmから300μmの間であって、第二金属柱体は、基板上に位置し、第二金属柱体の最大横寸法を第二金属柱体の高度で割ると4より小さく、かつ第一金属柱体の中心点から第二金属柱体の中心点までの距離Hbが10μmから250μmの間である。

(もっと読む)

半導体装置の製造方法

【目的】 基板上の膜に対し、膜の膜剥れやスクラッチを防止する半導体装置の製造方法を提供することを目的とする。また、露光装置におけるステージ上での基板のチャックエラーを抑制することを別の目的とする。

【構成】 基板200の表面にCu膜260を形成するめっき工程(S120)と、前記基板200の裏面を研磨する裏面研磨工程(S122)と、前記裏面が研磨された後、前記基板200の表面に形成された前記Cu膜260を研磨する表面研磨工程(S124)と、を備えたことを特徴とする。

(もっと読む)

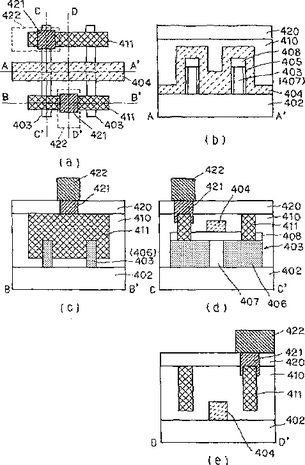

半導体装置およびその作製方法

【課題】液晶表示装置やEL発光装置などの半導体装置において、今後のさらなる高精細化(画素数の増大)、小型化に伴う各表示画素ピッチの微細化、及び画素部を駆動する駆動回路の集積化を進められるように、複数の素子を限られた面積に形成し、素子が占める面積を縮小して集積することを課題とする。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して複雑なゲート電極を形成する。また、マスクを変更するだけで、工程数を増やすことなく、同一基板上に上記マルチゲート構造であるトップゲート型TFTとシングルゲート構造であるトップゲート型TFTを形成することができる。

(もっと読む)

メタル材料用エッチング剤組成物及びそれを用いた半導体デバイスの製造方法

【課題】

半導体デバイス製造のトランジスタ形成工程に用いられるメタル材料を、選択的に、かつ効率よくエッチングするエッチング剤組成物、及びそれを用いた半導体デバイスの製造方法を提供する。

【解決手段】

メタル材料の精密な加工が可能であり、かつ絶縁材料に対する腐食性が少ないという優れた特性をもつエッチング剤組成物であって、フッ素化合物に無機酸もしくは有機酸のいずれかを含有することからなるエッチング剤組成物、及びそれを用いた半導体デバイスの製造方法。

(もっと読む)

ナノ・スケール・チャネルトランジスタのためのブロックコンタクトアーキテクチャ

ナノスケールチャネルデバイスのコンタクトアーキテクチャは、複数の並列半導体本体を有するデバイスのソースまたはドレイン領域に結合されかつその間に延びるコンタクト構造を有する。コンタクト構造は、サブリソグラフィックピッチを有する並列半導体本体と接触することができる。 (もっと読む)

半導体装置およびその製造方法

【課題】 MISFETを有する半導体装置の性能を向上させる。

【解決手段】 半導体基板1のp型ウエル7上にゲート絶縁膜8を介してゲート電極15が形成され、p型ウエル7にはソース・ドレインとしてのn+型半導体領域35が形成されている。ゲート電極15の両側壁上にはオフセットスペーサ23を介してサイドウォールスペーサ33が形成され、サイドウォールスペーサ33の側面34aには凹部34bが形成されている。ゲート電極15上およびn+型半導体領域35上に金属シリサイド膜43a,43bが形成され、金属シリサイド膜43aはゲート電極15の上面上だけでなく、サイドウォールスペーサ33の側面34aうちの凹部34bよりも上部の領域上にも延在している。金属シリサイド膜43bは、n+型半導体領域35の上に形成されている。

(もっと読む)

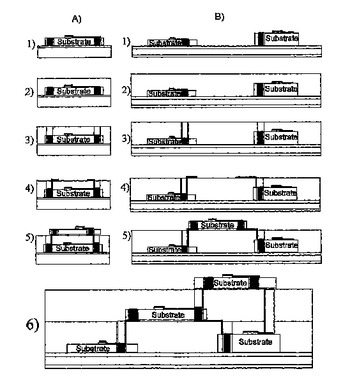

線路デバイスの製造方法

【課題】ストレスリリーフと接触窓構造の間隔距離を微小化できる線路デバイスの製造方法を提供する。

【解決手段】一つの半導体基部30は、半導体基部30上に位置する少なくとも一つの第一金属柱体及び半導体基部30上と第一金属柱体上に位置する一つの第一重合物層46を提供する。第一重合物層46を金属柱体の一つの頂部が露出するまで除去する。一つの第二金属柱体を提供する。電気めっき方式で第一重合物層46上に一つの金属接続線路層を形成させ、金属接続線路層は第一金属柱体及び第二金属柱体と接続する。金属接続線路層の形成ステップの前に、第一重合物層46上に一つのチタン含有金属層を形成させる。

(もっと読む)

応力緩衝カラーを備えるシリコン貫通ビアを形成する方法およびその装置

応力緩衝カラー(250)を有するビア(230)を形成する方法が提供される。応力緩衝カラーは、周囲材料の熱膨脹係数中の不一致に起因する応力を吸収することができる。他の実施例も説明される。 (もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線形成のためのドライエッチングが進行しても、ゲート絶縁膜にチャージダメージを与えることを抑制できる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、ゲート絶縁膜3a,3bを形成する工程と、ゲート配線4a,4bを形成する工程と、絶縁膜8を形成する工程と、接続孔8a,8b,8cを形成する工程と、接続孔8a,8b,8cに導電体9a,9b,9cを埋め込む工程と、絶縁膜8上及び導電体9a,9b,9c上に、導電膜11,12,13を形成する工程と、ドライエッチングを用いて導電膜11,12,13をパターニングすることにより、絶縁膜8上に複数の配線10a,10b,10d、及びダミー配線10cを形成する工程とを具備する。ダミー配線10cと、ダミー配線10cに最も近い配線10bの間隔は、配線10a,10b,10dの相互間隔以下である。

(もっと読む)

電気光学表示装置およびその製造方法

【課題】TFT構造部の製造工程を簡略化するとともに、ソース・ドレイン電極の材質を限定せずとも、TFTチャネル部となる半導体層の膜厚を正確に制御することで、表示ムラを防止した電気光学表示装置を提供する。

【解決手段】活性領域層AR上から、画素電極30の下方の透明絶縁性基板1の上方にかけて延在するようにドレイン電極26が配設されている。ソース電極24およびソース配線25は、その端面が半導体膜6の何れの端面よりも後退した位置となるように配設され、活性領域層AR上のドレイン電極26の端面も、半導体膜6のほぼ平行な関係にある端面よりも後退した位置となるように配設されている。

(もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上部から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在するゲート絶縁膜と、前記半導体凸部に設けられたソース/ドレイン領域とを有するMIS型電界効果トランジスタ、このトランジスタを含む基体上に設けられた層間絶縁膜、及びこの層間絶縁膜に形成された埋め込み導体配線を有し、この埋め込み導体配線は、前記半導体凸部のソース/ドレイン領域と、前記層間絶縁膜下の他の導電部とに接続されていることを特徴とする半導体装置。  (もっと読む)

(もっと読む)

パターンの形成方法及び液滴吐出ヘッド

【課題】 パターン形成において、低コスト化及び形成時間の短縮化を図るとともに、微細パターンの形成を可能としたパターンの形成方法を提供する。

【解決手段】 本発明のパターン形成方法は、基板18上に第1金属膜28を形成する第1金属膜形成工程と、第1金属膜28上に、パターンを形成しない基板18上の位置に対応する第1金属膜28が露出するようにマスクパターン38を形成するマスクパターン形成工程と、マスクパターン38をマスクとして第1金属膜28上に絶縁膜40を形成する絶縁膜形成工程と、マスクパターン38を除去し、メッキ法により、マスクパターン38を除去した第1金属膜28上に絶縁膜40をマスクとして少なくとも第2金属膜42を形成する第2金属膜形成工程と、を有する。

(もっと読む)

膜パターンの形成方法、半導体装置、電気光学装置、及び電子機器

【課題】 バンクに撥液化処理を行う際の、機能膜へのダメージを解消した膜パターンの形成方法と、これによって得られた膜パターンを備えた半導体装置、電気光学装置、及び電子機器を提供する。

【解決手段】 基板Pに設けられたゲート絶縁膜28(機能膜)上に機能液を配置して膜パターンを形成する方法である。基板Pにゲート絶縁膜28を設け、ゲート絶縁膜28上にポリシラザン液、ポリシラン液またはポリシロキサン液のいずれかを塗布し乾燥してバンク膜31を形成する。そして、マスクMを用いてバンク膜31を選択的に露光し、バンク膜31に撥液処理を施す。バンク膜31を現像処理することでゲート絶縁膜28を露出させ、パターン形成領域を区画するバンクを形成する。パターン形成領域に前記機能液を配置し、膜パターンを形成する。少なくとも、バンク膜31に撥液処理を施す工程は、バンク膜31を現像処理しバンクを形成する工程より前の工程で行う。

(もっと読む)

マイクロ反応チップおよびその製造方法

【課題】 CMOS回路のAl合金配線の有無による段差やAl合金残渣による突起の影響を受けることなく、平坦な表面の反応電極を形成して、均一かつ収率の高いDNAの合成や検出等を促すことができるマイクロ反応チップと、その確実な製造方法を提供する。

【解決手段】 CMOS回路の最終保護層6に形成されたコンタクトホール13に接続電極22が形成されてCMOS回路の配線12に接続されるとともに、最終保護層6上には、接続電極22に達する孔部23Bを備えた保護膜23が形成され、さらにこの保護膜23上には、孔部23Bを介して接続電極22に接続される反応電極24が形成される。保護膜23の表面23Aを研磨加工した後に反応電極24を形成する。

(もっと読む)

チップの架橋接続

システムは、第1半導体デバイスと第1電気接続とを有する第1チップ、第2半導体デバイスと第2電気接続とを有する第2チップ、および第3半導体デバイスと第3電気接続とを有する第3チップを有し、第3チップは、第1および第2チップの上面にスタックされ、第1および第2チップのそれぞれの少なくとも一部分を物理的に架橋し、前記第1および第2チップに接続される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】MIM型容量素子において、ヴィアホールのエッチング時に上部電極と下部電極ではコンタクト深さが異なるため、上部電極及び容量誘電膜の突き抜けによるリーク不良が発生する。

【解決手段】基板上に下部電極12a及び上部電極引き出し層12bを同一配線層に形成し、下部電極12a上にのみ容量絶縁膜13を形成し、容量絶縁膜13上から上部電極引き出し層12bを覆う上部電極14を形成し、上部電極14と上部電極引き出し層12bを電気的に接続することにより、MIM型容量素子を形成する。

(もっと読む)

薄膜トランジスタ及び半導体デバイスの作製方法

【課題】液滴吐出法などのマスクレスプロセスを用いて円形薄膜トランジスタを作製することにより、工程の簡略化、作製時間の短縮、及び作製費用の低減を図ると共に、従来よりもその形状が制御された円形薄膜トランジスタの作製方法を提供することを目的とする。

【解決手段】液滴吐出法等のマスクレスプロセスを用いて、基板上に同心円状の薄膜を積層し、円形の電極を有する円形薄膜トランジスタを形成する。また、液滴吐出法等のマスクレスプロセスを用いて、基板上に同心円状の薄膜を積層し、円形の半導体層を有する円形薄膜トランジスタを形成してもよい。

(もっと読む)

2,101 - 2,120 / 2,592

[ Back to top ]