Fターム[5F033HH18]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | Ti (2,592)

Fターム[5F033HH18]に分類される特許

2,021 - 2,040 / 2,592

半導体装置の作製方法

【課題】強度を向上させることにより、信頼性を向上させた半導体装置を提供する。また、強度を向上させることにより、高付加価値化を実現した半導体装置を提供する。

【解決手段】第1の基板上にトランジスタを形成する工程と、トランジスタ上に第1の絶縁層を形成する工程と、第1の絶縁層に設けられた開口部を介して、トランジスタのソース又はドレインに接続された第1の導電層を形成する工程と、第1の絶縁層と第1の導電層上に、第2の基板から分離した第2の絶縁層を形成する工程と、第2の絶縁層上に、異方性導電層とアンテナとして機能する第2の導電層が設けられた第3の基板を配置して、異方性導電層を介して第1の導電層と第2の導電層を電気的に接続させる工程を含む半導体装置の作製方法を提供する。

(もっと読む)

半導体装置およびその作製方法

【課題】基板上に設けられた半導体素子を複数積層させた場合であっても、積層した半導体素子が基板を通して電気的に接続可能となる半導体装置およびその作製方法を提供することを目的とする。

【解決手段】基板の一方の面に選択的に凹部または基板の一方の面から他方の面に貫通する開口部を形成し、基板の一方の面および凹部または開口部を覆うようにトランジスタを有する素子群を形成し、基板を他方の面から薄膜化することによって、凹部または開口部に形成された素子群を露出させることを特徴としている。基板を薄膜化する手段としては、基板の他方の面から研削処理、研磨処理、化学処理によるエッチング等を行うことによって基板を部分的に除去することによって行うことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 容量密度を高めることが可能な、立体構造のMIMキャパシタにおいてMIMキャパシタ直下の配線領域が配線として利用でき、配線層数の増大や、ICチップ面積の増大を防ぐことのできるMIMキャパシタを備えた半導体装置及びその製造方法を提供する。

【解決手段】 下層配線を被覆するように層間絶縁膜301を形成し、層間絶縁膜に対し、下層配線の上面を基準とする層間絶縁膜の膜厚よりも小さな高さの開口部を形成し、開口部を被覆するように上部電極204、容量膜401、下部電極203から構成されるMIMキャパシタを形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線信頼性を向上させるとともに配線の高抵抗化を防ぐ半導体装置の製造方法および半導体装置を提供する。

【解決手段】基板11上に下層側に酸素含有絶縁層21aを有する層間絶縁膜21を形成する。次に、層間絶縁膜21の上層側に配線溝22を形成し、酸素含有絶縁層21aに接続孔23を形成する。次いで、接続孔23の側壁が露出するように配線溝22の内壁を覆う状態で、層間絶縁膜21上に、第1のバリア膜24を形成する。次に、配線溝22と接続孔23の内壁を覆う状態で、CuMn合金膜25を形成する。続いて、配線溝22と接続孔23とを埋め込む状態で、CuMn合金膜25上に銅を含む導電層26を形成する。その後、熱処理を行い、CuMn合金膜25中のMnを拡散させて、酸素含有絶縁層21a中の酸素と反応させることで、接続孔23の側壁に、金属含有酸化物からなる第2のバリア膜27を形成することを特徴とする半導体装置の製造方法および半導体装置である。

(もっと読む)

膜パターンの形成方法、デバイス、電気光学装置、電子機器、及びアクティブマトリクス基板の製造方法

【課題】幅の異なる幾つかの領域を有するパターン形成領域に機能液を配置する場合等において、形成される膜パターン間での膜厚さを無くした該膜パターンの形成方法を提供する。

【解決手段】本発明の膜パターンの形成方法は、基板18上に第1バンク層35と第2バンク層36とを積層形成する工程と、前記第1バンク層35及び第2バンク層36をパターニングすることで、第1のパターン形成領域56と、該第1のパターン形成領域56に連続し、かつ該第1のパターン形成領域56より幅が広い第2のパターン形成領域55とからなるパターン形成領域13を有するバンク34を形成する工程と、を有し、前記第1バンク層35、第2バンク層36の形成材料がいずれもシロキサン結合を主鎖としてなる材料であり、前記第2バンク層の形成材料が、側鎖にフッ素結合を有する材料であることを特徴としている。

(もっと読む)

半導体ウエハ及びその製造方法

【課題】

複数の半導体チップを積層するときの、コンタクト電極を、半導体基板の裏面から加工するための製造方法を提案する。

【解決手段】

半導体基板の裏面から開口部がすり鉢状の貫通孔を形成した後、絶縁膜を形成し、その後、貫通孔の底面のコンタクト部となる部分の絶縁膜を除去し、シード層をスパッタした後、Auメッキとパッド部のパターンニングによりコンタクト電極を形成することを特徴とする。

【効果】

貫通孔の開口部がすり鉢状であるため、フォトリソグラフィー時、孔にレジストが充填されやすく、露光時に孔の底面まで光がまわりやすいため、孔底面の絶縁膜に開口パターンを形成することができる。これにより、裏面と素子面との電気的な接続が可能となる。さらに、半導体基板の裏面からの加工であるため半導体素子がプラズマによる影響を受けず、素子の欠陥が発生しない。

(もっと読む)

配線及びその形成方法と薄膜トランジスタ基板及びその製造方法

【課題】接着性が向上し、伝導性に優れた配線及びその形成方法とこれを用いて形成された薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】 配線は、酸化反応性金属またはシリサイド化反応性金属、及び銀を含む接着層と、前記接着層上に形成される銀導電層と、前記銀導電層上に形成され、前記酸化反応性金属及び前記銀を含んで形成される保護層とを有する。

(もっと読む)

膜パターンの形成方法、デバイス、電気光学装置、電子機器、及びアクティブマトリクス基板の製造方法

【課題】幅の異なる幾つかの領域を有するパターン形成領域に機能液を配置する場合等において、形成される膜パターン間での膜厚さを無くした該膜パターンの形成方法を提供する。

【解決手段】本発明の膜パターンの形成方法は、基板18上に第1バンク層35と第2バンク層36とを積層形成する工程と、前記第1バンク層35及び第2バンク層36をパターニングすることで、第1のパターン形成領域55と、該第1のパターン形成領域55に連続し、かつ該第1のパターン形成領域55より幅が広い第2のパターン形成領域56とからなるパターン形成領域13を有するバンク34を形成する工程と、を有し、前記パターン形成領域13に臨む前記第1バンク層35の側壁35sの接触角が、水を含む機能液に対して50°未満であり、前記第2バンク層36の接触角が前記第1バンク層35の接触角より大きい角度である前記バンク34を設けることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極上にシリサイド膜を有し、従来に比べてより一層の高密度化が可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極62及びLDD層63が形成された半導体基板60の上にシリサイドブロックとなるSiN膜64を形成し、このSiN膜64にゲート電極62に通じる開口部を設ける。この開口部を介してゲート電極66の表面をシリサイド化してシリサイド膜66を形成する。次に、SiO2からなる層間絶縁膜67を形成し、フォトリソグラフィ法により層間絶縁膜67の上面からLDD層63に到達するコンタクトホール67hを形成する。そして、このコンタクトホール67hを介してLDD層63に不純物を高濃度に導入して、ソース/ドレイン層63aを形成する。

(もっと読む)

半導体チップおよびその製造方法、ならびに半導体装置

【課題】歩留まりと信頼性の高い貫通電極を有した半導体チップおよびその製造方法を提供する。

【解決手段】この半導体チップ1は、半導体基板2を含んでいる。半導体基板2の表面には導電層3が形成されている。導電層3の下部には、半導体基板2を厚さ方向に貫通する貫通孔5が形成されている。貫通孔5内には、貫通電極8が設けられている。半導体基板2の表面には、貫通孔5を形成する前に予め、補強構造体4が、貫通孔5を完全に覆い尽くすように、貫通孔5よりも大きい径で配置されている。これにより、導電層3は、常に貫通孔5の反対面において補強構造体4で、支えられることにより、導電層3のクラックが防止される。

(もっと読む)

半導体装置

【課題】 本番チップにPCMを設けても、チップサイズが増大しないようにする。

【解決手段】 製造工程の不良解析用のPCM22は半導体装置21のチップ内に埋め込まれている。PCM22の測定用のパッド12はチップの側面に設けられている。半導体装置21は各層が積層されて構成され、パッド12はその積層構造の最上層のメタルより下層に位置するメタルで形成されている。

(もっと読む)

Cu層及びCu/Ni層用の安定化されたエッチング溶液

本発明は、半導体技術において適切に銅からなるメタライジング層をさらにはCu/Ni層をエッチングすることができる新規の貯蔵安定な溶液に関する。この新規エッチング溶液を用いて、純粋な銅メタライジング、銅ニッケル合金からなる層並びに互いに積層された銅及びニッケル層をエッチングしかつ構造化することができる。前記溶液は、硝酸、過酸化水素、クエン酸及び水を含有する。 (もっと読む)

半導体装置

【課題】低コスト化を図り、強度、信頼性に優れるとともに、高いQ値を得ることが可能な半導体装置を提供する。

【解決手段】一方の面10aの厚み方向の少なくとも一部の領域が除去された除去領域11を有する半導体基板10と、除去領域11に充填された絶縁材料からなる絶縁部12と、該絶縁部12上に複数回周回されて形成された配線21とを備えることを特徴とする。

(もっと読む)

半導体基板への導電性膜の形成方法、半導体装置の製造方法

【課題】半導体基板上の同一層に厚さの異なる領域を有する導電性膜を形成する方法として、各領域の厚さを所定厚さに精度良く制御できる方法を提供する。

【解決手段】半導体基板1上に、下側配線2、層間絶縁膜3、および導電性プラグ4を形成した後、この半導体基板1上の全面に、Ti膜5、TiN膜6、アルミニウム合金膜(第1の導電性膜)7、TiN膜(エッチングストップ層)8、アルミニウム合金膜(第2の導電性膜)9、およびTiN膜10をこの順に形成する。セル領域の上のみを覆うレジストパターンを形成した後、TiN膜(エッチングストップ層)8に至るまでエッチングを行うことにより、周辺回路領域上のTiN膜10とアルミニウム合金膜(第2の導電性膜)9を除去する。これにより、層間絶縁膜3上の導電性膜の厚さが、周辺回路領域よりもセル領域の方が厚くなる。

(もっと読む)

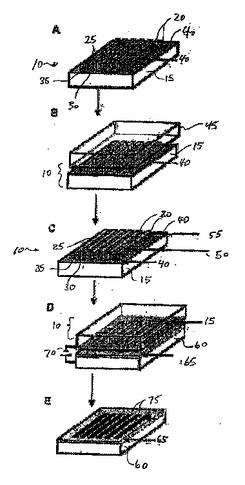

導電性コーディングされた側壁を有するナノ転写印刷スタンプを使用する方法

ナノ転写印刷法の既知の方法は、厚さ10nm未満の金属層(40)でコーティングしたスタンプ(10)を使用して、スタンプ(10)の凸部(25)から第二の表面(45)へ層(40)を転写する。本発明によれば、スタンプ(10)の側壁(35)および凹部(30)の残りの層は、材料(60)の層(65)への電荷印刷(charge print)に使用するか、または化学的測定および生物学的測定における電極として使用することができる。  (もっと読む)

(もっと読む)

薄膜トランジスタ表示板

【課題】本発明は、液晶表示装置のPLSモードで生じ易いオフ画素不良を軽減できる薄膜トランジスタ表示板を提供する。

【解決手段】本発明による薄膜トランジスタ表示板基板は、前記基板上に形成されている複数のゲート線、前記基板上に形成されて透明な導電体で構成される複数の共通電極、前記ゲート線と交差するデータ線、前記ゲート線及び前記データ線と連結されている薄膜トランジスタ、前記薄膜トランジスタと連結されており、前記共通電極と重なっている複数の画素電極を含み、前記画素電極は互いに分離されている第1及び第2副画素電極を含む。これにより共通電極と画素電極の一部が短絡されても画素が暗く表示される画素オフ不良を軽減できる。

(もっと読む)

半導体装置

【課題】銅配線を覆って設けられるバリアメタル膜のバリア性能が向上されており、低比誘電率層間絶縁膜から放出されるガスによりバリアメタル膜が酸化されても、銅配線の信頼性や性能、および品質等が低下するおそれの殆ど無い半導体装置を提供する。

【解決手段】比誘電率が3以下である絶縁膜3が基板1上に少なくとも1層設けられている。少なくとも一部がこの絶縁膜3内に形成されている凹部10の内面を覆って第1のバリアメタル膜6が設けられている。この第1のバリアメタル膜6の表面を覆って凹部10内に第2のバリアメタル膜7が設けられている。この第2のバリアメタル膜7の表面を覆って凹部10内に第3のバリアメタル膜8が設けられている。この第3のバリアメタル膜8の表面を覆って凹部10内にCu膜11が埋め込まれて設けられている。

(もっと読む)

半導体装置

【課題】 埋込銅配線を有する半導体装置の信頼性を向上させる。

【解決手段】 絶縁膜14,15に配線溝を形成し、その配線溝の底面および側面上を含む絶縁膜15上に導電性バリア膜18と銅の主導体膜19を形成し、CMP法により不要な部分を除去して配線20を形成する。そして、主導体膜19上にタングステンからなる金属キャップ膜22を選択成長させてから、配線20を埋込んだ絶縁膜15上に絶縁膜23〜26を形成し、ビア30が金属キャップ膜22を貫通して主導体膜19を露出するようにビア30及び配線溝31を形成し、ビア30の底部で露出した主導体膜19上にタングステンからなる金属キャップ膜32を選択成長させた後に、ビア30および配線溝31の内部を含む絶縁膜26上に導電性バリア膜33と銅の主導体膜34を形成し、CMP法により不要な部分を除去して配線35を形成する。

(もっと読む)

有機薄膜トランジスタ表示パネル及びその製造方法

【課題】有機薄膜トランジスタの特性を良好に維持したまま、製造工程全体の作業時間の短縮を可能にする有機薄膜トランジスタ表示パネル及びその製造方法を提供する。

【解決手段】本発明による有機薄膜トランジスタ表示パネルでは、データ線とドレイン電極とが、ITOまたはIZOを含む第1導電層と、第1導電層より抵抗の低い金属を含む第2導電層とを有し、それぞれの第1導電層で有機半導体に接触している。

(もっと読む)

表面活性化剤を用いる金属含有フィルムの原子層蒸着

表面上に金属含有フィルムを形成させる原子層蒸着法が提供される。これらの方法は、これらの方法の最も広い態様において、(a)表面を表面活性化剤にさらして表面上に表面活性化錯体の蒸着物を形成させる工程と、

b)表面活性化錯体の蒸着物を金属前駆体にさらして表面上に金属錯体の蒸着物を形成させる工程と、

c)蒸着させた金属錯体を還元剤と反応させて、表面上に酸化物を含まない金属含有フィルムを形成させる工程とを含んでなり、ここで、金属はCo、Ni、Pt、Pd、IrおよびWよりなる群から選択される。

(もっと読む)

2,021 - 2,040 / 2,592

[ Back to top ]