Fターム[5F033HH18]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | Ti (2,592)

Fターム[5F033HH18]に分類される特許

1,961 - 1,980 / 2,592

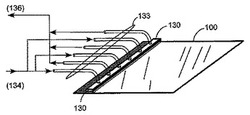

液晶ディスプレイ用のガラス基板上に、パターン形成された導電層を作成するための方法および装置

【解決手段】液晶ディスプレイ(LCD)の一部にされる金属特徴を定めるための方法およびシステムが提供される。この方法は、ガラス基板に対して施され、ガラス基板は、ガラス基板上にまたはガラス基板の層上に定められたブランケット導電性金属層(例えば障壁層)を有する。ブランケット導電性金属層の上には、反転フォトレジストマスクが塗布される。次いで、反転フォトレジストマスクの上に、めっきメニスカスが形成される。めっきメニスカスは、少なくとも電解液およびめっき化学剤を含み、めっきメニスカスは、ブランケット導電性金属層の上の、反転フォトレジストマスクによって覆われていない領域内に金属特徴を形成する。 (もっと読む)

半導体集積回路装置

【課題】 MIM構造の容量素子の、半導体基板上に形成した時に単位面積当たりで得られる容量値(容量密度)を高くする。また、前記MIM構造の容量素子を有する半導体集積回路装置を小型化する。

【解決手段】 半導体基板上に、第1金属膜、第1絶縁膜、第2金属膜、第2絶縁膜、第3金属膜を順次積層してなり、前記第1金属膜と第3金属膜が電気的に接続され、前記第1金属膜、第1絶縁膜、第2金属膜により構成される第1容量と、前記第2金属膜、第2絶縁膜、第3金属膜からなる第2容量が並列に接続されており、前記第2容量の容量として機能する容量真性部が前記第1容量の容量として機能する容量真性部の内側に設けられているMIM構造の容量素子である。

(もっと読む)

半導体装置

【課題】簡便な方法により、タングステン膜とバリアメタル膜との電気的接続を安定させることができるとともに、配線層の成膜性を向上させることができる半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体基板101と、半導体基板101上に形成された開口部102aを有する層間絶縁膜102と、開口部102a内を埋設するタングステン膜(Wプラグ108)と、タングステン膜の表面に形成された、Ti膜以外の第1バリアメタル膜110と、第1バリアメタル膜110上に形成された、Ti含有膜である第2バリアメタル膜111と、第2バリアメタル膜111の表面に形成された金属配線膜116と、を備える。

(もっと読む)

半導体装置及びその製造方法並びに電子装置

【課題】 外部基板へ実装した際に、接続不良を低減できる半導体装置を提供する。

【解決手段】 本発明に係る半導体装置1は、一面に電極を配してなる半導体基板2と、 半導体基板1の一面を覆うように配され、かつ、前記電極が露呈するように開口部を有すると共に、厚さが異なる部分を有する中間層21と、中間層21を覆い、外部基板との接続領域に配された第一導電部6A、6aと、前記開口部を通して前記電極と第一導電部6A、6aとを電気的に接続する第二導電部と、第一導電部6A、6aに接合されるバンプ9A、9aと、を少なくとも備え、第一導電部6A、6aが配された中間層21の厚さに応じて体積の異なるバンプ9A、9aを有する。図1に示す構成例は、第一中間層4に第二中間層5を重ねた厚い中間層21上に配されるバンプ9Aが、第一中間層4のみからなる薄い中間層21上に配されるバンプ9aに比べて、小さな体積を有する場合を示す。

(もっと読む)

配線構造体の形成方法、配線構造体、半導体装置の形成方法、及び表示装置

【課題】表面凹凸が少なく電気抵抗が低い配線構造体の形成方法を提供する。

【解決手段】基体1上に金属層4を形成する第1工程と、金属層4にフラッシュランプから発せられる光を照射してアニールを行う第2工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 信頼性及び歩留りの低下を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】 バイアホール18が形成された半導体基板11と、半導体基板11の表面上に形成された絶縁膜13と、絶縁膜13、バイアホール18の内壁及び半導体基板11の表面上に形成されたスパッタ金属層14と、絶縁膜13上のスパッタ金属層14を除くスパッタ金属層14上に形成された第1のメッキ層15と、第1のメッキ層15及びスパッタ金属層14上に形成された第2のメッキ層16とを備える。

(もっと読む)

半導体装置の製造方法

【課題】上部の径が大きく、下部の径が小さなコンタクトを形成する際に行う絶縁膜の異方性ドライエッチングを、フォトレジスト膜との選択性が高く且つエッチストップを生ずることなくエッチングする、半導体装置の製造方法を提供する。

【解決手段】カーボンリッチなガスとO2及び希ガスとを含むエッチングガスを用い、層間絶縁膜20の途中までを選択的にエッチングして上部の大径コンタクト孔を形成する第1の異方性エッチング工程と、水素ガスを含むガスを用いて上部コンタクト孔にデポジション膜を堆積するデポジション工程と、O2を含むガスを用いコンタクト孔の底部のデポジション膜を選択的に除去する第2の異方性エッチング工程と、第1の異方性エッチング工程と同じガスを用い、層間絶縁膜20の残りの部分をエッチングして、下部の小径コンタクト孔を形成する第3の異方性エッチング工程とを有する。

(もっと読む)

パターニング方法および薄膜トランジスタの製造方法

【課題】 フォトマスクの枚数を低減して製造コストの低減が可能なパターニング方法を提供する。

【解決手段】 (a)電極層20およびオーミック接続層30を順に積層形成する工程と、(b)接続層30の表面の所定位置にエッチングマスク層40を形成する工程と、(c)接続層30のa−Si材料のエッチングレートが、電極層20のMo材料およびエッチングマスク層40のレジスト材料のエッチングレートより大きくなる第1エッチングと、(d)電極層20のMo材料およびエッチングマスク層40のレジスト材料のエッチングレートが、接続層30のa−Si材料のエッチングレートより大きくなる第2エッチングとを、繰り返し実施することにより、接続層30および電極層20をパターニングするとともに、電極層20の側面を傾斜面とする工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ウエハレベルCSPにより形成される再配線部の剥離を防止し、微細配線の形成を可能とした半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、少なくとも一面に電極が設けられた基板と、該基板の一面を被覆する絶縁樹脂層11と、該絶縁樹脂層11を被覆し、前記電極と電気的に接続されたライン状の配線部15とを備えている。前記配線部15は、シード部13とその上に配された導電部14とからなる積層体を構成しており、該積層体の長手方向の側面下部のアンダーカット部には少なくとも絶縁性の補強部材19が埋設されている。

(もっと読む)

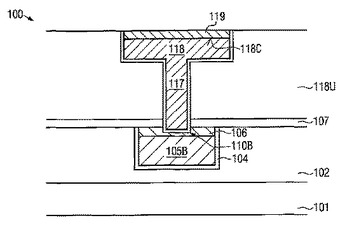

導電性キャッピング層を含む銅ベースのメタライゼーション層を形成する技術

金属ベースの相互接続線に対して導電性キャッピング層(106)を設けることで、エレクトロマイグレーションに対するパフォーマンスを強化することができる。さらに、銅ベースの材料などの下方の金属(105b)を露出せずにビア開口部(110)をキャッピング層(106)に確実にエッチングし、これによりエレクトロマイグレーションパフォーマンスを具体的には銅線とビアの間の遷移において強化することができる。  (もっと読む)

(もっと読む)

フリップチップ半導体デバイス用はんだバンプ構造およびその製造方法

【課題】フリップチップ技術における冶金上の問題および機械的安定性の問題の両方に対処するはんだバンプ構造を提供する。

【解決手段】半導体基板の上に配置された相互接続層を備える半導体デバイス100において、相互接続層115の上に不活性化層122が配置され、不活性化層122中にはんだバンプ128の支持開口125が形成されている。導体材料を含む複数の支持ピラー124がはんだバンプ128の支持開口125内に配置される。

(もっと読む)

有機絶縁膜とその作製方法,及び有機絶縁膜を用いた半導体装置

【課題】 半導体装置の構築に用いられる有機絶縁膜として、低誘電率でCuとの高い密着性を示す有機絶縁膜を提供する。

【解決手段】炭素の三重結合を有する有機シランを原料ガスとして用いて作られた有機絶縁膜を提案する。

(もっと読む)

アクティブマトリクス基板の製造方法、その製造方法により製造されたアクティブマトリクス基板を備えた表示装置

【課題】アクティブマトリクス基板を製造する際に必要なフォトマスクの枚数を従来よりも減らすと共に、低消費電力駆動を実現する。

【解決手段】まず、第1のフォトマスクを用いて、ゲート線1、ゲート電極1a及びソース線下層部3aを形成する。次いで、第2のフォトマスク11を用いてレジスト層12を形成する。続いて、レジスト層12の第1開口部12aを介してn+アモルファスシリコン膜、真性アモルファスシリコン膜及びゲート絶縁膜4をエッチングする。その後、レジスト層12の第2開口部12bを介してn+アモルファスシリコン膜をエッチングして、ソース領域5b及びドレイン領域5cをパターニングして半導体層5を形成する。さらに、第3のフォトマスクを用いて、コンタクトホール6a、6b及び6cを形成する。最後に、第4のフォトマスクを用いて画素電極8a及びソース線3を形成する。

(もっと読む)

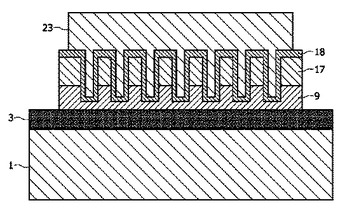

改良された接触パッドを有する半導体デバイスとその製造方法

半導体デバイスおよびその製造方法が開示される。このデバイスは、1以上の導電性ゲート(11)を具えた活性半導体領域(1A)と、前記活性半導体領域(1A)の周辺に位置し主としてフィールド酸化領域(3)よりなるコンタクト領域(1B)とを具える。周辺コンタクト領域(1B)上、および、少なくとも一部の活性半導体領域(1A)上に、導電性ゲート(11)の間にコンタクト窓(19a)が形成された絶縁層(17)が積層される。絶縁層(17)上に積層された金属コンタクトパッド(23)が、前記コンタクト領域(1B)に設けられる。この金属コンタクトパッド(23)は、導電性のパターンを介して、絶縁層(17)の下に埋設されているコンタクトストリップ(15)に接触し、この導電性のパターンは、コンタクト窓(19b)充填物の複数個で構成されており、コンタクトパッド(23)の実質的な領域を横切って延びている。このパターンは平行な一連のトレンチに充填されたもので構成されているのが好ましい。  (もっと読む)

(もっと読む)

導体トラック配列およびその製造方法

【課題】結合容量の低下、機械的、電気的特性が向上した導体トラック配列及び製造方法の提供。

【解決手段】基材1、2と、少なくとも2つの導体トラック4と、空洞6と、導体トラック4を覆い、空洞6を塞ぐレジスト層5とを含む、導体トラック配列に関する。導体トラック4の幅B1よりも小さい幅B2のキャリアトラックTBを形成することにより、結合容量と信号遅延を低減するためのエアギャップが、導体トラック4の下にその側面に沿ってセルフアライン技術により形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】 不揮発性メモリ素子のデトラップ・リテンション特性の劣化を防止することができる技術を提供する。

【解決手段】 プラグ16を形成した絶縁膜14上にシリコンリッチな酸化膜よりなる層間絶縁膜17およびTEOS膜よりなる層間絶縁膜18を形成する。そして、層間絶縁膜17および層間絶縁膜18を貫通する溝19を設け、この溝19内へ埋め込むように配線20aを形成する。すなわち、第1配線層を層間絶縁膜17および層間絶縁膜18に埋め込んだ埋め込み配線とする。さらに、第1配線層を構成する配線20a〜20cと同層の層間絶縁膜17として水や水素などの不純物を捕獲する性質を有するシリコンリッチな酸化膜とする。

(もっと読む)

可撓性表示装置用表示板の製造方法

【課題】

本発明は、プラスチック基板が熱によって変形することを防止して正確な薄膜パターンを形成する方法を提供する。

【解決手段】

本発明による表示板を製造する方法は、可撓性基板を形成する段階、前記基板の上にゲート線を形成する段階、前記基板の上にゲート絶縁膜を積層する段階、前記ゲート絶縁膜の上に半導体層を形成する段階、前記半導体層の上にデータ線及びドレーン電極を形成する段階、そして前記ドレーン電極と電気的に連結されている画素電極を形成する段階を含み、前記ゲート線を形成する段階、ゲート絶縁膜を積層する段階、半導体層を形成する段階、ソース電極を含むデータ線及びドレーン電極を形成する段階、そして画素電極を形成する段階のうち、少なくとも一つは温度80℃乃至150℃及び1×10-6乃至9×10-6Torrの真空度でスパッタリングする段階を含む。

(もっと読む)

配線基板のメッキ膜形成方法

【課題】絶縁層に形成された高アスペクト比の溝やビア孔に電気銅メッキを行うとき、メッキ層中でのボイド(空孔)発生が抑制された配線層やビアの形成を可能とする。

【解決手段】溝やビア孔の底面部に、電気メッキを促進する添加剤を含む膜を選択的に形成してから、電気銅メッキを行う。この底面部のメッキ促進添加剤含有膜は、メッキ促進添加剤を含む溶液に、メッキ形成用の開口基板を浸漬しつつ脱気して開口部内の気泡を除去した後、スピン・リンス法と乾燥処理を行って形成する。

(もっと読む)

有機絶縁膜及びその製造方法及び有機絶縁膜を用いた半導体装置及びその製造方法

【課題】現在、一般的に検討されているSiCやSiCNは比誘電率が4.5から5程度、SiOCは2.8から3.0程度である。デバイスの縮小化により、配線サイズと配線間隔の微細化が更に進むと、比誘電率の更なる低減が求められている。また、SiOCとSiCN及び、SiCとのエッチング選択比がちいさいために、エッチングストッパ膜として、SiCN及びSiCを用いた場合、金属配線層の表面が、フォトレジストを除去する際に酸化し、接続抵抗が高くなるという問題がある。

【解決手段】少なくともC/Si比が5以上で、且つ、分子量が100以上の有機シランを原料として形成された、SiOCH、SiCNH及び、SiCHからなる有機絶縁膜、及び、該有機絶縁膜を用いた半導体装置、特に、溝構造を有する半導体装置に関するものである。

(もっと読む)

トランジスタ、並びにそれを用いた表示装置、電子機器、及び半導体装置

【課題】コンタクト抵抗の低いトランジスタを提供する。

【解決手段】P型又はN型を付与する不純物元素を含む半導体膜と、その上に形成された絶縁膜と、少なくとも前記絶縁膜に形成されたコンタクトホールを介して前記半導体膜と電気的に接続された電極又は配線とを有し、前記半導体膜は、所定の深さよりも深い領域に含まれる前記不純物元素の濃度が第1の範囲(1×1020/cm3以下)であり、且つ前記所定の深さより浅い領域に含まれる前記不純物元素の濃度が第2の範囲(1×1020/cm3を超える)であり、前記半導体膜の、前記電極又は配線と接する部分よりも深い領域は、前記不純物元素の濃度が前記第1の範囲である。

(もっと読む)

1,961 - 1,980 / 2,592

[ Back to top ]