Fターム[5F033HH18]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | Ti (2,592)

Fターム[5F033HH18]に分類される特許

1,941 - 1,960 / 2,592

半導体装置及びその製造方法

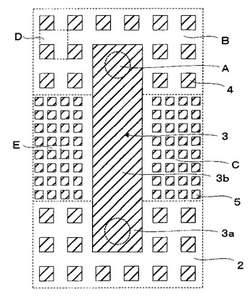

【課題】初期電気特性の向上及びストレスマイグレーション信頼性の向上を両立させた半導体装置及びそのような半導体装置を製造することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板上に形成された層間絶縁膜2と、層間絶縁膜2上に形成された層間絶縁膜と、層間絶縁膜2内に形成され、プラグ接続部3aを有する配線3と、層間絶縁膜内に形成され、プラグ接続部3aに接続されたビアプラグと、層間絶縁膜2内かつプラグ接続部3aの近傍に形成された複数の第1のダミー配線4と、層間絶縁膜2内かつプラグ接続部3aを除く配線3の部分の近傍に形成され、第1のダミー配線4より小さい幅及び第1のダミー配線4より大きい1つのダミー配線の単位当たりのパターン被覆率の少なくともいずれかを有する複数の第2のダミー配線5とを備えている。

(もっと読む)

化合物半導体スイッチ回路装置

【課題】基板を貫通するバイアホールとその内壁の縦型金属層によって、基板の第1主面のスイッチング素子と、第2主面の電極パッドを接続したスイッチMMICにおいて、隣接する縦型金属層に異なる高周波信号が伝搬する場合、基板に伸びる空乏層によって、縦型金属層間に高周波信号が漏れる問題があった。

【解決手段】異なる高周波信号が印加される縦型金属層間に縦型n+型領域を設ける。これにより一方の縦型金属層から伸びる空乏層が他方に到達することを防止し、高周波信号の漏れを抑制する。また制御抵抗の一部に、縦型n+型領域による縦型抵抗を接続することにより、制御抵抗のチップ上の占有面積を小さくできる。

(もっと読む)

パターン形成方法、電子デバイス、及び電子機器

【課題】 より緻密でかつ密着性の良い拡散防止層を形成し、拡散防止層を構成する金属元素が他の層に拡散することを防止したパターン形成方法、電子デバイス、及び電子機器を提供する。

【解決手段】 本発明のパターン形成方法は、基板P上に隔壁30を形成する隔壁形成工程と、隔壁30に囲まれたパターン形成領域30aに導電層80を形成する導電層形成工程と、導電層80上にめっき核26を配置するめっき核配置工程と、導電層80上に、無電解めっき法によりめっき核26を触媒として拡散防止層82を形成する拡散防止層形成工程と、を有する。

(もっと読む)

特徴画成部を形成する方法

【課題】 基板の表面上に特徴画成部を形成する改良された方法を提供する。

【解決手段】 基板の表面にネガティブマスク材料を堆積し、そのネガティブマスク材料を基板表面へとエッチングしてネガティブマスク特徴画成部を形成し、ネガティブマスク特徴画成部に耐エッチング材料を堆積し、その耐エッチング材料を研磨してネガティブマスク材料を露出させ、ネガティブマスク材料をエッチングして耐エッチング材料に特徴画成部を形成することにより、基板を処理する方法が提供される。

(もっと読む)

めっき方法

【課題】工程が容易で、厚膜を高速で形成することができ、且つムラなく、所望の領域に選択的にめっき層を形成することができるめっき方法を提供する。

【解決手段】基材の少なくとも一部に、表面に活性化された硫黄が存在する被めっき層を設け、この基材に無電解めっき処理を施すことにより前記被めっき層上に選択的にめっき層を形成することを特徴とするめっき方法。

(もっと読む)

配線基板、表示装置及び配線基板の製造方法

【課題】

導電層の損傷を防ぐことができるを配線基板とその製造方法並びに表示装置を提供すること。

【解決手段】

本発明の一態様にかかる配線基板は、ガラス基板10と、ガラス基板10上に設けられた庇状のソース配線と、ソース配線2を覆うように設けられた層間絶縁膜8と、層間絶縁膜8の上に設けられ、ソース配線2の庇状の箇所の上に配置された画素電極6と、前記第1の導電層の庇状の部分に対応する箇所に設けられたテーパー状の塗布絶縁膜21とを備えるものである。

(もっと読む)

取付基板上にはんだ接点を形成する方法

マイクロ電子アセンブリの製作方法が提供される。第1の厚さを有する半導体基板(20)が、低温接着剤で支持基板(28)に装着される。半導体基板は第1の厚さから第2の厚さまで薄化される。半導体基板上に少なくとも1つの接点構造(50)が形成され、少なくとも1つの接点構造をリフローするために少なくとも1つの接点構造に高エネルギー電磁放射線(56)が向けられる。  (もっと読む)

(もっと読む)

液晶表示装置の作製方法

【課題】 液晶表示装置の作製工程におけるプラズマ工程による問題、ゲイト電極等におけるヒロック等の問題、液晶パネルの取り出し部におけるコンタクト不良の問題のうち、少なくとも一つを解決する。

【解決手段】 本発明に係る、液晶パネル内に薄膜トランジスタを有する液晶表示装置の作製方法は、Sc、Y、ランタノイド及びアクチノイドから選ばれた一種又は複数種類の元素が含まれたアルミニウム膜を有するゲイト電極を形成し、前記ゲイト電極に電気的に接続される、パルス電流が放電しやすい形状を有する第1の配線を形成し、前記薄膜トランジスタの不純物領域に接続される第2の配線を形成し、前記第2の配線から延在した前記液晶パネルの取り出し部に、透明導電膜を形成することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 多層配線構造を含む半導体装置のマイグレーション耐性を高めて歩留まりを向上させる。

【解決手段】 半導体装置100は、半導体基板(不図示)上の第1の層間絶縁膜106中に設けられた第1の配線112と、第1の配線112上に、第1の配線112に接続して設けられたビア128と、第1の配線112の上部において、ビア128の底部との接続箇所に選択的に形成され、第1の配線112を構成する主成分の金属と当該金属と異なる異種元素とを含む異種元素含有導電膜114とを含む。

(もっと読む)

ウエハレベルチップスケールパッケージのための再配線層およびその製造方法

ある実施形態においては、ウエハレベルチップスケール(WLCS)パッケージ(300)において回路パターン(305)を有する集積回路デバイス(IC)をパッケージするための方法である。この方法は、金属層を第1誘電層(315)上に堆積させ(ステップ5,10,15)、ボンドパッド開口(310)およびバンプパッド開口(330)に充填させ(ステップ20)、金属層(360)は頂部側層(340)および底部側層(360)を備えるものとする。金属層(360)において、ボンドパッド開口または接続部(310)およびバンプパッド開口または接続部(330)は、ボンドパッド開口(310)およびバンプパッド開口(330)以外の区域における頂部側金属層を除去し、ボンドパッド接続部またはバンプパッド接続部がない区域における底部側金属層(360)を残すことステップ(30)によって画定する(ステップ25,30)。底部側金属層に、接続配線をボンドパッドおよびバンプパッド間に画定する(ステップ35、40)。第2有機誘電層(325)をシリコン基板(305)上に堆積させ(ステップ45)、回路パターンを覆う。第2有機誘電層をバンプパッド接続部から除去し(ステップ50)、バンプパッド(330)を露出させるものとする。  (もっと読む)

(もっと読む)

アモルファス膜の成膜方法、このアモルファス膜を備える半導体装置、及び半導体装置の製造方法

【課題】Ti及びAlを含有するほかに、Nを任意成分として含むことがあるアモルファス膜を成膜する方法を提供する。

【解決手段】 Ti及びAlを含むほかに任意成分としてNを含むことがあるアモルファス膜であって、電気抵抗率が、6×102Ω・cm以下の当該アモルファス膜を、スパッタリングターゲットとしてTiAl合金を用い、下記のスパッタ条件で基板上に成膜する。(1)DCパワーは、1kW以上かつ3kW以下である、(2)成膜室内の気圧は、6mTorr以上かつ12mTorr以下である、(3)基板温度は、100℃以上かつ300℃以下である、及び(4)N2ガスとArガスとの混合スパッタガス中におけるN2ガスの体積比率が0%以上かつ70%以下である。

(もっと読む)

チタン/アルミニウム合金を用いた集積回路金属被着膜

【課題】シリコン層における構造的な欠陥を不活性化し、低接触抵抗である金属被着膜、その製造方法、及び金属被着膜を含む集積回路を提供する。

【解決手段】集積回路上に、電気的配線などのために形成される金属被着膜構造は、集積回路の最上層の上に堆積されるチタン層32と、チタン層上に堆積されるアルミニウム層34とを有する。これらのチタン層及びアルミニウム層は、加熱等により少なくとも部分的に合金化される。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】薄膜トランジスタ表示板の製造工程を簡素化する製造方法を提供する。

【解決手段】基板110上にゲート電極を含むゲート線を形成する段階、ゲート線110上にゲート絶縁膜140を形成する段階、ゲート絶縁膜140上に半導体層150、160を形成する段階、半導体層150、160上にオーミックコンタクト部161を形成する段階、オーミックコンタクト部161上にソース電極173を含むデータ線171及びドレイン電極175を形成する段階、保護膜180を蒸着する段階、保護膜180上に感光膜を成膜して露光現像し、第1エッチングマスクとし、前記ゲート絶縁膜140及び保護膜180をエッチングしてドレイン電極175の一部と基板110の一部を露出させる段階、選択的蒸着法を利用してエッチングマスクが存在しない部分にドレイン電極175と接触する画素電極191を形成する段階、感光膜を除去する段階を含む。これによって、表示板の製造時間、製造費用が短縮されて、製品の生産性が向上する。

(もっと読む)

半導体装置およびその製造方法

【課題】ボンディング衝撃による不具合を改善するとともに、フェールセーフ的な構造とすることにより、能動回路上ボンディングパッドへ直接ボンディングワイヤを接続できる半導体装置およびその製造方法を提供する。

【解決手段】第1の配線2で結線され層間絶縁層3で被覆した能動回路1にあって、前記能動回路1が機能するよう第1の接続孔4を介して接続された第2の配線5と平面構造において複数の開口を持つ衝撃吸収梁6がボンディング接続領域に設け保護膜7で被覆し、第2接続孔8を介して前記能動回路1と電気的に接続された厚い電極9を衝撃吸収梁6上に位置するよう設け、厚い電極9へボンディング接続を行うために、衝撃吸収梁6の上方において、保護樹脂層10が開口されてなる半導体装置とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 異種の金属膜の積層構造からなる導電膜に対するボンディングパッドの保護膜の開口を保護膜の減損を生じることなく形成し、かつダイシング工程等水溶液に浸される工程において金属膜の溶解を回避するボンディングパッドを提供する。

【解決手段】 アルミ膜とアルミ膜上に堆積されたTi,TiN等の反射防止膜を含む導電膜の上に堆積した保護膜と前記反射防止膜を除去して前記アルミ膜を露出させたボンディングパッド等の保護膜開口を有し、前記保護膜の除去領域が、前記反射防止膜の除去領域の内側となるように、前記反射防止膜を除去するエッチング工程が、前記保護膜の堆積前に行われる。

(もっと読む)

電気光学装置、及び、その製造方法

【課題】 ゲート電極の膜厚を厚く形成することなく、ゲート電極の十分な遮光性と低抵抗化とを両立することができる電気光学装置を提供する。

【解決手段】 多結晶シリコン層5aと、多結晶シリコン層5aに積層する高融点金属の硅化物層5bと、硅化物層5bに積層する高融点金属層5cとを具備する多層構造の薄膜でTFT30のゲート電極3aを形成することにより、ゲート電極3aの膜厚を厚く形成することなく、十分な遮光性と低抵抗化とを両立する。すなわち、多結晶シリコン層5aの上層に積層された高融点金属の硅化物層5b及び高融点金属層5cを積層によって、ゲート電極3aの低抵抗化が実現され、同時に、硅化物層5bの上層に積層されたシリコン成分を含まない高融点金属層5cによって、TFT基板10にアニール処理が行われた場合等にも、薄い膜厚でゲート電極3aの遮光性が十分に確保される。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の信頼性を高める。

【解決手段】 本発明の半導体装置の製造方法は、基板上に、多孔質構造からなる絶縁膜を形成する工程(S102)と、絶縁膜に配線形成用の凹部を形成する工程(S106)と、絶縁膜上全面に、凹部内を埋め込むように金属層を形成する工程(S108)と、凹部外部の余剰金属層を除去して配線を形成する工程(S110)と、絶縁膜を改質して、当該絶縁膜の表面に改質層を形成する工程(S112)と、改質層を形成する工程の後に、めっき液を用いて配線上に選択的に金属膜を形成する工程(S114)とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】製造プロセスにおけるプラズマ電流により破壊されることを防止でき、且つダイオードの耐圧が上昇してしまうことを回避した半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置10は、支持基板であるシリコン基板101aと、シリコン基板101a上の酸化膜101bと、酸化膜101b上のシリコン薄膜101cとを有するSOI基板101を用い、これのシリコン薄膜101c上に形成された入力端子IN(第2上層配線134)と、シリコン薄膜101c上に形成されたVss端子Tvss(第1上層配線139)と、シリコン薄膜101cに形成され、入力端子INとVss端子Tvssとに接続された半導体素子(例えばインバータ11)と、シリコン薄膜101cに形成され、Vss端子Tvssから入力端子INへ順方向に接続された保護ダイオード12とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】NOR型のメモリセルに形成するワード線の抵抗を低減する。

【解決手段】シリコン基板1は、STI2により活性領域3が分離形成される。活性領域3を直交するようにゲート電極4が所定間隔で形成される。ワード線としてのゲート電極4は、コントロールゲート電極としての多結晶シリコン膜、WSi膜が積層され、その上の上面には、シリコン窒化膜17が形成されるが、これには開口部が形成され、タングステンなどの導体が溝配線5として埋め込まれる。この構成により、微細化が進んでも、ワード線の高抵抗化を抑制できる。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、液晶表示装置およびそれらの製造方法

【課題】パッシベーションおよびゲート絶縁膜のエッチング時の形状制御を可能とし、導電層の段切れを防止可能とし、品質を向上させた薄膜トランジスタ、これを用いた液晶表示装置およびその製造方法を提供する。

【解決手段】 絶縁基板1上にゲート層2、ゲート絶縁膜3、半導体層4、ドレイン層5、パッシベーション層60を設け、かつ前記パッシベーション層60上に配置された導電層7がコンタクトホールを介して前記ゲート層2若しくは前記ドレイン層5と接続される薄膜トランジスタにおいて、前記パッシベーション層60が、表面側を高速エッチングレート層62、基板側を低速エッチングレート層61の2層以上で形成され、かつ前記高速エッチングレート層62の膜厚を前記導電層7の膜厚以下とする。

(もっと読む)

1,941 - 1,960 / 2,592

[ Back to top ]