Fターム[5F033HH18]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | Ti (2,592)

Fターム[5F033HH18]に分類される特許

1,981 - 2,000 / 2,592

半導体装置およびその製造方法

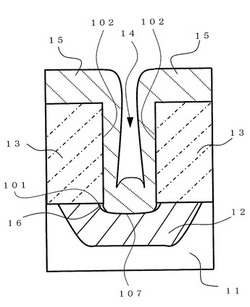

【課題】従来の半導体装置は、コンタクトホールの底部に段差部があり、これにより、コンタクトホール内で配線金属が分断してしまうという問題があった。

【解決手段】本発明の半導体装置は、コンタクトホールの底部にもっとも近い部分の層間膜の開口径より半導体層の開口径が大きく、その開口径の差で生じる層間膜と半導体層との間の段差部を絶縁膜で埋める構成を有している。このような構成によって、コンタクトホールの内壁の縦端面と絶縁膜の表面とが段差のない連続したなめらかな曲面を形成し、コンタクトホール内での配線金属の分断を防止する。

(もっと読む)

半導体装置の製造方法

【課題】 サイドウォール幅の減少を抑制し、ゲート電極が微細化された場合であっても接合リーク電流に起因する製造歩留まりの低下を回避することができる半導体装置の製造方法を提供する。

【解決手段】 ゲート電極3上にスペーサパターン13を形成し、サイドウォール6形成後にスペーサパターン13を除去する。当該手法により、ゲート電極3の高さより高い、もしくは同等の高さのサイドウォール6を形成した後、コンタクトホール21を形成する。これにより、ストッパ膜7を異方性エッチングする際にサイドウォール6の幅が減少することを抑制し、エクステンション領域が露出することにより生じる接合リーク電流に起因する半導体装置の歩留まり低下を抑制することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 デカップリングキャパシタを備えた高周波用の半導体装置において、実装面積をより一層小さくするとともに、配線の長さを可及的に短くして、高周波信号に対する伝送特性を向上させる。

【解決手段】 シリコン基板1上に設けられた絶縁膜3上にグラウンド層5をシリコン基板1上の接続パッド2bに接続させて設け、その上に設けられた保護膜7の開口部9内にデカップリングキャパシタ用の誘電体膜11をグラウンド層5の一部からなる下部電極に接続させて設け、誘電体膜11を含む保護膜7上に高周波信号用の第1の上層配線12をシリコン基板1上の接続パッド2aに接続させて設け、誘電体膜11上における第1の上層配線12の途中に上部電極15を設けることにより、電気的接続配線が主としてシリコン基板1の厚さ方向となり、これにより、実装面積をより一層小さくすることができ、且つ、配線の長さを可及的に短くすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 Cu拡散性が良好で、耐熱性、電気特性、特に誘電率、接着性等に優れた多層配線構造、およびこれを具備した、電気特性に優れる半導体装置を提供する事を目的としてなされたものである。

【解決手段】半導体基板上に形成された絶縁層を有し、前記絶縁層にこれを貫通して埋め込まれた銅および銅を含む合金からなる配線層を備え、少なくとも配線層の上部に配線層を構成する銅および銅を含む合金の拡散防止能を有する窒素含有層を有し、さらにその上に、配線層を構成する銅および銅を含む合金の拡散防止能を有する有機絶縁材料で構成される層を有することを特徴とする半導体装置。

(もっと読む)

半導体素子とその製造方法及びそれを備えたワイヤボンディング・チップサイズ・パッケージ

【課題】短絡等の不具合が生じる虞がなく、配線自由度を容易に増大させることができ、配線の変更を容易かつ短時間で行うことができる半導体素子とその製造方法及びそれを備えたワイヤボンディング・チップサイズ・パッケージ(WBCSP)を提供する。

【解決手段】本発明のWBCSPは、シリコン基板上に配線用パッド32及びバンプ用パッドが形成され、バンプ用パッド上にはポストを介してバンプ電極36が形成され、このシリコン基板上には銅再配線層37が、この銅再配線層37の上方にはボンディングワイヤ38がそれぞれ配設され、この銅再配線層37とボンディングワイヤ38は1つのバンプ電極36に接続され、1つのパッド32と2つのバンプ電極36はそれぞれボンディングワイヤ38により接続されている。

(もっと読む)

ドライエッチング方法

【課題】 ハードマスクで形成されたアルミニウム(Al)を含有する金属膜をプラズマエッチングする場合において、サイドエッチングを抑制し異方性形状を得ることができるエッチング方法を提供する。

【解決手段】 エッチングガスに、三塩化ホウ素(BCl3)、塩素(Cl2)、メタン(CH4)、エチレン(C2H4)、アルゴン(Ar)の混合ガス、もしくは三塩化ホウ素(BCl3)、塩素(Cl2)、メタン(CH4)、アセチレン(C2H2)、アルゴン(Ar)の混合ガスを用いることにより、サイドエッチング無く異方性形状、低パーティクルを提供する。

(もっと読む)

微細構造の製造方法

【課題】微細パターンを歩留まりよくエッチングできる微細構造の製造方法を提供する。

【解決手段】製造方法は、(a)被エッチング膜の上に、下層ハードマスク膜、上層ハードマスク膜を積層したエッチング対象物を準備し、(b)エッチング対象物の上にレジストパターンを形成し、(c)レジストパターンをマスクとして、上層ハードマスク膜をエッチングして上層ハードマスクを形成し、(d)工程(c)の後、レジストパターンを除去し、(e)工程(d)の後、上層ハードマスクをエッチングして細くし、(f)工程(e)の後、細くした上層ハードマスクをマスクとして下層ハードマスク膜をエッチングして下層ハードマスクを形成し、(g)上層ハードマスク、下層ハードマスクをマスクとして、被エッチング膜をエッチングするにあたり、上層ハードマスク膜は下層ハードマスク膜よりもレジストパターンをマスクとしたエッチングが容易な膜を用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】銅配線を用いて配線を行う半導体装置において、接続孔のバリアメタル層の除去の際に、上層配線溝におけるバリアメタル層の除去による層間絶縁膜への銅の拡散を抑えることができる半導体装置を得ること。

【解決手段】所定の形状にパターン形成された銅配線36を有する第1の配線層30と、所定の形状にパターン形成され、銅配線36と電気的に接続される銅配線57を有する第2の配線層50と、を備える半導体装置において、第2の配線層50は、所定の形状の配線溝62に銅配線57が埋め込まれた上部層間絶縁膜54と、銅配線57と銅配線36とを接続する接続孔61に銅配線57が埋め込まれた下部層間絶縁膜51と、上部層間絶縁膜54の配線溝62の下部と下部層間絶縁膜51との間に、銅の拡散を防止する所定の厚さの銅拡散防止用絶縁膜52と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】 電極サイズが大きい場合でも、アルミニウムを含むメタル配線に変質、変形等の悪影響を与えることなく、界面準位を十分に低減できるようにした半導体導体装置の製造方法を提供する。

【解決手段】 ゲート電極15両側のシリコン層5にS/D19とを形成する工程と、S/D19とが形成されたシリコン層5上に層間絶縁膜21を形成する工程と、層間絶縁膜21を選択的にエッチングしてコンタクトホールh1〜h3を形成する工程と、コンタクトホールh1〜h3の底面にTiN/Ti膜23を形成する工程と、TiN/Ti膜23が形成されたSOI基板10に水素シンターを施す工程と、水素シンターの後でTiN/Ti膜23上にアルミニウムを含むメタル配線31を形成する工程と、を含む。長チャネルトランジスタについては、メタル配線31に悪影響を与えることなく、シリコン層5とゲート絶縁膜13との間の界面準位を低減できる。

(もっと読む)

半導体装置の製造方法

【課題】 半導体記憶装置に係り、特に、高集積化されたDRAMを、少ない工程数で、且つ微細なセル面積で実現できる半導体記憶装置及びその製造方法を提供する。

【解決手段】 半導体基板10に形成されたメモリセルトランジスタと、メモリセルトランジスタのゲート電極20の上面及び側面を覆う絶縁膜42と、ソース拡散層24上に開口したスルーホール40と、ドレイン拡散層26上に開口したスルーホール38とが形成された層間絶縁膜36と、スルーホール40内壁及び底部に形成され、ソース拡散24層に接続されたキャパシタ蓄積電極46と、キャパシタ蓄積電極46を覆うキャパシタ誘電体膜48と、キャパシタ誘電体膜48を覆うキャパシタ対向電極54とを有するキャパシタと、スルーホール38の内壁及び底部に形成され、ドレイン拡散層と接続されたコンタクト用導電膜44とにより構成する。

(もっと読む)

半導体装置の製造方法

【課題】バリアメタルがない場合であっても、配線の平坦性を向上させることができる半導体装置の製造方法を提供する。

【解決手段】本実施例の半導体装置の製造方法は、半導体基板1上に層間絶縁膜2を形成し、層間絶縁膜2上に金属を含むメタルマスク3を形成し、メタルマスク3および層間絶縁膜2の一部をエッチングして、メタルマスク3および層間絶縁膜2にパターン溝2aを形成し、パターン溝2a内を埋め込むように、層間絶縁膜2上に導電層5を形成し、パターン溝2a内に導電層5を残すように、層間絶縁膜2上の余剰の導電層5を研磨する。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコンパターンの抵抗値を制御しつつ、多結晶シリコンパターンの上層に金属配線層を配置する。

【解決手段】半導体基板1上に多結晶シリコンパターンからなる抵抗体23と、半導体基板1上に形成された層間絶縁膜27と、層間絶縁膜27上に形成された金属配線層31を備え、抵抗体23として、同じ多結晶シリコンからなり、その上部に金属配線層31が配置されているものと配置されていないものとを含み、両抵抗体23,23の上部は層間絶縁膜27上に形成された第1窒化膜29で被われており、抵抗体23の上部に配置されている金属配線層31は第1窒化膜29上に形成され、抵抗体23の上部かつ金属配線層31の近傍領域での第1窒化膜29直上に第2窒化膜33が存在している。上部に金属配線層31が配置されている抵抗体23のシート抵抗値と上部に金属配線層31が配置されていない抵抗体23のシート抵抗値が等しくなっている。

(もっと読む)

半導体装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して作製した半導体装置を提供することを目的とする。また配線等のパターンを所望の形状で制御性よく形成できる技術を提供することを目的とする。

【解決手段】連続した波状形状有する形状のパターンを、均一な間隔をもって隣接して備えた半導体装置である。隣接するパターンにおいて、吐出する液滴の中心の位置が線幅方向に一致しないように、配線の長さ方向にずらして吐出する。液滴の中心がずれているので、パターン同士の線幅の最大個所(節の最大値)同士が隣接することがなく、より狭い間隔に隣接したパターンを設けることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】キャパシタ電極とコンタクトプラグとの導通性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、絶縁膜15−1と、前記絶縁膜中に設けられ、金属を主成分とするコンタクトプラグ16と、前記絶縁膜上に設けられ、前記金属より酸素親和性が高く、酸化物を主成分とする第1接着膜33−1と、前記コンタクトプラグ上および前記第1接着膜上に設けられ、酸素の拡散を防止するように働く第1キャパシタ電極21と、前記第1キャパシタ電極上に設けられたキャパシタ絶縁膜22と、前記キャパシタ絶縁膜上に設けられた第2キャパシタ電極23とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】 WPPを使用した半導体装置において、最上層配線間のショート不良を防止することにより、信頼性を向上させることのできる技術を提供する。

【解決手段】 最上層配線43aと再配線50との間に緩衝層47を設ける。このとき、例えば、最上層配線43aは銅膜より形成され、緩衝層47は、アルミニウム膜より形成される。さらに再配線50は、銅膜51とニッケル膜52の積層膜から形成される。このように構成された半導体装置において、低温と高温との間の温度サイクルで3重点Xに応力が集中する。この3重点Xに集中した応力は、緩衝層47の存在によって緩和され、3重点Xの直下にある界面Yへの応力の伝達を抑制することができる。このため、界面Yでの応力による剥離を防止できる。

(もっと読む)

電子装置およびその製造方法

【課題】 電力増幅モジュールやそれに用いる集積受動部品または半導体チップの低コスト化および高性能化を図る。

【解決手段】 集積受動部品5において、シード膜51、銅膜53およびニッケル膜54の積層膜からなる配線55により、RFパワーモジュールのローパスフィルタ回路を構成するインダクタ素子が形成される。ニッケル膜54は、銅膜53の全面上に形成され、表面保護膜としての絶縁膜61の開口部62から露出するニッケル膜54上に、金膜63およびバンプ電極64が形成されている。ニッケル膜54は、無電解Ni−Pめっき膜であり、リンを10重量%以上含有し、非磁性状態とされている。

(もっと読む)

層間絶縁構造およびその形成方法

【課題】層間絶縁体、あるいは層内絶縁体および層間絶縁体としてエアギャップを統合する銅のインタコネクトを製造する方法を提供すること。

【解決手段】層間絶縁構造の形成方法であって、第1の金属層を提供する工程と、第1の犠牲層を堆積する工程と、エッチング停止層を堆積する工程と、第2の犠牲層を堆積する工程と、2層のハードマスクを形成する工程と、2層のハードマスクをパターニングしてビアマスクおよびトレンチマスクを生成する工程と、第2の犠牲層をエッチングしてビアを形成する工程と、エッチング停止層の剥き出し部分と第1の犠牲層とをエッチングして第1の金属層を剥き出しにする工程と、第2の犠牲層をエッチングしてトレンチを形成する工程と、バリア金属および銅を堆積し、平坦化して第2の金属層を形成する工程と、第1および第2の犠牲層を分解して上記犠牲層をエアギャップと交換する工程とを包含する。

(もっと読む)

導電性パターンの形成方法、半導体装置の製造方法、および有機電界発光素子の製造方法

【課題】塗布技術を用いながらも、表面平坦性を確保しつつ薄型化された導電性パターンを形成可能な方法を提供する。

【解決手段】金属微粒子sを溶媒中に分散させてなるペースト材料を基板1上に塗布してペースト材料膜3を塗布成膜する。ペースト材料膜3を焼成処理して導電性材料膜5とする。導電性材料膜5をパターニングすることにより導電性パターン5aを形成する。その後、この導電性パターン5aをゲート電極とし、これを覆う状態でゲート絶縁膜を形成し、この上部にソース/ドレイン電極を形成する。次に、ソース/ドレイン電極間におけるゲート絶縁膜上に半導体薄膜を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】電気的にフローティングした配線に蓄積する電荷を、半導体基板に逃がすこと。

【解決手段】第1主面12aを備えた半導体基板12と、第1主面側に設けられたMOSFET14と、MOSFETのゲート電極26およびゲート電極に電気的に接続された配線を含む第1配線構造体36と、第1主面および第1主面に電気的に接続された配線を含む第2配線構造体38と、第1および第2構造体のどちらとも接触し、かつ、第1および第2配線構造体間を接続している、酸化イットリウムからなる非導電性膜16とを備える

(もっと読む)

半導体装置およびその製造方法

【課題】 切断された電気ヒューズの切断状態を良好に保つ。

【解決手段】 半導体装置100は、半導体基板(不図示)上に形成されるとともに凹部が形成された第1の絶縁膜102と、導電体206、ならびに導電体206の一端と他端にそれぞれ設けられた第1の端子202および第2の端子204を有し、第1の絶縁膜102上に設けられた電気ヒューズ200とを含む。導電体206は、第1の絶縁膜102の凹部を埋め込むように形成されるとともに、導電体206を構成する材料が凹部外に流出した流出領域212を有し、流出領域212とは異なる箇所が切断される。

(もっと読む)

1,981 - 2,000 / 2,592

[ Back to top ]