Fターム[5F033KK13]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | Au、Au合金 (399)

Fターム[5F033KK13]に分類される特許

361 - 380 / 399

基板及びその製造方法

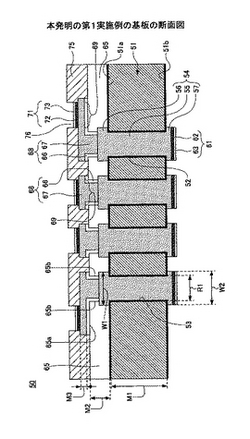

【課題】 本発明は、基材を貫通する貫通ビアと、貫通ビアと接続される配線とを備えた基板及びその製造方法に関し、配線が接続される貫通ビアの電気的な接続信頼性を向上することのできる基板及びその製造方法を提供することを課題とする。

【解決手段】 貫通部55と、貫通部の一方の端部に設けられ、貫通部の直径R1よりも幅広の形状とされた配線接続部56と、貫通部の他方の端部に設けられ、貫通部の直径R1よりも幅広の形状とされた接続パッド57とにより貫通ビア54を構成し、配線接続部56に外部接続端子69を有した配線68を接続する。

(もっと読む)

集積回路内での金属層の選択的形成

【課題】集積回路(IC)メタライゼーションにおいて信頼性が高いインターフェースを形成するための、生産的かつ制御可能な方法を与える。

【解決手段】埋め込み銅配線の表面が露出したビア底またはCMP直後の銅配線の上面での銅相互接続及び/またはコンタクトの信頼性を強化するための方法が与えられる。当該方法は、露出した銅表面を貴金属から成る気相化合物と接触させる工程と、銅置換反応または貴金属の選択的蒸着(例えば、ALDまたはCVD)により、露出した銅表面上に貴金属の層を選択的に形成する工程から成る。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体基板に形成された開口部の形成状態を、断面観察しないでも確認できるようにすることを目的とする。

【解決手段】 本発明の半導体装置は、半導体基板1上に形成されたパッド電極3を露出するように基板裏面から開口部が形成され、この開口部を介して前記パッド電極3に配線層10が形成されて成るものにおいて、前記開口部の形成状態をモニターするためのモニター開口部6bをスクライブライン上に形成することを特徴とするものである。

(もっと読む)

液晶表示装置の作製方法

【課題】本発明は、しきい値のずれが生じにくく、高速動作が可能な逆スタガ型TFTを有する液晶表示装置の作製方法を提供する。また、スイッチング特性が高く、コントラストがすぐれた表示が可能な液晶表示装置の作製方法を提供する。更には、少ない原料でコスト削減が可能であり、且つ歩留まりが高い液晶表示装置の作製方法を提供する。

【解決手段】 本発明は、耐熱性の高い材料でゲート電極を形成した後、非晶質半導体膜の結晶化を促進する触媒元素を有する層、非晶質半導体膜、及びドナー型元素又は希ガス元素を有する層を形成し加熱して、非晶質半導体膜を結晶化すると共に触媒元素を結晶性半導体膜から除いた後、該結晶性半導体膜の一部を用いて半導体領域を形成し、該半導体領域に電気的に接するソース電極及びドレイン電極を形成し、ゲート電極に接続するゲート配線を形成して、逆スタガ型TFTを形成する。

(もっと読む)

自動設計装置、自動設計方法、及び半導体集積回路

【課題】 斜め配線と直交配線とを有する多層配線構造の半導体集積回路においてクロストークの発生を抑制でき、ビアホールの配置制約の少ない半導体集積回路が設計可能な自動設計装置、自動設計方法、及び半導体集積回路を提供する。

【解決手段】 第1線群及び第2線群により定義される第1格子領域401a及び第3線群及び第4線群により定義される第1斜め格子領域402aを第1配線層400a上に設定し、第1〜第4線群を基準として第1配線41a及び第1斜め配線42aを第1配線層400a上に配置する第1層配線部14と、第1格子領域401a及び第1斜め格子領域402a上に重なる位置に、第2格子領域501a及び第2斜め格子領域502aを第2配線層500a上に設定し、第1〜第4線群を基準として、第2配線51a及び第2斜め配線52aを第2配線層500a上に配置する第2層配線部15とを含む。

(もっと読む)

再配線基板を用いたウェーハレベルチップスケールパッケージの製造方法

【課題】一般的なウェーハと同じ幅のスクライブ領域を有するウェーハを利用することによって、ウェーハ当たりチップの個数が減少しないようにするウェーハレベルチップスケールパッケージの製造方法を提供する。

【解決手段】再配線基板は、透明絶縁基板110に絶縁層をパターニングして形成されたパターン突起116と、その上に形成された再配線118とを含む。再配線基板は、ウェーハと別体に製造された後、ウェーハと接合される。パターン突起は、対をなし、一方は、ウェーハの活性面のチップパッド214に接触し、他方は、ウェーハのチップ領域に形成された貫通孔に対応する。貫通孔を介してウェーハの非活性面までに導電性配線223が形成され、導電性配線の一部に外部接続端子230が形成されている。すなわち、チップパッドは、再配線基板のパターン突起及び貫通孔内部の導電性配線により外部接続端子に電気的に連結されている。

(もっと読む)

パターン形成構造、パターン形成方法、デバイス及び電気光学装置、電子機器

【課題】パターン形成時に、微細パターンと他のパターンとの各々の高さを同じくすることにより、パターンを含む領域の上面に平坦領域を形成するバンク構造体、パターン形成方法、及び電気光学装置、電子機器を提供する。

【解決手段】機能液により形成するパターンに対応した凸部35が設けられた隔壁構造体であって、第1パターンに対応して設けられた第1凹部55と、第1パターンに接続され、かつ、第1パターンよりも幅が狭い第2パターンに対応して設けられた第2凹部56と、第1凹部55に少なくとも1以上設けられた凸部35と、を備えることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通孔内に密着性が良好な絶縁樹脂層が形成され、これを介してビア(スルーホール導通部)が形成された信頼性の高い半導体装置を提供する。

【解決手段】半導体装置は、表面に素子が集積・形成された半導体基板1と、この半導体基板を貫通する貫通孔2と、貫通孔の側壁面に形成された第1の絶縁樹脂層5と、半導体基板の表裏両面に形成された第2の絶縁樹脂層6と、貫通孔内で第1の絶縁樹脂層上に形成された第1の導体層と、第2の絶縁樹脂層上に形成され第1の導体層と導通された第2の導体層7を有する。半導体基板にレーザ照射して貫通孔を形成する工程と、貫通孔内に絶縁樹脂を充填する工程と、充填された絶縁樹脂に樹脂貫通孔を同心的に形成する工程と、樹脂貫通孔の側壁面に導体層を形成し、半導体基板の表面と裏面を導通させるビアを形成する工程とを備える。

(もっと読む)

配線パターン形成方法、TFT用ソース電極およびドレイン電極の形成方法

【課題】 液滴吐出装置から液滴を吐出してTFT用ソース電極またはドレイン電極を設けること。

【解決手段】 配線パターン形成方法は、バンクパターンに縁取られたパターン形成領域における所定のセクションへ液状の導電性材料の液滴を吐出して、パターン形成領域を覆う導電性材料層を形成するステップ(A)を含んでいる。セクションのX軸方向に沿った長さをLとし、Y軸方向に沿った長さをMとすると、吐出される液滴の直径φは、L以下であるとともに、M以下である。そして、ステップ(A)は、バンクパターンから少なくとも直径φの1/2倍離れた位置に液滴の中心が当たるように、液滴を吐出するステップ(a1)を含んでいる。

(もっと読む)

半導体素子及びその製造方法

【課題】メッキ配線形成後の熱処理工程におけるビアホール周辺での膜浮き、及び膜剥がれを抑制し、高歩留まりかつ高信頼性を有する半導体素子を提供する。

【解決手段】本発明の半導体素子は、半導体基板1上に、凸状の段差4が形成されており、段差4の上面から基板1裏面に達するビアホール2を有しており、ビアホール2内にはシード層5を下層に有する第1のメッキ配線6が形成され、ビアホール2近傍の基板1の表面は絶縁膜3で覆われている。さらに、第1のメッキ配線6は段差4を覆うように形成されている。半導体基板1の裏面には全面に電極8が設けられており、第1のメッキ配線6は基板1の裏面で電極8と接続されている。

(もっと読む)

電子部品およびその製造方法

【課題】 接触抵抗の小さい電子部品およびその製造方法を提供する。

【解決手段】 下層金属配線4と、下層金属配線4上に形成された層間絶縁膜6と、層間絶縁膜6上に形成され、かつ層間絶縁膜6に形成された貫通孔5を介して下層金属配線4と電気的に接続された上層金属配線7と、を備える電子部品であって、下層金属配線4が少なくとも第1の金属と第2の金属とが拡散されてなり、第1の金属は第2の金属より酸化物の標準生成自由エネルギーが大きく、第2の金属は前記第1の金属より波長350〜440nmの光線の少なくとも一点で反射率が高く、かつ、上層金属配線8と下層金属配線4との間に、第1の金属より酸化物の標準生成エネルギーが小さい金属で形成される密着層7を備える。

(もっと読む)

インダクタ及びその製造方法

【課題】チップ占有面積が小さく、自己共振周波数やQ値を高くできるオンチップインダクタ及びその製造方法を提供する。

【解決手段】互いに対面するように配置される右巻スパイラル構造と左巻スパイラル構造とが、半導体基板に対して水平方向を軸に巻かれて構成される。そして、右巻スパイラル構造の中心端と左巻スパイラル構造の中心端とが接続される。巻軸方向から見て、右巻スパイラル構造を流れる電流の向きと左巻スパイラル構造を流れる電流の向きが等しく、これらの配線がそれぞれ近傍に位置している。

(もっと読む)

アクティブマトリクス基板の製造方法、アクティブマトリクス基板、電気光学装置並びに電子機器

【課題】 ドライプロセスとフォトリソエッチングを組み合わせた工程の回数を低減することができるアクティブマトリクス基板の製造方法等を提供することを目的とする。

【解決手段】 アクティブマトリクス基板20の製造方法において、第1方向又は第2方向のいずれか一方の配線42が交差部56において分断された格子パターンの配線40,42,46を基板P上に形成する第1工程と、交差部56及び配線40,42,46の一部上に絶縁膜と半導体膜30とからなる積層部を形成する第2工程と、積層部上に分断された配線42を電気的に連結させる導電層49、及び半導体膜30を介して配線42と電気的に接続される画素電極45を形成する第3工程と、を有する。

(もっと読む)

少なくとも1つの試験接点構造を備えたチップ

半導体本体(6)と、半導体本体(6)に形成された集積回路(7)と、集積回路(7)を保護するように形成された不動態層(14)と、試験接点構造(15)とを備えるチップ(2)において、試験接点構造(15)は、不動態層(14)の下に位置する試験接点層(16)と、試験接点層(16)に接続される試験接点ブロック(18)とを有し、試験接点ブロック(18)の一部は不動態層(14)の穴部(17)を通って試験接点層(16)へと突出するとともに試験接点層(16)に接続し、試験接点ブロック(18)は不動態層(14)の上に位置する接点領域(20)を有する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の一面側に形成された半導体素子の電極端子と、この半導体基板の他面側に形成された外部接続端子用のパッドとを電気的に接続する距離を可及的に短距離にできる半導体装置を提供することにある。

【解決手段】半導体素子12が一面側に造り込まれた半導体基板10の半導体素子形成面側には、半導体素子12の電極端子12aから半導体基板10と電気的に絶縁されて延出されたパターン14と、半導体素子12及びパターン14を覆う絶縁層16とが形成され、 半導体基板10の他面側には、パターン14と電気的に接続された外部接続端子用のパッド32が形成された半導体装置であって、該半導体基板10の他面側に開口され且つ底面にパターン14の半導体素子近傍の半導体基板側面が露出する凹部は、その側壁面を覆う絶縁層22と、パターン14の半導体基板側面に一端部が接続されていると共に、他端部が前記凹部の開口部を覆うように形成されたパッド32に接続された金属から成る柱状導体部30とによって充填されていることを特徴とする。

(もっと読む)

半導体装置および半導体装置製造方法

【課題】 熱耐久性が高い半導体装置を提供することである。

【解決手段】 本発明の半導体装置は、主表面20と上記主表面と対向する裏面24とに開口端を有する貫通孔12を備える半導体チップ14を有する半導体装置10であって、上記貫通孔12内に約400℃以下で焼結する粒子径を有する金属ナノ粒子が焼結して形成された焼結体34を有することを特徴とする。

(もっと読む)

伝送線路及び半導体集積回路装置

本発明の伝送線路は、信号配線(3)と、誘電体層(2)を挟んで信号配線に対向する抵抗層(4)と、抵抗層に電気的に接続された接地用導体(11)とを備え、信号配線を所定周波数の高周波信号が伝送される際に、誘電体層によって信号配線と抵抗層との間に形成された容量を介して抵抗層に誘起される高周波電流が、抵抗層、及び抵抗層と接地用導体との間を流れる際に発生する単位長さあたりの抵抗を付加抵抗と定義し、前記高周波電流が接地用導体を流れる際に発生する単位長さあたりの抵抗を接地抵抗とした定義した場合に、付加抵抗が接地抵抗よりも大きい。  (もっと読む)

(もっと読む)

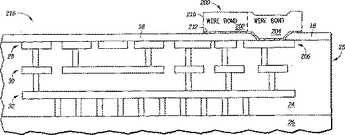

ボンディングパッドを有する半導体装置及びその形成方法

ボンディングパッド(200)は第1ワイヤボンディング領域(202)と、第2ワイヤボンディング領域(204)と、を含む。一実施形態では、第1ワイヤボンディング領域(202)がパッシベーション(18)を覆って延びる。別の実施形態では、ボンディングパッドはプローブ領域、第1ワイヤボンディング領域、及び第2ワイヤボンディング領域を有する。一実施形態では、プローブ領域及びワイヤボンディング領域がパッシベーション(18)を覆って延びる。ボンディングパッドはどのような数のワイヤボンディング領域及びプローブ領域も有することができ、かつこれらの領域をどのような構成として有することもできる。ボンディングパッドが複数のワイヤボンディング領域を含むことができるので、マルチチップパッケージにおける場合のように単一のボンディングパッドへの複数のワイヤ接続を行なうことができる。ボンディングパッドがパッシベーションを覆って延びる形でパッドを設けることができるので、集積回路チップ面積を小さくすることもできる。  (もっと読む)

(もっと読む)

電子素子の製造方法、コンタクトホールの形成方法、コンタクトホール、電子素子、表示素子、表示装置、半導体演算素子およびコンピュータ

【課題】 半導体演算素子や表示素子等の高集積化の下で、基本的な電子素子(電極や配線電極およびコンタクトホール)を作製する製造工程の低減を図れる電子素子の製造方法、コストの低減や信頼性の向上を図れる電子素子、表示素子、表示装置、半導体演算素子、コンピュータを提供する。

【解決手段】 第一の導電性材料層1上にパターニング層3を成膜するとともに、臨界表面張力の異なる第一の部位Aを、第一と第二の導電性材料層1、7が電気的に接続されるべき部位に形成する工程と、エネルギーの付与によって臨界表面張力が変化する機能と絶縁機能とを有する絶縁性濡れ変化材料層5を第一の部位A以外に成膜する工程と、絶縁性濡れ変化材料層5の一部分にエネルギーを付与することによって、臨界表面張力の異なる第二の部位Bを第一の部位Aに連通して形成する工程と、第二の部位B上に第二の導電性材料層7を形成する工程とを含む。

(もっと読む)

半導体装置

【課題】 多層配線構造において、層間の密着性を良好にする。

【解決手段】 半導体装置100には、半導体基板(不図示)上に、配線124が形成された第一の層間絶縁膜120と、ビア126が形成された第二の層間絶縁膜122とを含む多層配線構造が形成されている。半導体装置100は、配線124およびビア126が形成された回路領域110と、回路領域110を隔離するシールリングが形成されたシールリング領域112と、シールリング領域112の外周に形成された外周領域114とを含む。外周領域114において、第二の層間絶縁膜122中に、金属材料により構成されたダミービア136が形成される。

(もっと読む)

361 - 380 / 399

[ Back to top ]