Fターム[5F033KK13]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | Au、Au合金 (399)

Fターム[5F033KK13]に分類される特許

341 - 360 / 399

半導体装置の製造方法

【課題】拡散防止膜へのサイドエッチの発生を抑制することができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、金属配線上に順次形成された互いに異なる材料からなる第1及び第2絶縁膜に開口部を形成して金属配線を露出させる工程を備える半導体装置の製造方法であって、開口部の形成は、第2絶縁膜をリアクティブイオンエッチングし、第1絶縁膜をスパッタエッチングすることにより行うこと特徴とする。

(もっと読む)

半導体装置およびその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリント技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成するのではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 接地インダクタンスを容易に低減することができ、半導体チップの収率を向上可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】 半導体チップ21の第1主面に配置された半導体能動素子及び半導体能動素子のグランドパッド11と、第1主面に対して垂直な半導体チップの側壁面上に配置された第1メタル層24aと、第1メタル層24aに接続され、グランドパッド11上まで延在する第2メタル層25aとを備える。

(もっと読む)

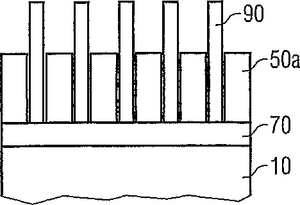

垂直な構造になるように意図的に製造されたナノチューブを有する集積電子部品

本発明は、基板(10)と、基板(10)の少なくとも一部に配置された少なくとも1つの金属多層組織と、金属多層組織上に配置されており、少なくとも1つの接続孔を有する非伝導性層(50)とを備え、接続孔には、少なくとも1つのナノチューブが、接続孔の底部にある金属多層組織上に成長しており、金属多層組織は、高融点金属層(20)と、金属分離層(30)と、触媒層(40)とを含んでいる集積電子部品に関する。本発明はさらに、ナノチューブを垂直構造に目的を絞って製造するための方法と、ナノチューブを垂直構造に目的を絞って製造するための金属多層組織の使用とに関する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置に備える半導体基板に形成された貫通穴を用いてバイアホール導体を電気めっきにより形成しようとするとき、貫通穴が金属材料で充填された状態となっているバイアホール導体が形成されることを可能にする。

【解決手段】 半導体基板2の第1の主面3側に、バイアホール形成用電極6を形成し、半導体基板2の第2の主面8側からエッチングし、それによって、バイアホール形成用電極6によって一方の開口端が塞がれた貫通穴12を半導体基板2に設け、次いで、貫通穴12においてバイアホール形成用電極6上に金属材料を堆積させることによって、貫通穴12を金属材料で充填した状態としたバイアホール導体13を形成するように、バイアホール形成用電極6に電流を流しながら電気めっきを実施する。

(もっと読む)

半導体装置の製造方法

半導体装置の製造方法は、基板の上に流動性を有する絶縁性物質よりなる流動性膜を形成する工程と、押圧部材の平坦な押圧面を前記流動性膜に押圧して流動性膜の表面を平坦化する工程と、押圧面を流動性膜に押圧した状態で流動性膜を第1の温度に加熱して表面が平坦化されている流動性膜を固化することにより、表面が平坦な固化膜を形成する工程と、表面が平坦な固化膜を前記第1の温度よりも高い第2の温度に加熱して固化膜を焼成することにより、表面が平坦な焼成膜を形成する工程とを備え

ている。  (もっと読む)

(もっと読む)

金属充填装置および金属充填方法

【課題】溶融金属充填法における歩留まりや品質の向上を目的として、溶融金属の表面の金属酸化物が基板に付着することを防止する。

【解決手段】内部を減圧する減圧手段14a,14bおよび内部を加圧する加圧手段15a,15bを備えたチャンバー11と、このチャンバー11内にて金属を加熱溶融することのできる金属溶融装置16とを備え、基板2に形成された微細孔へ金属を充填する金属充填装置10Aにおいて、前記金属溶融装置16に、加熱溶融された金属6の表面7を清浄に保つ金属表面浄化機構20を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】エレクトロマイグレーション耐性に優れた配線を実現する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板上の第2の層間絶縁膜2中に形成された下層配線8と、下層配線8上の第3の層間絶縁膜11中に形成されたメタルプラグ13と、第4の層間絶縁膜12中に形成された上層配線19とは、その底面及び側面が密着層とバリア層とからなるバリアメタル層によって覆われている。これにより、配線層と層間絶縁膜との間にバリアメタル層が介在するため、電流印加時のボイド発生が抑制され、配線の信頼性が向上する。

(もっと読む)

半導体装置及びその製造方法

【課題】 製造工程数を削減し、低コスト化を実現した半導体装置を提供する。

【解決手段】 本発明の半導体装置は、半導体チップ上に形成されたパッド2と、前記パッド2上に形成された電極接続部7と、前記パッド2を露出するように前記半導体チップの裏面に形成された開口部14と、前記開口部14の側壁に形成された第1の絶縁膜15と、前記第1の絶縁膜15を有した前記開口部内に形成された金属膜(Cu17)とを具備することを特徴とするものである。

(もっと読む)

半導体装置の作製方法

【課題】材料の利用効率を向上させ、作製工程を簡略化した半導体装置の作製技術を提供することを目的とする。また、それらの半導体装置を構成する配線等のパターンを、所望の形状で密着性よく形成できる技術を提供することも目的とする。

【解決手段】第1の導電層上に第1の絶縁層を形成し、第1の絶縁層上に第2の絶縁層を形成し、第2の絶縁層上に第1の開口を有する第1のマスク層を形成し、第1の絶縁層及び第2の絶縁層をエッチングすることにより、第1の導電層に達する第1の開口部を形成し、第1のマスク層除去後、第1の開口よりも開口面積が広い第2の開口を有し、且つ、導電性材料を含む組成物に対してぬれ性の低い第2のマスク層を第2の絶縁層上に形成し、第1の絶縁層上面の一部が露出するように第2の絶縁層をエッチングし、第2の開口部を形成し、第1の開口部及び第2の開口部に導電性材料を含む組成物を充填し、第2の導電層を形成する。

(もっと読む)

絶縁膜及び半導体装置の作製方法

【課題】複数の空孔を有する絶縁膜の形成方法を提案する。また、高集積化された半導体装置の歩留まり高い作製方法を提案する。

【解決手段】層間絶縁膜の低誘電率化の方法として、レーザ光を用いて層間絶縁膜中に複数の空孔を作成形成してすることにより、多孔質の絶縁膜を形成することを特徴とする。また、インクジェット法に代表される液滴吐出法を用いて、前記多孔質の絶縁膜に導電性粒子を含む組成物を吐出し、焼成して配線を形成する。レーザ光としては、超短パルスレーザーレーザ光を用いることが好ましい。

(もっと読む)

半導体装置の作製方法

【課題】従来のCMPプロセスを用いることなく、高アスペクト比の開口を有する接続孔にも良好な埋め込みが可能である半導体装置の作製方法を提供する。また、従来よりも少ない工程数で、配線形成が可能な方法を提供することを目的とする。更には、高集積化された半導体装置の歩留まり高い作製方法を提案する。

【解決手段】複数の空孔を有する絶縁膜表面に撥水表面を有する膜を形成し、撥水表面を有する膜の一部に光を照射して、親水表面を有する領域を形成した後、親水表面を有する領域に導電性粒子を有する液状物質を吐出し、焼成して導電膜を形成することを特徴とする。

(もっと読む)

半導体装置

【課題】実装面積が小さく性能ばらつきの少ないインダクタを有する半導体装置を提供する。

【解決手段】半導体基板10と、半導体基板10の表面11に配列して形成される少なくとも一つ以上の配線パターン13と、半導体基板10の裏面に配列して形成される少なくとも一つ以上の配線パターン14と、表面側及び裏面側の配線パターン13,14の夫々の面内に形成される、表面11から裏面12に貫通する少なくとも一つ以上の貫通電極15と、を有し、配線パターン13と配線パターン14とを貫通電極15を介して螺旋状に接続することにより形成される螺旋状インダクタ16を有する半導体装置1を提供する。

(もっと読む)

半導体集積回路装置及びそれを用いた車載レーダシステム

【課題】能動回路と受動回路とを含む半導体集積回路装置において、チップ面積を縮小可能としながら、高周波損失を低減し且つ段差による配線切れを防止できるようにする。

【解決手段】半導体集積回路装置(MMIC)は、サファイアからなる基板11上の一部の領域に形成されたIII-V族窒化物半導体層15からなるHFET19と、基板11の上に、III-V族窒化物半導体層15の上面、側面及び上端の角部を覆うように形成された誘電体膜20とを有している。基板11の上には、誘電体膜20を介在させて形成されたマイクロストリップ線路25aと、誘電体膜20の上に形成され、HFET19とマイクロストリップ線路25aとを電気的に接続するドレイン引き出し配線25とを有している。

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 製造に係る期間の短縮及びコストの低減を図ると共に、製品としての信頼性の向上に寄与することができる「半導体装置及びその製造方法」を提供すること。

【解決手段】 機能素子が作り込まれた半導体基板11の一方の面に、絶縁層12を介して導体層13を形成した後、半導体基板11の所定の箇所にスルーホールTH1を形成する。さらに、半導体基板の他方の面に支持シートを張り付け、導体層13と支持シート上とをワイヤ14により接続し、導体層13、ワイヤ14及びスルーホールTH1が形成されている部分を樹脂16で封止した後、支持シートを除去する。さらに、半導体基板11の他方の面から露出しているワイヤ14の端部14a上に導体層15を形成する。

(もっと読む)

ショットキーバリアダイオード及びダイオードアレイ

【課題】耐圧が高く且つオン抵抗が低い上に、チップ面積が小さいショットキーバリアダイオード及びダイオードアレイを実現できるようにする。

【解決手段】導電性のシリコン基板2の上にバッファ層3と、アンドープの窒化ガリウムである第1の半導体層4と、アンドープのアルミニウム窒化ガリウムである第2の半導体層5とが順に形成されている。第2の半導体層5の上には、ショットキー電極6とオーミック電極7とが互いに間隔をおいて形成されている。第2の半導体層5と第1の半導体層4とバッファ層3とを貫通して、n+−Si基板2に達するビア8が形成されており、オーミック電極7とn+−Si基板2とは電気的に接続されている。n+−Si基板2の裏面には裏面電極1が形成されており、オーミック電極7は基板2の裏面に引き出されている。

(もっと読む)

半導体装置の製造方法

【目的】 選択的に拡散防止膜を形成する場合でも、配線同士間でショートが生じてしまう原因となる導電性材料の研磨残りを生じさせないようにすることを目的とする。

【構成】 基体上の開口部に形成された導電性材料膜上に前記導電性材料膜に用いる導電性材料の拡散を防止する拡散防止膜を選択的に形成する拡散防止膜形成工程(S120〜S122)と、前記拡散防止膜が形成された後、前記基体上に絶縁膜を形成する絶縁膜形成工程(S124〜S128)と、前記絶縁膜形成工程の後、前記絶縁膜表面を研磨する平坦化工程(S130)と、を備えたことを特徴とする。

(もっと読む)

配線パターン形成方法および配線パターン

【課題】液滴吐出装置から液滴を吐出してTFT用ソース電極またはドレイン電極を設けること。

【解決手段】基板10Aの表面Sにヘキサメチルシラザンを基板10Aの表面Sに塗布し、HMDS層12を形成するヘキサメチルシラザン層形成工程と、HMDS層12上に、有機感光性材料層を形成する有機感光性材料層形成工程と、前記有機感光性材料層をパターニングしてバンクパターン18を形成する工程と、バンクパターン18によって縁取られた領域に、インクジェット法を用いて、導電性材料を付与する導電性材料付与工程と、を含んでいる。

(もっと読む)

薄膜パターン形成方法、半導体装置、電気光学装置、及び電子機器

【課題】 薄膜形成領域の断面全域に機能液を充填することにより、形成される薄膜の機能を実現するために充分な断面積と必要な断面形状を有する薄膜を形成することができる、薄膜パターン形成方法、半導体装置、電気光学装置、及び電子機器を実現する。

【解決手段】 薄膜パターン形成方法は、第1の薄膜を構成する材料を含む機能液に対して親液性を有する第2の薄膜を形成するステップと、第2の薄膜の表面に、機能液に対する撥液性を付与する処理を行うステップと、第2の薄膜の一部を取り除いて、第1の薄膜のパターン形状を規定する凹部を形成するステップと、凹部に向けて機能液を吐出するステップと、凹部に吐出された機能液を乾燥させて第1の薄膜を形成するステップとを有する。半導体装置の回路配線は、上記薄膜パターン形成方法を用いて形成されており、電気光学装置は当該半導体装置を備え、電子機器は上記電気光学装置を備える。

(もっと読む)

341 - 360 / 399

[ Back to top ]