Fターム[5F033KK13]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | Au、Au合金 (399)

Fターム[5F033KK13]に分類される特許

321 - 340 / 399

薄膜トランジスタ及び半導体デバイスの作製方法

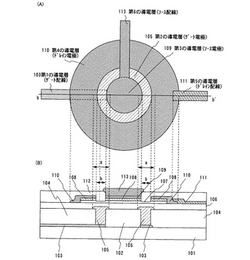

【課題】液滴吐出法などのマスクレスプロセスを用いて円形薄膜トランジスタを作製することにより、工程の簡略化、作製時間の短縮、及び作製費用の低減を図ると共に、従来よりもその形状が制御された円形薄膜トランジスタの作製方法を提供することを目的とする。

【解決手段】液滴吐出法等のマスクレスプロセスを用いて、基板上に同心円状の薄膜を積層し、円形の電極を有する円形薄膜トランジスタを形成する。また、液滴吐出法等のマスクレスプロセスを用いて、基板上に同心円状の薄膜を積層し、円形の半導体層を有する円形薄膜トランジスタを形成してもよい。

(もっと読む)

膜パターンの形成方法、半導体装置、電気光学装置、及び電子機器

【課題】 バンクに撥液化処理を行う際の、機能膜へのダメージを解消した膜パターンの形成方法と、これによって得られた膜パターンを備えた半導体装置、電気光学装置、及び電子機器を提供する。

【解決手段】 基板Pに設けられたゲート絶縁膜28(機能膜)上に機能液を配置して膜パターンを形成する方法である。基板Pにゲート絶縁膜28を設け、ゲート絶縁膜28上にポリシラザン液、ポリシラン液またはポリシロキサン液のいずれかを塗布し乾燥してバンク膜31を形成する。そして、マスクMを用いてバンク膜31を選択的に露光し、バンク膜31に撥液処理を施す。バンク膜31を現像処理することでゲート絶縁膜28を露出させ、パターン形成領域を区画するバンクを形成する。パターン形成領域に前記機能液を配置し、膜パターンを形成する。少なくとも、バンク膜31に撥液処理を施す工程は、バンク膜31を現像処理しバンクを形成する工程より前の工程で行う。

(もっと読む)

膜パターンの形成方法、アクティブマトリクス基板、電気光学装置、及び電子機器

【課題】 分断されたパターン形成領域にキャップ層を有した膜パターンを形成する際に、その形成工程を簡略化することにより、膜パターンの生産性を向上した、膜パターンの形成方法、アクティブマトリクス基板、電気光学装置、及び電子機器を提供する。

【解決手段】 基板P上に、第1のパターン形成領域52,53と、交差部56で分断される第2のパターン形成領域55とを備えるパターン形成領域を区画するバンク51を形成する。そして、第1のパターン形成領域52,53に第1の膜パターンを、第2のパターン形成領域に第2の膜パターンを形成した後、基板の全面に撥液処理を施す。その後、第2の膜パターンの各所定の位置の撥液性を選択的に保持させたまま、基板上の撥液性を低下させる。第1の膜パターン、及び第2の膜パターン上にキャップ層を積層し、第2の膜パターンの各所定の位置における撥液性を除去し、各所定の位置間に導電膜により接続する。

(もっと読む)

半導体集積回路配線構造

【課題】エレクトロマイグレーション劣化が生じにくく、高電流密度まで安定して通電可能な高信頼半導体集積回路配線構造を実現させること。

【解決手段】半導体基板上に堆積された下敷き絶縁膜層である酸化シリコン膜11の上に、Ti層12-1、Pt層12-2、Au層12-3、Pt層12-4、Ti層12-5を順次堆積してリフトオフすることによって、積層配線金属層12を形成し、酸化シリコン膜11と積層配線金属層12との上に、層間絶縁膜層である窒化シリコン膜13を堆積することによって半導体集積回路配線構造を構成する。

(もっと読む)

半導体パッケージ及び同パッケージを形成する方法

金がバックメタル層(118)から半田(164)に溶出するのを防止する半導体パッケージ(100)、及び同パッケージを形成する方法が提供される。例示としての方法では、金属パッド(112)及び基板(116)を含む半導体ウェハ積層構造(110)を設ける。接着/メッキ層(115)を基板(116)の上に形成する。金層(118)をメッキにより接着/メッキ層(115)の表面に形成する。金層をダイシングストリート領域(124)でエッチングして、金層(118)及び接着/メッキ層(115)のエッジ部分(128)を露出させる。バリアメタル層(130)を堆積させてエッジシール(129)を露出エッジ部分(128)の周りに形成する。エッジシール(129)は、ウェハ積層構造(110)をリードフレーム(162)に半田付けするときに、金がバックメタル層(118)から半田(164)に溶出する現象を防止する。  (もっと読む)

(もっと読む)

表示装置、及び表示装置の作製方法

【課題】信頼性の高い表示装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】一導電型の不純物領域を含む半導体層と、半導体層上にゲート絶縁層と、ゲート電極層と、一導電型の不純物領域と接する配線層と、ゲート絶縁層上に設けられ、配線層と接する導電層と、導電層と接する第1の電極層と、第1の電極層上に電界発光層と、第2の電極層とを有し、配線層は導電層を介して第1の電極層と電気的に接続している。

(もっと読む)

液晶表示装置及びその製造方法

【課題】 ソース配線2からの漏れ電界による液晶300の配向の乱れを低減すると共に、開口率が大きく、かつ、製造工程を増加することなくソース配線2と対向電極6との短絡が発生しにくい液晶表示装置及びその製造方法を得る。

【解決手段】 ソース配線2より下層にゲート絶縁膜8を介して、ソース配線2に沿って配置された第1の電極パターン11と、ソース配線2より上層に層間絶縁膜9を介して、ソース配線2に沿って、且つ前記ソース配線2に実質的に重なり合わない位置に配置された第2の電極パターン12とによって、ソース配線2からの漏れ電界を上下層に配置された電極パターン11、12により効果的に遮蔽する。また、第1の電極パターン11はゲート配線1と、第2の電極パターン12は対向電極6と同一層の導電膜で形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 良好な特性を有するMIM型キャパシタを半導体基板上に形成し、特別な製造工程を追加せずに製造する半導体装置及びその製造方法を提供する。

【解決手段】

下層層間絶縁膜3上に形成されたMIM型キャパシタ11(下部電極膜8a、キャパシタ絶縁膜9a、上部電極膜10aからなる)は、下層配線6と上層配線14cを接続するプラグ14aと同じ高さに形成することにより、上部電極用接続孔を必要としない。

(もっと読む)

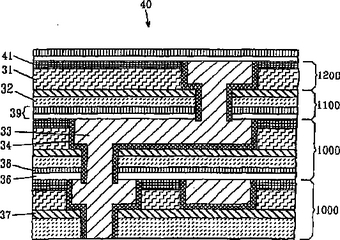

半導体装置、積層半導体装置およびそれらの製造方法

【課題】高抵抗化や接触不良の低減が可能になるように改良された半導体装置を提供することを主要な目的とする。

【解決手段】配線層106を持つ半導体装置150a、150b、150cにおいて、その表面から裏面に達する貫通孔110が存在し、貫通孔110の内壁には、各配線層106の側壁の一部が露出している。貫通孔110の内部には導電材料112が存在し、該貫通孔110内で、各配線層106の側壁の一部と、導電材料112が電気的に接続されている。この発明によれば、半導体装置150a、150b、150cを積層する際の、積層段数増加による貫通孔形成用マスク数の増加無く形成する事ができ、同一設計寸法の貫通孔110で全ての半導体装置を形成できる為、半導体装置面積の縮小もできる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置及びその製造方法における信頼性の向上を図る。

【解決手段】本発明の半導体装置は、半導体基板1上に第1の絶縁層2を介して形成されたパッド電極3と、前記半導体基板1の裏面から前記パッド電極3の表面に到達するように形成されたビアホール8とを有するものにおいて、前記ビアホール8が、前記半導体基板1の裏面に近い部分よりも前記パッド電極3に近い部分の開口径が広くなるように形成された第1の開口部7Aと、前記第1の開口部7Aに連なり、前記半導体基板1の表面に近い部分よりも前記パッド電極3の表面に近い部分の開口径が狭くなるように前記第1の絶縁層2に形成された第2の開口部7Bとから成ることを特徴とする。

(もっと読む)

超小型電子相互接続構造の多層キャップ障壁

【課題】超小型電子相互接続構造の多層キャップ障壁を提供すること。

【解決手段】本明細書には、少なくとも1つの低kサブレイヤと少なくとも1つの空気障壁サブレイヤとを有する低k多層誘電拡散障壁層を有する構造が記載される。多層誘電拡散障壁層は金属の拡散に対する障壁であり、かつ空気の透過に対する障壁である。この構造の生成に関連した方法および組成物も記載される。これらの低k多層誘電拡散障壁層を利用する利点は、導電性金属フィーチャ間のキャパシタンスの低下によるチップ性能の増大、および多層誘電拡散障壁層が空気を通さず金属拡散を防ぐことによる信頼性の増大である。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】熱膨張差に起因する応力歪みを樹脂ポストにおいて効果的に吸収・緩和させることができるとともに、高密度な配線設計が可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】電極9を有する半導体基板1上の所定位置に形成された突起状の樹脂ポスト3と、前記樹脂ポスト3上に形成され一端部が前記電極9に電気的に接続された金属配線層4と、前記金属配線層4上に形成され前記樹脂ポスト3の頂部に整合する領域に前記金属配線層4を露出する開口部5bを備えた絶縁性の封止層6と、前記開口部の金属配線層上に形成された金属パッド7と、前記金属パッド7上に載置されたはんだバンプ8とを備えてなる半導体装置。

(もっと読む)

膜パターンの形成方法、デバイスの製造方法、電気光学装置、並びに電子機器

【課題】隔壁により区画領域を設けて液滴塗出法により液滴を配置する際に、区画領域端部で液滴が十分に塗れ広がらず空隙が残ったり、局所的に膜厚が薄くなったりしてしまう、という課題を解決することを目的とする。

【解決手段】本発明の膜パターンの形成方法は、機能液の液滴を基板上に配置することにより膜パターンを形成する膜パターンの形成方法であって、前記基板上に前記膜パターンに応じた隔壁を形成する工程と、前記隔壁によって区画された領域に前記機能液の液滴を配置する工程とを有し、前記区画領域の端部は曲率を持たせて形成し、液滴が塗れ広がる距離を短くして機能液の充填性を向上させる。

(もっと読む)

高周波伝送線路

【課題】 高周波伝送線路に関し、半導体集積回路基板、特に、シリコン集積回路基板であっても、誘電体層を用いることなく、マイクロストリップ線路のような高周波伝送線路を作製できるようにする。

【解決手段】 半導体基板11上に形成したグランド電極13と、グランド電極13と間隙を介して対向し、且つ、該対向した面と反対側の面で線路支持体絶縁層16を介して線路支持体17に支持された伝送線路15とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 誘導素子の磁束が半導体基板上のデバイス等に影響を与えることなく、誘導素子を自由に配置することができる半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板2上に誘導素子3が形成された半導体装置1において、接地電極5を介して半導体基板2に接地されたシールド部15を、絶縁樹脂層10,12を挟んで誘導素子3と厚み方向において重なる位置に配置する。これにより、シールド部15が誘導素子3の磁束を遮断し、この誘導素子3の磁束が半導体基板2上のデバイス等に影響を与えるのを防ぐことができる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】より高性能、高信頼性の記憶装置、及びその記憶装置を備えた半導体装置を低コストで、歩留まりよく作製できる技術を提供することも目的とする。

【解決手段】第1の導電層と、第1の導電層の側端部と接して設けられる第1の絶縁層と、第1の導電層及び第1の絶縁層上に設けられる第2の絶縁層と、第2の絶縁層上に設けられる第2の導電層とを有し、第2の絶縁層は、絶縁性材料によって形成されており、絶縁性材料が流動化したときの流動化物に対するぬれ性は、第1の導電層より第1の絶縁層の方が高い。

(もっと読む)

膜パターンの形成方法、デバイス及びその製造方法、電気光学装置、並びに電子機器

【課題】 微細化や細線化が図られた膜パターンを、精度よく安定して形成することができる薄膜パターンの形成方法を提供する。

【解決手段】 基板P上にバンクBを形成する工程と、バンクBによって区画された領域に機能液Lを配置する工程と、基板P上に配置された機能液Lを乾燥させて膜パターンFを形成する工程とを有する。バンクBの形成材料は、ポリシラザンを主成分とする感光性のバンク形成材料を焼結した無機質の材料からなる。

(もっと読む)

半導体素子の製造方法、電気光学装置、および電子機器

【課題】 本発明は、絶縁膜として酸化シリコン膜等の無機絶縁膜を用いる場合にも、少ない工程で簡易にコンタクトホールを形成することができる半導体素子の製造方法を提供することを目的とする。

【解決手段】 本発明は、第一の導電膜(16)上に、所定の処理によって絶縁膜に変換され、且つ所定の液体に溶解または分散可能である、絶縁膜の前駆体膜(18)を形成する第一工程と、前記絶縁膜の前駆体膜のコンタクトホールを形成すべき位置に、上記所定の溶液を供給し、前記絶縁膜の前駆体膜にコンタクトホール(20)を形成する第二工程と、絶縁膜の前駆体膜を絶縁膜(18’)に変換する第三工程と、を含む半導体素子の製造方法を提供するものである。

(もっと読む)

半導体装置

【課題】 ゲート電極に多結晶Si/金属積層構造を用いつつ、多結晶Si/金属界面の空乏化を抑制することを目的とする。

【解決手段】

ゲート電極が上層に多結晶Si層6、下層に金属層(TiN層7)の積層構造を成して、かつ上部配線とのコンタクト部分は、上部配線がゲート積層構造の下層金属層まで到達させることで、多結晶Siと下層金属(TiN)に電位差が生じないため、空乏層が伸びることなく、ゲートに印加した電圧と同じだけゲート絶縁膜に電圧が掛かり十分なキャリアがチャネル領域に形成され、駆動電流の向上が得られる。また、ゲート加工が基本的には既存技術をそのまま適用できるため、金属ゲート電極を有する半導体装置の製造及びその技術開発が簡略化される。

(もっと読む)

半導体装置の製造方法

【課題】 単位基板あたりの半導体チップ数を増加できる半導体装置の製造方法を提供する。

【解決手段】 この半導体装置の製造方法では、半導体基板1の主面S1に切断すべき部分1hを露出する様にしてマスク7を形成し、そのマスク7に基づき前記切断すべき部分1hをエッチングにより切断することにより、半導体基板1を個々の半導体チップに分割する。

(もっと読む)

321 - 340 / 399

[ Back to top ]