Fターム[5F033KK13]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | Au、Au合金 (399)

Fターム[5F033KK13]に分類される特許

301 - 320 / 399

半導体装置及びその製造方法

【課題】初期電気特性の向上及びストレスマイグレーション信頼性の向上を両立させた半導体装置及びそのような半導体装置を製造することができる半導体装置の製造方法を提供する。

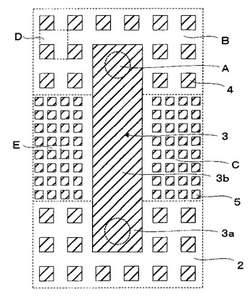

【解決手段】半導体装置は、半導体基板と、半導体基板上に形成された層間絶縁膜2と、層間絶縁膜2上に形成された層間絶縁膜と、層間絶縁膜2内に形成され、プラグ接続部3aを有する配線3と、層間絶縁膜内に形成され、プラグ接続部3aに接続されたビアプラグと、層間絶縁膜2内かつプラグ接続部3aの近傍に形成された複数の第1のダミー配線4と、層間絶縁膜2内かつプラグ接続部3aを除く配線3の部分の近傍に形成され、第1のダミー配線4より小さい幅及び第1のダミー配線4より大きい1つのダミー配線の単位当たりのパターン被覆率の少なくともいずれかを有する複数の第2のダミー配線5とを備えている。

(もっと読む)

化合物半導体スイッチ回路装置

【課題】基板を貫通するバイアホールとその内壁の縦型金属層によって、基板の第1主面のスイッチング素子と、第2主面の電極パッドを接続したスイッチMMICにおいて、隣接する縦型金属層に異なる高周波信号が伝搬する場合、基板に伸びる空乏層によって、縦型金属層間に高周波信号が漏れる問題があった。

【解決手段】異なる高周波信号が印加される縦型金属層間に縦型n+型領域を設ける。これにより一方の縦型金属層から伸びる空乏層が他方に到達することを防止し、高周波信号の漏れを抑制する。また制御抵抗の一部に、縦型n+型領域による縦型抵抗を接続することにより、制御抵抗のチップ上の占有面積を小さくできる。

(もっと読む)

構造の作製方法

金層(20)が金酸化物マスク(30)でパターニングされる。前記マスクは、酸によってパターニングされ、好適にはマイクロコンタクトプリントによってパターニングされる。金酸化物マスク(30)は、金層(20)用のアルカリエッチング溶液中で安定である。金酸化物マスク(30)は、再曝露可能な金パッド(20)を形成するように維持されて良い。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】 MIM構造の容量素子の、半導体基板上に形成した時に単位面積当たりで得られる容量値(容量密度)を高くする。また、前記MIM構造の容量素子を有する半導体集積回路装置を小型化する。

【解決手段】 半導体基板上に、第1金属膜、第1絶縁膜、第2金属膜、第2絶縁膜、第3金属膜を順次積層してなり、前記第1金属膜と第3金属膜が電気的に接続され、前記第1金属膜、第1絶縁膜、第2金属膜により構成される第1容量と、前記第2金属膜、第2絶縁膜、第3金属膜からなる第2容量が並列に接続されており、前記第2容量の容量として機能する容量真性部が前記第1容量の容量として機能する容量真性部の内側に設けられているMIM構造の容量素子である。

(もっと読む)

半導体装置の製造方法

【課題】バリアメタルがない場合であっても、配線の平坦性を向上させることができる半導体装置の製造方法を提供する。

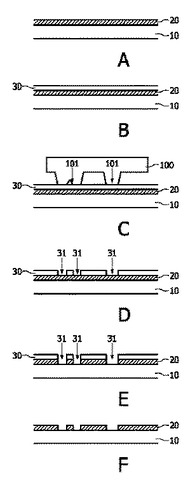

【解決手段】本実施例の半導体装置の製造方法は、半導体基板1上に層間絶縁膜2を形成し、層間絶縁膜2上に金属を含むメタルマスク3を形成し、メタルマスク3および層間絶縁膜2の一部をエッチングして、メタルマスク3および層間絶縁膜2にパターン溝2aを形成し、パターン溝2a内を埋め込むように、層間絶縁膜2上に導電層5を形成し、パターン溝2a内に導電層5を残すように、層間絶縁膜2上の余剰の導電層5を研磨する。

(もっと読む)

半導体ウエハ及びその製造方法

【課題】

複数の半導体チップを積層するときの、コンタクト電極を、半導体基板の裏面から加工するための製造方法を提案する。

【解決手段】

半導体基板の裏面から開口部がすり鉢状の貫通孔を形成した後、絶縁膜を形成し、その後、貫通孔の底面のコンタクト部となる部分の絶縁膜を除去し、シード層をスパッタした後、Auメッキとパッド部のパターンニングによりコンタクト電極を形成することを特徴とする。

【効果】

貫通孔の開口部がすり鉢状であるため、フォトリソグラフィー時、孔にレジストが充填されやすく、露光時に孔の底面まで光がまわりやすいため、孔底面の絶縁膜に開口パターンを形成することができる。これにより、裏面と素子面との電気的な接続が可能となる。さらに、半導体基板の裏面からの加工であるため半導体素子がプラズマによる影響を受けず、素子の欠陥が発生しない。

(もっと読む)

半導体チップおよびその製造方法、ならびに半導体装置

【課題】歩留まりと信頼性の高い貫通電極を有した半導体チップおよびその製造方法を提供する。

【解決手段】この半導体チップ1は、半導体基板2を含んでいる。半導体基板2の表面には導電層3が形成されている。導電層3の下部には、半導体基板2を厚さ方向に貫通する貫通孔5が形成されている。貫通孔5内には、貫通電極8が設けられている。半導体基板2の表面には、貫通孔5を形成する前に予め、補強構造体4が、貫通孔5を完全に覆い尽くすように、貫通孔5よりも大きい径で配置されている。これにより、導電層3は、常に貫通孔5の反対面において補強構造体4で、支えられることにより、導電層3のクラックが防止される。

(もっと読む)

分離及び不動態の層用の支持構造を有する半導体装置

半導体装置の異なる、積み重ねられる金属性層の間の導通及びビアが、機械的な歪によって機械的に損傷されることがある。本発明の模範的な具体例によれば、この機械的な歪が基材に対する構造を通じて基礎構造の格子並びに基礎構造によって接続される分離の及び不動態の層によって移され得る。これは半導体装置の寿命の増大を提供し得る。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 表面にキャップメタル膜が形成された銅配線を含む半導体装置において、ビア接続の歩留まりや抵抗の均一性を良好にする。

【解決手段】 本発明の半導体装置の製造方法は、半導体基板上に形成された絶縁膜に、配線溝を形成する工程(S100)と、絶縁膜上全面に、バリアメタル膜を形成する工程(S102)と、バリアメタル膜上全面に、配線溝内を埋め込むように銅膜を形成する工程(S104)と、絶縁膜表面に、バリアメタル膜が残る条件で、配線溝部外の銅膜を研磨により除去する工程(S106)と、銅膜を研磨により除去する工程の後に、配線溝部内に形成された銅膜上に、選択的にキャップメタル膜を形成する工程(S108)と、キャップメタル膜を研磨により平坦化する工程(S110)とを含む。

(もっと読む)

薄膜トランジスタ基板及び薄膜トランジスタ基板の製造方法

【課題】薄膜トランジスタの特性が向上した薄膜トランジスタ基板を提供する。

【解決手段】本発明は薄膜トランジスタ基板と薄膜トランジスタ基板の製造方法に関する。本発明による薄膜トランジスタ基板は、絶縁基板と絶縁基板上に形成されたゲート電極と;ゲート電極上に形成され、ゲート電極の少なくとも一部を露出させる開口部が備えられた第1ゲート絶縁膜と;開口部によって露出されたゲート電極を覆い、第1ゲート絶縁膜より誘電率が大きい第2ゲート絶縁膜と;第2ゲート絶縁膜を中心に互いに分離してチャネル領域を定義するソース電極及びドレイン電極と;チャネル領域に形成された有機半導体層とを含むことを特徴とする。

(もっと読む)

超小型電子技術における電極パッド

ある実施の形態に係る集積回路(30)は、基板(38)と、基板の上に設けられた回路素子(34)と、電極パッド(72)と、を含み、回路素子が基板と電極パッドとの間に配置されるように、電極パッドが回路素子の上に配置され、かつ垂直軸に沿って回路素子と一直線上に並べられるという特徴を持つ。 (もっと読む)

コンタクトホール/層間絶縁膜の形成方法、コンタクトホール/層間絶縁膜、表示素子、表示装置、半導体演算素子およびコンピュータ

【課題】 コンタクトホール/層間絶縁膜を形成・製造する工程全体の短縮化、簡素化、コストダウンを図れ、また絶縁膜材料の選定が限定されることなく有機半導体材料を使用しても損傷を与えない溶剤・溶媒を用いることが可能なコンタクトホール/層間絶縁膜の形成方法等を提供する。

【解決手段】 第一の導電性材料層1上に低臨界表面張力層3を形成し、UV照射により低臨界表面張力部3aを形成する工程と、低臨界表面張力部3aよりも高い臨界表面張力を有し、かつ、半導体層を冒さない第一の絶縁材料層5を低臨界表面張力部3a以外に形成した後、第一の絶縁材料層5上に第二の絶縁材料を成膜して第二の絶縁材料層6を形成する工程と、第二の絶縁材料層6上に疎水性材料層9を形成する工程と、疎水性材料層9における第二の導電性材料層を形成する部位のみにUV照射により、高臨界表面張力部9bを形成した後、第二の導電性材料層7を形成する工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 比誘電率の低い絶縁膜を備え、かつ、電気的性能の劣化および信頼性の劣化を抑制することが可能な、多層配線構造の半導体装置およびその製造方法を提供する。

【解決手段】 半導体基板と、前記半導体基板上に形成された絶縁膜と、前記絶縁膜内に形成された配線とを有し、前記絶縁膜は、前記配線の直下に位置する第1の絶縁膜と、その他の部分に位置する第2の絶縁膜から構成され、前記第1の絶縁膜は、前記第2の絶縁膜との境界面に位置する表層の炭素濃度が前記第1の絶縁膜の内部の炭素濃度よりも高いことを特徴とする半導体装置を提供する。

(もっと読む)

平板表示装置と平板表示装置の製造方法

【課題】データ配線と透明電極層間の接触構造を改善した平板表示装置を提供する。

【解決手段】平板表示装置は、絶縁基板と、絶縁基板上に形成されているデータ配線と、データ配線上にデータ配線を露出させる第1接触口を有する層間絶縁膜と、第1接触口の少なくとも一部とその周辺の層間絶縁膜上に形成されている連結部材と、連結部材上に形成されて連結部材を露出させる第2接触口を有するゲート絶縁膜及びゲート絶縁膜上に形成されている有機半導体層を含む。

(もっと読む)

半導体集積回路装置の製造方法

【課題】配線と配線を接続する接続部のバリア膜の構造を最適化し、エレクトロマイグレーション特性を向上させる。

【解決手段】半導体基板上の第1層配線M1上に形成された層間絶縁膜TH2中に配線溝HM2およびコンタクトホールC2を形成した後、これらの内部にバリア膜PM2aを、コンタクトホールC2の底部の全周に渡ってコンタクトホールC2の底部の中央部から側壁に向かってその膜厚が増加するよう形成し、このバリア膜PM2a上に銅膜(PM2b、PM2c)を形成した後、CMP法により研磨することにより第2層配線M2と接続部(プラグ)P2を形成する。その結果、接続部(プラグ)P2を介して第2層配線M2から第1層配線M1へ流れる電流の幾何学的な最短経路と、電気的に抵抗が最小となるバリア膜PM2aの薄い部分が一致せず、電流経路を分散することができ、電子の集中を起こりにくくできる。

(もっと読む)

電子基板の製造方法、電子基板および電子機器

【課題】 トロイダルインダクタ40を簡単に製造することが可能な半導体チップ1の製造方法を提供する。

【解決手段】 半導体チップ1上に第1配線12を形成する工程と、その第1配線12を覆うように応力緩和層30を形成する工程と、その応力緩和層30に貫通孔33,34を穿設して第1配線12の端部を露出させる工程と、その第1配線12の端部から貫通孔33,34を通り応力緩和層30の表面にかけて第2配線22を形成することにより、第1配線12および第2配線22を巻き線とし応力緩和層30をコア42とするトロイダルインダクタ40を形成する工程と、を有する。

(もっと読む)

集積回路装置、集積回路装置の作製方法

【課題】薄膜回路の下方に外部と接続するための電極を容易に形成できる薄膜回路部品の構造及び薄膜回路部品の作製方法を提供することを課題とする。

【解決手段】第1の絶縁膜と、第1の絶縁膜の一方の面上に形成された薄膜回路と、薄膜回路上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された電極と、電極上に形成された樹脂膜とを有する積層物を形成し、積層物の第1の絶縁膜の他方の面側に、電極と重なるように導電膜を形成し、導電膜にレーザーを照射する。

(もっと読む)

電子部品とその製造方法

【課題】高信頼性の電子部品の製造方法と、互いに接近した配置が可能な電子部品を提供する。

【解決手段】半導体基板(10、10′)に回路を形成するためのCMOS構造(20、20′)を形成し、CMOS構造(20、20′)の形成後、低温処理、特に450℃以下の温度での処理で、半導体基板(10、10′)の第1面(S1)とそれとは反対側の第2面(S2)との間で回路の接続を行うべく、半導体基板(10、10′)の開口内に少なくとも1つの電気導体(30、30′)を形成する。この電子部品は電子回路及びセンサ(80、80′)の狭小な配置を可能とし、特に医療機器用として適する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ヘテロ接合半導体素子と別の半導体素子とが同一基板上に集積され、かつ、この別の半導体素子の電極取り出し構造が改良された半導体装置及びその製造方法を提供すること。

【解決手段】 前記別の半導体素子の一例である抵抗素子20を構成する抵抗層11を、イオン注入法または不純物拡散法によって半絶縁性基板1内に形成する。次に、サブコレクタ層2、コレクタ層3、ベース層4、エミッタ層5、そしてエミッタキャップ層6の構成材料層を、基板1の全面にエピタキシャル成長法によって形成する。次に、これらの一部をメサ構造に加工して、HBT10を形成する。一方、抵抗素子20の素子電極14、15を高い位置で取り出すための導電層12、13を、サブコレクタ層2の構成材料層42のパターニングによって形成し、素子電極14、15をこの上に形成する。次に、BCBなどの平坦化膜30を形成し、これを介して配線31、32を形成する。

(もっと読む)

線路デバイスの製造方法

【課題】ストレスリリーフと接触窓構造の間隔距離の微小化を可能にする線路デバイス構造の製作過程及びその構造を提供する。

【解決手段】基板と、第一金属柱体68と、第二金属柱体と、を備え、第一金属柱体68は、基板上に位置し、第一金属柱体68の最大横寸法Hwを第一金属柱体68の高度Htで割ると4より小さく、かつ第一金属柱体68の高度が20μmから300μmの間であって、第二金属柱体は、基板上に位置し、第二金属柱体の最大横寸法を第二金属柱体の高度で割ると4より小さく、かつ第一金属柱体の中心点から第二金属柱体の中心点までの距離Hbが10μmから250μmの間である。

(もっと読む)

301 - 320 / 399

[ Back to top ]