Fターム[5F033KK25]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | シリサイド (1,324)

Fターム[5F033KK25]の下位に属するFターム

高融点金属のシリサイド (608)

Fターム[5F033KK25]に分類される特許

701 - 716 / 716

応力制御を伴う窒化シリコン膜

アセンブリは、互いに重ねて形成された窒化物エッチストップ層を有する多層窒化物スタックを備え、これら窒化物エッチストップ層の各々は、膜形成プロセスを使用して形成される。多層窒化物スタックを形成する方法は、単一ウエハ堆積チャンバに基板を配置し、堆積の直前に基板に熱的ショックを与えることを含む。第1の窒化物エッチストップ層が基板上に堆積される。第2の窒化物エッチストップ層が第1の窒化物エッチストップ層上に堆積される。 (もっと読む)

高融点金属シリサイド膜の製造方法、半導体装置の製造方法

【課題】高融点金属シリサイド膜を適切に形成することができる高融点金属シリサイド膜の製造方法を提供すること。

【解決手段】本発明の高融点金属シリサイド膜の製造方法は、シリコンを含む半導体基板1上に高融点金属膜9を形成する工程と、形成された高融点金属膜9の表面を非晶質化する工程と、非晶質化された高融点金属膜10上に窒化チタン膜11を形成する工程と、得られた基板を熱処理することにより高融点金属シリサイド膜12を形成する工程を備える。

(もっと読む)

発光装置の作製方法

【課題】 発光装置、特に発光装置が有する画素部の高精細化、高開口率化が進むにつれて、より幅の小さい配線を形成することが要求されている。しかしインクジェット法を用いて配線を形成する場合、配線形成表面でドットが広がってしまい、配線の幅を小さくすることが難しかった。

【解決手段】 本発明は、配線形成表面に光触媒物質を形成し、該光触媒物質の光触媒活性を利用して配線を形成することを特徴とする発光装置の作製方法である。インクジェット法により、光触媒物質上に、溶媒に導電体が混入された組成物を吐出することにより、ドットの径より狭い、つまり幅の小さい配線を有する発光装置を提供することができる。

(もっと読む)

半導体装置の製造方法

【課題】 安定した低抵抗のシリサイド膜を形成する技術を提供する。

【解決手段】 半導体基板1上にゲート絶縁膜5を形成する工程、ゲート絶縁膜5上にシリコン膜7を形成する工程、シリコン膜7と半導体基板1との表面にBF2イオンおよびBイオンを注入し、pチャネル型MISトランジスタQpのゲート電極11pと高濃度n型半導体領域15からなるソース/ドレインとを形成する工程、ゲート電極11pの上部に第1コバルトシリサイド膜を形成し、ソース/ドレインの上部に第2コバルトシリサイド膜を形成する工程を有する。

(もっと読む)

半導体装置

【課題】パッド部に流れる過電流が抑制されてパッド部におけるESD耐性が向上された半導体装置を提供する。

【解決手段】基板2上に第1の電位が与えられた第1のパッド8と、パッド8に電気的に接続された第1の導電層5が設けられている。基板2との間に少なくとも1層の第1の導電層5を挟んで第1の電位とは異なる第2の電位が与えられている第2のパッド13が設けられているとともに、少なくとも1層の第2の導電層10がパッド13に電気的に接続されてパッド8,13と基板2との間に設けられている。基板2上には、複数層の絶縁層4が積層されて設けられている。各絶縁層4は、パッド8および導電層5の少なくとも一方とパッド13および導電層10の少なくとも一方との間で容量絶縁膜となる。

(もっと読む)

測定で求めた電気的特性に基づいて製造プロセスを制御するための方法および装置

本発明の方法は、動作レシピに従って半導体デバイスの構造を形成するプロセスを少なくとも1つ実行するステップを有する。この構造の電気的性能特性が測定される。測定で求めた電気的性能特性とその電気的性能特性の目標値とが比較される。この比較に基づいて、操作レシピの少なくとも1つのパラメータが決定される。システム(10,100)は、プロセス装置(30〜80,200,210,220,230)、計測装置(30〜80,250)およびコントローラ(140)を備える。プロセス装置(30〜80,200,210,220,230)は、操作レシピに従って半導体デバイスの構造を形成するプロセスを少なくとも1つ実行するように構成されている。計測装置(30〜80,250)は、構造の電気的性能特性を測定するように構成されている。コントローラ(140)は、測定で求めた電気的性能特性とその電気的性能特性の目標値とを比較して、この比較に基づいて操作レシピの少なくとも1つのパラメータを決定するように構成されている。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の小型化を可能にする。

【解決手段】 基板21上のエピタキシャル層22に、ゲート電極32と、n-型オフセットドレイン領域35、n型オフセットドレイン領域39およびn+型ドレイン領域42からなるドレイン領域と、n-型ソース領域36およびn+型ソース領域43からなるソース領域とを有するLDMOSFEを形成するとともに、n型ウエル27上に複数のショットキ電極52を形成してショットキ電極52およびn型ウエル27間にショットキ接合を形成することでショットキダイオード素子を形成している。複数のショットキ電極52はプラグ63およびアノード電極74を介して互いに電気的に接続されている。複数のショットキ接合部の間および両側に設けられたn+型半導体領域44は、プラグ63およびカソード電極73を介して互いに電気的に接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 第1層配線と、拡散層あるいはゲート電極との層間容量を抑えつつ、拡散層あるいはゲート電極に確実に接続するコンタクトプラグを形成する。

【解決手段】 基板上方に形成されたゲート電極と、ゲート電極の両側に形成された拡散層とを有する半導体装置において、一端において、ゲート電極の上面に接し、かつ、他端が、ゲート電極上面よりも、基板に近い位置に伸びる導電体膜を形成する。そして、基板上に、ゲート電極と、導電体膜とを埋め込む層間絶縁膜を形成し、この層間絶縁膜を貫通し、導電体膜の、ゲート電極上面よりも基板に近い位置において、導電体膜に接続する第プラグを形成する。

(もっと読む)

半導体装置

【課題】 バイポーラトランジスタにおける高利得化および低雑音化を同時に実現できる技術を提供する。

【解決手段】 ベースパッド31およびコレクタパッド32の下部にエミッタ(基準(接地)電位)と電気的に接続された配線24が設けられた基板シールド構造とすることにより、ベースパッド31およびコレクタパッド32と配線24との間では容量が設けられた構造として電力消費をなくし、基板1からの熱雑音は、配線24を介して基準(接地)電位へと逃がし、ベースパッド31およびコレクタパッド32へは届かないようにする。

(もっと読む)

半導体基板及びその製造方法

【課題】表面上に引っ張り応力を有する層間絶縁膜等の絶縁膜が形成された半導体基板において、反りを抑制しうる半導体基板及びその製造方法を提供する。

【解決手段】シリコンウェーハ10と、シリコンウェーハ10の表面上に形成された層間絶縁膜に埋め込まれた多層配線12と、シリコンウェーハ10の裏面に形成され、引っ張り応力を有する絶縁膜であるシリコン窒化膜16bとを有している。シリコン窒化膜16bにより、多層配線12が埋め込まれた層間絶縁膜によりシリコンウェーハ10に与えられる応力が緩和され、シリコンウェーハ10の反りが抑制される。したがって、半導体基板の搬送系における吸着不良の発生を防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】静電破壊耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極とドレイン領域とソース領域とを有する半導体装置であって、ドレイン領域は、ゲート電極の第1の側に形成された第1導電型の第1の不純物拡散領域18aと;第1の不純物拡散領域より深く形成された第1導電型の第2の不純物拡散領域20aと;第1の不純物拡散領域より浅く形成され、不純物拡散層より不純物濃度が高い第1導電型の第3の不純物拡散領域28a、28bと;第3の不純物拡散領域上に形成され、ドレインコンタクト部22Dに接続されるシリサイド膜32a、32bとを有し、ドレインコンタクト部とサイドウォール絶縁膜との間にシリサイド膜が形成されていない領域が存在しており、ドレインコンタクト部の下方の半導体基板内に第2の不純物拡散領域が形成されていない。

(もっと読む)

PMD層の限定された熱履歴の形成

基板上に持ち上がった隣接特徴部により画成されたギャップを充填する方法は、基板を収容するチャンバにシリコン含有プロセスガス流を供給するステップと、上記チャンバに酸化プロセスガス流を供給するステップと、上記チャンバに燐含有プロセスガス流を供給するステップとを備えている。また、この方法は、シリコン含有プロセスガスと、燐含有プロセスガスと、酸化プロセスガスとの間に反応を生じさせることにより、Pドープの酸化シリコン膜の第1部分を実質的な適合層としてギャップに堆積するステップも備えている。適合層の堆積は、(シリコン含有プロセスガス+燐含有プロセスガス):(酸化プロセスガス)の比を時間と共に変化させる段階と、適合層の堆積全体にわたり基板の温度を約500℃未満に維持する段階とを含む。また、この方法は、Pドープの酸化シリコン膜の第2部分をバルク層として堆積するステップも備えている。上記膜の第2部分の堆積は、(シリコン含有プロセスガス+燐含有プロセスガス):(酸化プロセスガス)の比をバルク層の堆積全体にわたり実質的に一定に維持する段階と、バルク層の堆積全体にわたり基板の温度を約500℃未満に維持する段階とを含む。 (もっと読む)

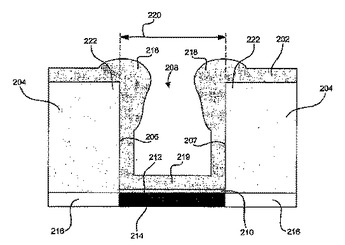

コンタクトの形成中、コンタクトホール幅の増大を防ぐ方法

一形態によれば、半導体ダイに位置するシリサイド層(214)上にコンタクトを形成する方法は、コンタクトホール(208)の各側壁(206、207)、及び、コンタクトホール(208)の底部に位置する自然酸化物層(210)に、バリア層(202)を堆積するステップを含み、各側壁(206、207)は、絶縁層(204)のコンタクトホールによって形成される。コンタクトホール(208)の各側壁(206、207)、及び、酸化物層(210)にバリア層(202)を堆積する(150)ステップにおいて、バリア層(202)の厚さを、コンタクトホール(208)の上部が、コンタクトホール(208)の底部よりも厚くなるよう最適化してもよい。この形態によれば、バリア層(202)の一部分(219)及びコンタクトホール(208)の底部に位置する酸化物層(210)を除去し、シリサイド層(214)を露出させるステップを含む方法も提供される。  (もっと読む)

(もっと読む)

基板上に多機能誘電体層を形成する方法

本発明は、多機能誘電体層を基板上、特に基板上に露出している金属配線系上に形成する方法に関する。本発明の目的は、銅による配線を形成するための多機能パッシベーション層を容易に形成する方法を提供するとともに、エレクトロマイグレーション、ストレスマイグレーション、および接着性を向上させる方法を提供することにある。本発明によれば、更なる金属層(5)を、露出した金属配線(3)の表面上に堆積することによって、本発明の目的は達せられる。この金属層は少なくともその一部が非導電性の金属酸化物に変換され、誘電体層となっている。  (もっと読む)

(もっと読む)

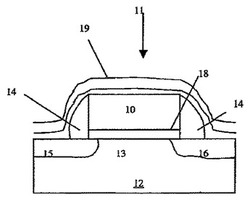

集積回路技術における超均一シリサイド

集積回路(100)の形成方法(900)およびその構造体が提供される。半導体基板(102)上にゲート誘電体(104)が形成され、半導体基板(102)上のゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(504/506)が形成される。ソース/ドレイン接合部(504/506)上に超均一シリサイド(604/608)が形成され、半導体基板(102)の上方に誘電体層(702)が堆積される。次いで、誘電体層(702)に、超均一シリサイド(604/608/606)へのコンタクトが形成される。  (もっと読む)

(もっと読む)

半導体装置

【課題】ESD 保護回路のサージ電流経路に使用される配線層に生じる熱を効率よく放熱でき、サージ電流経路に使用される配線層も保護する。

【解決手段】外部端子と内部回路との間の配線に接続され、外部端子に印加された過大な静電サージ入力から内部回路を保護する保護素子を有する入力保護回路と、入力保護回路に接続され、そのサージ電流経路に含まれる第1のメタル配線層25と、第1のメタル配線層に連なり、熱伝導性が良好な材質の配線を用いてなる放熱器20とを具備する。

(もっと読む)

701 - 716 / 716

[ Back to top ]