Fターム[5F033NN08]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 深さの異なる複数のコンタクトホールの穴埋め (88)

Fターム[5F033NN08]に分類される特許

81 - 88 / 88

半導体装置の製造方法および半導体装置

【課題】 微小開口の孔の形成が容易で、断線が発生しにくく、且つオーバーエッチングによる電極等の再付着現象を発生させないようにする。

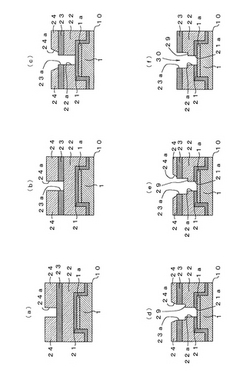

【解決手段】 有機系の第2の絶縁層22を珪素系の第1の絶縁層21と第3の絶縁層23で挟んで絶縁膜20を形成し、その絶縁膜に対して、異方性エッチングと異方性の強いエッチングを交互に繰り返すことにより、第2の絶縁層22部分に段部29を有し、基板側に向かって凸型の孔30を形成し、回路素子1の電極1aと絶縁膜表面との間を接続する配線部として蒸着される導電材が、段部29に堆積する導電材を介して一体化するようにしている。

(もっと読む)

半導体装置、DRAM集積回路装置およびその製造方法

多層配線構造を有する半導体装置は、第1の導電領域と、前記基板に対して前記第1の導電領域よりも高い位置に上面を有する第2の導電領域と、前記第1および第2の導電領域を覆う絶縁膜と、前記絶縁膜中に、前記第2の導電領域を露出するように形成された配線溝と、前記絶縁膜中に前記第1の導電領域を露出するように形成されたコンタクトホールと、前記配線溝および前記コンタクトホールを充填する配線パターンとよりなり、前記配線パターンの上面は、前記絶縁膜の上面に一致する。  (もっと読む)

(もっと読む)

混載型メモリ装置及びその製造方法

【課題】電気的特性に優れた、より高性能な混載型メモリ装置及びその製造方法。

【解決手段】混載型メモリ装置100は、強誘電体層44を含む複数のメモリセルがマトリクス状に設けられているメモリセルアレイ領域1、ロジック回路素子20が設けられているロジック回路領域2を含む複数の領域を有していて、メモリセルアレイ領域を除く領域を覆って設けられているライナー酸化膜80と、ライナー酸化膜が設けられている領域とメモリセルアレイ領域とにわたって設けられているカバー膜90とを具えている。

(もっと読む)

半導体装置およびその製造方法

【課題】低電気抵抗化および高信頼性化可能なコンタクトを備え、高速伝送が可能で信頼性の高い半導体装置およびその製造方法を提供する。

【解決手段】 コンタクト20、23を、CVD法を用いて、シリサイド膜19、22、シリコン窒化膜15aおよび第1層間絶縁膜15bの内壁に接する表面に、表面からコンタクト内部方向への距離に応じて窒素含有量が減少する組成勾配を有する窒化タングステン部24を形成し、その内側にタングステンが充填されたタングステン部25を形成する。窒化タングステン部24とタングステン部25との界面の酸化や汚染を防止する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】 ヴィア(ヴィアコンタクト)の加工形状を均一にすることを目的とする。

【構成】 第1の配線層と、前記第1の配線層の上方に形成された第2の配線層と、前記第1の配線層と前記第2の配線層との間のヴィア層に配置され、前記第2の配線層下面から前記第1の配線層上面まで導電性材料が堆積したヴィア20と、前記第1の配線層と前記第2の配線層との間のヴィア層に配置され、前記第2の配線層下面から前記ヴィア層の途中まで導電性材料が堆積した、前記ヴィア20より径の小さなヴィア22と、を備えたことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】多層配線の狭ピッチ化に対応可能な半導体装置およびその製造方法を得る。

【解決手段】半導体基板上に複数の第1配線層を形成する工程と、第1配線層を覆うように第1層間絶縁膜層9を形成する工程と、第1層間絶縁膜層に、表面からその厚み方向に貫いて第1配線層に接続する複数の第1プラグ14を形成する工程と、第1層間絶縁層上であって、第1プラグのうち一部の第1プラグの直上部に第2配線層40を形成する工程と、第1層間絶縁膜層上に第2配線層を覆うように第2層間絶縁膜層19を形成する工程と、第2層間絶縁膜層に、表面からその厚み方向に貫いて第2配線層に接続する第2プラグ24’と、表面からその厚み方向に貫いて第1プラグに直接接続する第3プラグ24と、を同時に形成する工程と、第2層間絶縁膜層上であって、第2プラグおよび第3プラグの直上部に第3配線層50を形成する工程と、を含む。

(もっと読む)

半導体装置の配線構造体及びその形成方法

【課題】 半導体装置の配線構造体およびその形成方法を提供する。

【解決手段】 この半導体装置は半導体基板100上に配置された層間絶縁膜、前記層間絶縁膜を貫通する第1コンタクト構造体181および第2コンタクト構造体182、前記層間絶縁膜上に配置されて前記第1コンタクト構造体と前記第2コンタクト構造体に連結される金属配線220を具備する。この際、前記第1コンタクト構造体は順次に積層された第1プラグおよび第2プラグ200を含み、前記第2コンタクト構造体は前記第2プラグを含む。

(もっと読む)

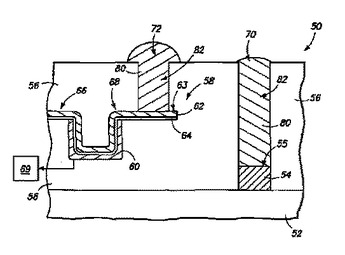

電気的接続部を形成する半導体処理方法及び半導体構造

無電解メッキを利用して、半導体基板に関連する電気的相互接続部を形成することができる。例えば、半導体基板は、その上に無電解メッキに適する表面を持つダミー構造を有するように、且つその上にダミー構造とほぼ同じ高さを有するディジット線を有するように形成することができる。層はダミー構造及びディジット線上に形成され、開口はその層を通ってダミー構造及びディジット線の上部表面まで形成される。続いて、導電性材料が開口内に無電解メッキされて、開口内に電気的接続部を形成することができる。ダミー構造まで延びる開口はキャパシタ電極を通ることができ、したがって、そのような開口内に形成される導電性材料を利用して、キャパシタ電極への電気的接続部を形成することができる。  (もっと読む)

(もっと読む)

81 - 88 / 88

[ Back to top ]